-

Xilinx MIPI CSI-2 Receiver Subsystem IP详解

目录

1.MIPI CSI-2 Receiver Subsystem IP架构

4.3 MIPI CSI-2 RX Controller延迟

1.MIPI CSI-2 Receiver Subsystem IP架构

2.MIPI CSI-2 Receiver 核心详细信息

2.1 MIPI D-PHY

说白了就是实现了MIPI的物理接口层。MIPI D-PHY实现了一个D-PHY RX接口,并提供了与CSI-2兼容的物理协议层支持。当链路速率大于1.5Gb/s时,MIPI D-PHY 支持抖动模式检测。可以看PG202了解更多信息。

MIPI D-PHY讲解

https://blog.csdn.net/weiaipan1314/article/details/125756016?spm=1001.2014.3001.5501

https://blog.csdn.net/weiaipan1314/article/details/125756016?spm=1001.2014.3001.55012.2 MIPI CSI-2 RX Controller

MIPI CSI-2 RX控制器由MIPI CSI-2 RX1.1规范中定义的多个层级组成,如通道管理层、LLP层、字节到像素转换层,说白了就是实现了MIPI的CSI-2协议。

MIPI CSI-2 RX控制器核心通过PPI从MIPI D-PHY核心接收每个通道的8位数据,最多支持4个通道。如下图所示,PPI(Physical protocol interface)上接收的字节数据随后由低层协议模块处理,以提取真实图像信息。最终提取的图像使用AXI4流协议提供给用户/处理器界面。通道管理块始终在从PPI接收的32位数据上运行,与通道数无关。

(1)1-4车道支持,寄存器支持选择多个通道;

(2)支持所有短包和长包;

(3)支持主要和多种次要的视频格式;

(4)数据类型(DT)交错;

(5)虚拟通道标识符(VC)交错;

(6)数据类型和虚拟通道交错;

(7)包头1bit的错误纠正码和2bit的错误检测;

(8)数据负载支持CRC效验;

(9)针对下游IPs的长包ECC/CRC转发能力;

(10)单lane支持最大2.5Gb/s的数据速率;

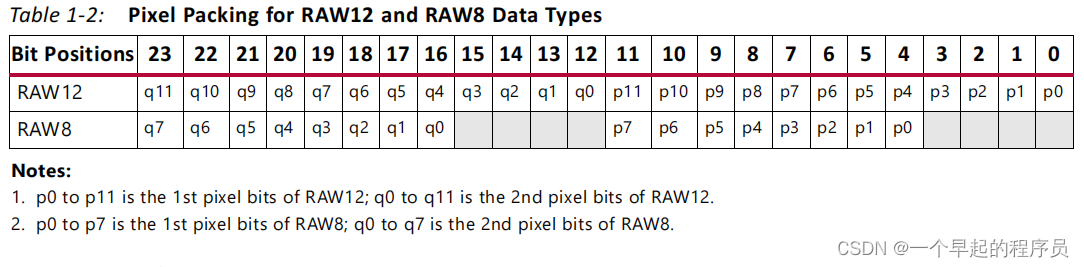

(11)基于数据格式的像素字节打包;

(12)AXI4-Lite接口访问核心寄存器;

(13)低功耗状态检测;

(14)错误检测(D-PHY级别错误、数据包级别错误、协议解码级别错误);

(15)提供中断支持,支持内部状态和错误信息;

如表下图所示,嵌入式非图像(数据类型代码为0x12)AXI4流接口数据宽度是根据所选的数据类型选择的。嵌入式非图像AXI4-流接口的宽度随着IP核所选的数据类型宽度可能不通。

2.3 ECC/CRC Forwarding

AXI4流接口的边带信号[包括/不包括视频格式网桥和嵌入式非图像接口]将从源[传感器]接收的ECC和CRC数据报告给下游IP。这允许下游IP在某些功能安全应用中重新计算ECC/CRC。

在错误场景中,如由于软重置而突然终止、在数据包传输过程中禁用核心、线路缓冲区处于满状态、接收数据包的字数大于实际有效负载,这些边带信号不会报告正确的ECC和CRC。

2.4 VCX Support

MIPI CSI-2标准v2.0特定VCX支持功能用于将可用虚拟通道的最大数量扩展到16个。启用此功能后,通过组合来自数据包标头的2位VC字段(LSB)和2位VCX字段(MSB)来推导虚拟通道。

2.5 AXI Crossbar

子系统中使用AXI Crossbar核根据地址将AXI4 Lite请求路由到相应的子核。

2.6 Video Format Bridge

视频格式桥接器核心使用用户选择的VC和数据类型信息,仅过滤出所需的AXI4流数据拍。该AXI4流数据基于数据类型信息进行进一步处理,输出基于每拍请求的像素数。

视频格式桥接核心处理在Vivado集成设计环境(IDE)中选择的数据类型,并过滤掉从CSI-2 RX控制器接收到的基于RAW8和基于用户定义数据类型(0x30-0x37)之外的所有其他数据类型。

不管Vivado IDE的选择如何,RAW8和基于用户定义的数据类型总是由视频格式桥核心处理。这允许多种数据类型支持,像素数据支持来自Vivado IDE的一种主要数据类型,元数据支持基于用户定义的基于字节的数据类型。当传输多个数据类型时(例如,RAW10和基于用户定义数据类型)时,真正的像素数据在AXI4流中被定义。

对于未对齐的传输,无法根据TKEEP信号为输出接口指定部分最终输出。

2.6.1 视频输出端口宽度

video_out接口中数据端口的宽度取决于所选的数据类型和所选的每拍像素数。宽度是RAW8和Vivado IDE中选择的数据类型乘以每拍像素数的最大值。然后根据AXI4流协议将其舍入到最近的字节边界。

举例1:选择RAW10、每个时钟输出2个像素

- Single pixel width of RAW10 = 10bit

- Single pixel width of RAW8 = 8bit

对于每个时钟选择的两个像素,RAW10和RAW8的有效像素宽度分别为20和16。视频输出端口宽度配置为单个像素宽度的最大值,并舍入到最近的字节边界。这导致视频输出端口宽度为24。

举例2:选择RAW7、每个时钟输出4个像素

- Single pixel width of RAW7 = 7bit

- Single pixel width of RAW8 = 8bit

对于每个时钟选择的两个像素,RAW7和RAW8的有效像素宽度分别为28和32。视频输出端口宽度配置为单个像素宽度的最大值,并舍入到最近的字节边界。这导致视频输出端口宽度为32。

2.6.2 多种数据类型的像素打包

当以不同像素宽度传输多个像素时,宽度较低的像素对正到最高有效位。

2.6.3 嵌入式非图像数据类型的像素打包

2.6.3 嵌入式非图像数据类型的像素打包AXI4流TDATA宽度基于从Vivado®IDE中选择的主要数据类型。这个列出了嵌入的非图像数据类型字节在emb_nonimg_tdata上的位置。

2.6.4 视频格式桥不存在时的像素打包

视频输出中数据端口的宽度可以从Vivado IDE中的CSI-2选项TDATA width下选择。当不存在视频格式桥接器时,MIPI CSI-2接收子系统遵循MIPI CSI-2规范的推荐内存存储格式输出像素,这个时候就需要查看mipi CSI-2的规范文档。

不同数据类型举例如下:

2.7 AXI IIC

2.7 AXI IIC MIPI CSI-2规范的摄像机控制接口(CCI)与具有400 kHz操作和7位从寻址的I2C接口的快速模式变体兼容。根据用户选择,AXI IIC可作为该子系统的一部分。

3. MIPI CSI-2 RX应用

Xilinx MIPI CSI-2 RX控制器在摄像机传感器和执行基带处理的可编程设备之间实现摄像机串行接口。由于高分辨率摄像机的发展,摄像机-传感器接口的带宽需求增加。传统的并行接口需要越来越多的信号线,从而导致更高的功耗。新的高速串行接口,如MIPI CSI规范,可以在不牺牲功耗的情况下满足这些不断扩展的带宽要求。MIPI是移动产业集团定义的一组协议,用于标准化移动平台(如手机和平板电脑)内的所有接口。然而,移动行业的巨大容量和规模经济迫使其他应用程序也采用这些标准。因此,基于MIPI的摄像机传感器正越来越多地应用于汽车应用中的驾驶员辅助技术、视频安全监控摄像机、视频会议以及虚拟现实和增强现实等新兴应用中。

4.性能

本节详细介绍了各种核心配置的性能信息。

4.1 CSI2 RX子系统延迟

CSI2 RX子系统核心延迟是从串行线路上的传输开始(SoT)行为到CSI-2 RX子系统输出的tvalid信号断言的时间。这包括D-PHY延迟、MIPI RX控制器延迟和VFB延迟(如果子系统中包括视频格式网桥)。

4.2 D-PHY延迟

MIPI D-PHY RX核心延迟是从串行线路上的传输开始(SoT)行为到PPI上的activehs信号断言的时间。HS_SETTLE 周期在D-PHY延迟计算中起着重要作用。下图提供了各种配置下D-PHY的延迟rxbyteclk时钟数。

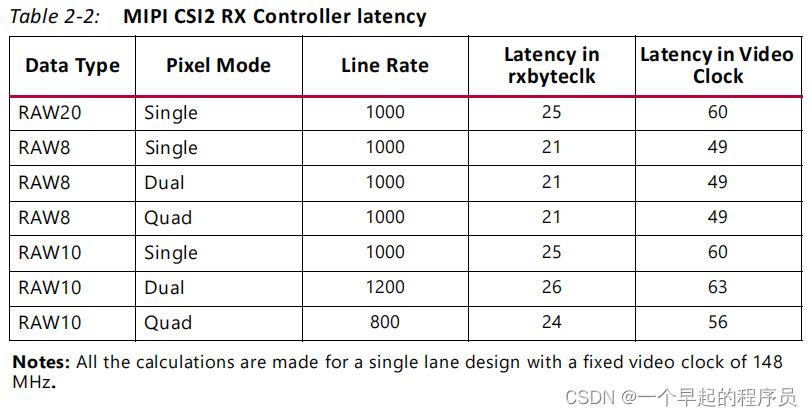

4.3 MIPI CSI-2 RX Controller延迟

MIPI CSI-2 RX控制器核延迟是从PPI接口上的activehs断言到控制器输出上的有效信号断言的时间。下图提供了各种配置下MIPI CSI-2 RX Controller的延迟rxbyteclk时钟数。

4.4 视频合适桥(VFB)延迟

VFB核心延迟是从VFB输入流接口“tvalid”到VFB输出流接口“tvalid”的时间。下图提供了各种配置下VFB的延迟rxbyteclk时钟数。

4.5 CSI2 RX子系统延迟时钟总数

通过增加链路通道数可以改善延迟时间。

5.接口

5.1 时钟和复位

dphy_clk_200M:D-PHY的时钟,必须为200MHz;

video_aclk:为子系统的所以核提供核心时钟,7系列最大为175MHz,UltraScale+最大为250MHz,此时钟频率应该大于等于lite_aclk时钟频率。

5.2 存在视频格式桥时的AXI4流视频接口

5.3 选择嵌入式非图像接口时的AXI4流接口

和5.2一致,只是时钟emb_nonimg_接口进行输出。

5.4 视频格式桥接器不存在时的AXI4流接口

和5.2一致。

5.5 其他接口

信号 输入输出 描述 csirxss_csi_irq输出 来自CSI-2 RX控制器的中断(高电平有效) csirxss_iic_irq输出 来自AXI IIC的中断(高电平有效) mipi_dphy_if输入 DPHY接口 rxbyteclkhs输出 PPI高速接收字节时钟 dlyctrl_rdy_out输出 IDEALYCTRL的就绪信号输出,延迟值根据vtc变化进行调整 6.寄存器空间

通过axi_lite接口可以访问MIPI CSI-2 RX控制器、IIC控制器、MIPI D-PHY所有内部核心组件。

当AXI IIC核心不存在时,MIPI D-PHY偏移向上移动并从0x1_0000开始。软件驱动程序可以无缝地处理这个问题。

1.本文部分素材来源网络,版权归原作者所有,如涉及作品版权问题,请与我联系删除。

2.未经原作者允许不得转载本文内容,否则将视为侵权;

3.转载或者引用本文内容请注明来源及原作者;

4.对于不遵守此声明或者其他违法使用本文内容者,本人依法保留追究权等。

下面是我的个人微信公众号,关注【一个早起的程序员】精彩系列文章每天不断。

-

相关阅读:

PostMan传时间参数&一次性发送多次请求

企业网上订货系统的定义与组成|手机APP订单管理软件

JavaScript设计模式中的单一职责原则

39. 组合总和

查看python第三方库的依赖

【笔试强训选择题】Day43.习题(错题)解析

两个点的距离

医学大数据|R|竞争风险模型:可视化与图像优化

NumPy数组基础

从根上理解Mybatis的一级、二级缓存

- 原文地址:https://blog.csdn.net/weiaipan1314/article/details/125885546