-

JESD204B时钟网络

本文为明德扬原创文章,转载请注明出处!

明德扬的JESD204B采集卡项目综合上板后,可以使用上位机通过千兆网来配置AD9144和AD9516板卡,实现高速ad采集。最终可以在示波器和上位机上采集到设定频率的正弦波。本文重点介绍JESD204B时钟网络。

一,JESD204B时钟网络原理概述

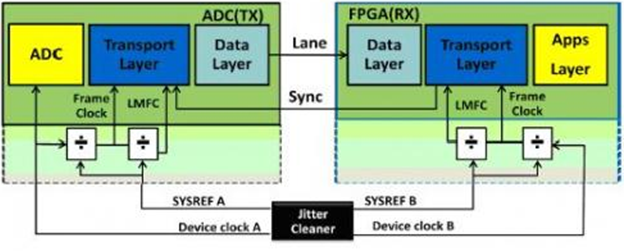

本文以JESD204B subclass1来讨论时钟的时序需要以及TI时钟芯片方案的实现。任何一个串行协议都离不开帧和同步,JESD204B也不例外,也需要收发双方有相同的帧结构,然后以一种方式来同步,即辨别起始。JESD204B是以时钟信号的沿来辨别同步的开始,以及通过一定的握手信号使得收发双方能够正确识别帧的长度和边界,因此时钟信号及其时序关系对于JESD204B就显得极其重要。下图是典型的JESD204B系统的系统连接:

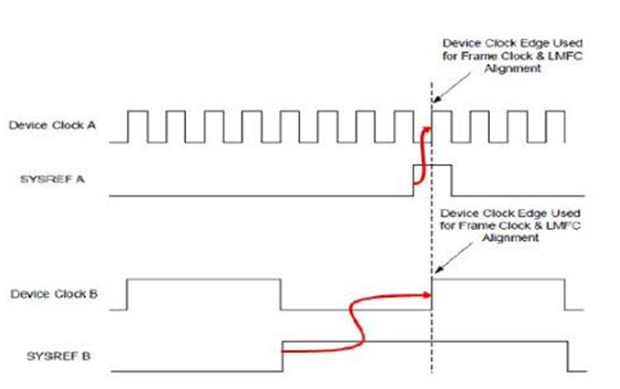

Device Clock是器件工作的主时钟,一般在数模转换器里为其采样时钟或者整数倍频的时钟,其协议本身的帧和多帧的时钟也是基于Device Clock.SYSREF是用于指示不同转换器或者逻辑的Device Clock的沿,或者不同器件间Deterministic latency的参考。如下图所示,Device Clock和SYSREF必须满足的时序关系。

SYSREF的第一个上升沿要非常容易的能被Device Clock捕捉到,这样就需要SYSREF和Device Clock满足上图的时序关系。通常会因为PCB的线长以及时钟器件不同通道输出时的Skew,会带来一定的误差,Device Clock的上升沿不一定正好在SYSREF的脉冲的正中间,工程上只要在一定范围内就能保证JESD204收发正常工作。

二,明德扬JESD204B项目时钟网络介绍

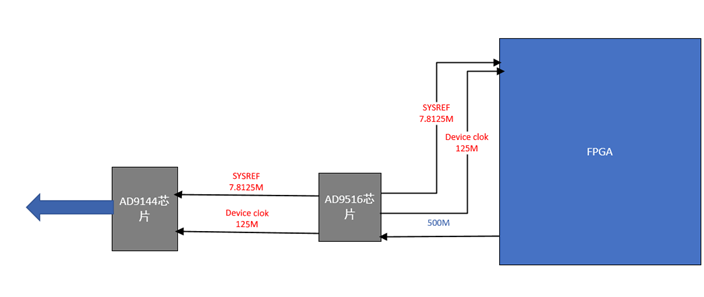

明德扬JESD204B采集卡项目使用Xilinx的KC705开发板,外接的DA板卡包含ad9144芯片和ad9516时钟芯片。

该项目由FPGA发送一个源时钟到ad9516芯片,接着由ad9516芯片输出4个时钟,其中2个时钟输送到FPGA,另外2个时钟输送到ad9144芯片。具体架构如下图:

AD9516介绍

AD9516,这是一个由ADI公司设计的14路输出时钟发生器,具有亚皮秒级抖动性能,还配有片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.55 GHz至2.95 GHz。或者,也可以使用最高2.4 GHz的外部VCO/VCXO。

AD9516有6路(3对)LVPECL输出,4路(2对)LVDS输出以及8路LVCMOS(每个LVDS可以作为2路LVCMOS)输出。每对之间共享数值为1-32的分频数值,因此,每对LVPECL或者LVDS输出的时钟频率是相同的。LVPECL输出可达1.6GHz,LVDS输出可达800MHz,LVCMOS可达250MHz。输入参考时钟频率和VCO工作频率有如关系: Fvco=(Fref/R)*(P*B+A)

每路输出还有单路的分频因子(1-32)可以配置,通过参考时钟的选择,内部P、B、A寄存器以及每路分频寄存器的配置,可以得到我们想要的时钟。

以上就是关于明德扬JESD204B的时钟网络的介绍,明德扬可承接基于JESD204B的高速数据传输项目,若想了解更多,感兴趣的同学可以留言相互讨论!

-

相关阅读:

一次线上故障:数据库连接池泄露后的思考

【Docker系列】Docker-核心概念/常用命令与项目部署实践

MySQL十种锁,一篇文章带你全解析

AST反混淆实战|某国外混淆框架一小段混淆js还原分析

一、认识STM32

rhcsa学习1基本命令(软硬链接,获取帮助等)

什么是 SRE?一文详解 SRE 运维体系

Shell脚本之awk的用法

基于微信小程序的在线测试系统

HCIA VLAN原理

- 原文地址:https://blog.csdn.net/MDYFPGA/article/details/125632767