-

野火FPGA入门(2):Verilog HDL基础语法

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog语言:

- 语法自有,易学易用

- 适合算法级、门级设计

- 代码简洁

- 发展较快

VHDL语言:

- 语法严谨,难以上手

- 适合系统级设计

- 代码冗长

- 发展缓慢

0 Verliog语言

- 模块开始结束:module、endmodule

- 输入输出:input、output、inout

- 线网型变量wire、寄存器型变量reg

- 参数parameter、localparam

常量表示格式:

[换算为二进制后位宽的总长度]['][数值进制符号][与数值进制符号对应的数值]

8'd171:位宽是8bit,十进制是171赋值方式:阻塞赋值(顺序进行)、非阻塞赋值(同时执行)

例:阻塞赋值a = 1; b = 2; c = 3; begin a = b; c = a; end- 1

- 2

- 3

- 4

- 5

- 6

- 7

a = 2; b = 2; c = 2;- 1

- 2

- 3

例:非阻塞赋值

a = 1; b = 2; c = 3; begin a <= b; c <= a; end- 1

- 2

- 3

- 4

- 5

- 6

- 7

a = 2; b = 2; c = 1;- 1

- 2

- 3

逻辑值

0:逻辑低电平,条件为假

1:逻辑高电平,条件为真

z:高阻态,无驱动

x:未知逻辑电平1 运算符

算数运算符

+(加法,如assign c = a+b;就是把a与b的和赋给c)

-(减法,如如assign c = a-b;就是把a与b的差赋给c)

*(乘法,如如assign c = a乘以3;结果赋给c)

/(除法,如如assign c = a/2;结果赋给c,一般不会用除号)

%(求模,或者称为求余,要求%两侧均位整形数据,5%3的值为2,用在测试文件)

归约运算符、按位运算符

作为一元运算符时:将所有比特相与

&4'b1111 = 1&1&1&1 = 1'b1 &4'b1101 = 1&1&0&1 = 1'b0- 1

- 2

作为二元运算符时:对应为相与

4'b1010&4'b0101 = 4'b0000 4'b1101&4'b1111 = 4'b1101- 1

- 2

其他操作符同理

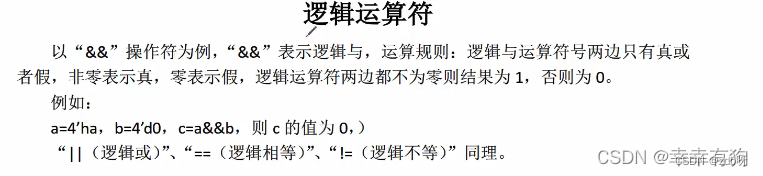

逻辑运算符

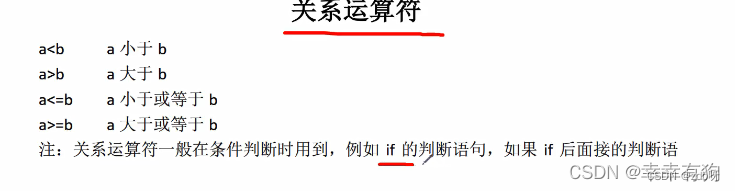

关系运算符

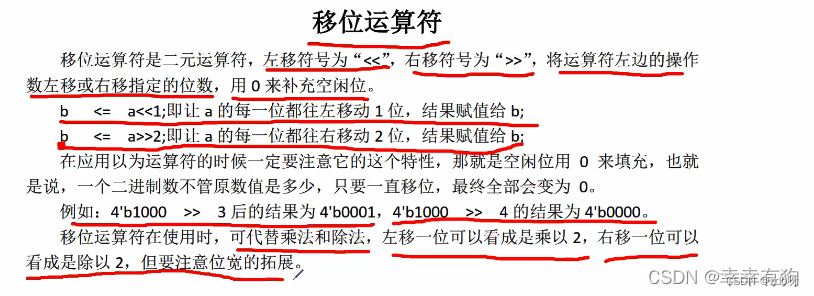

位移运算符

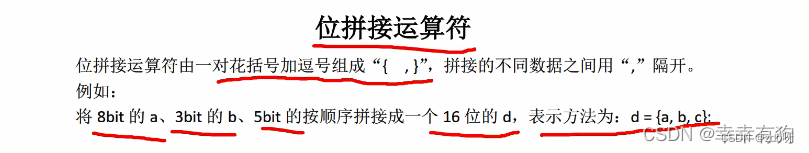

拼接运算符

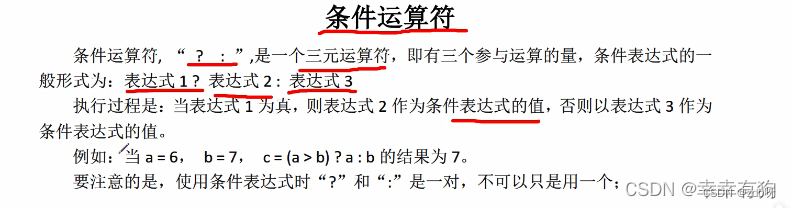

条件运算符

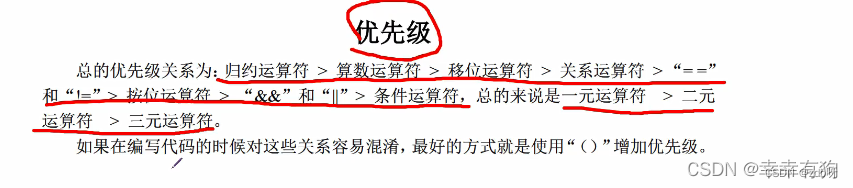

优先级

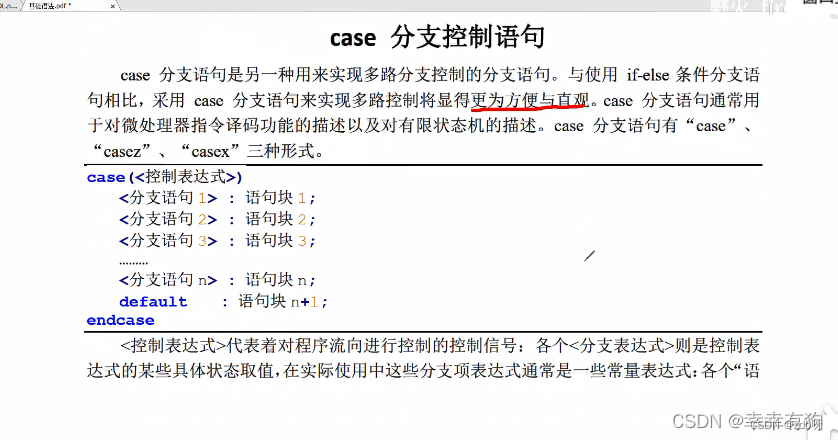

case分支语句

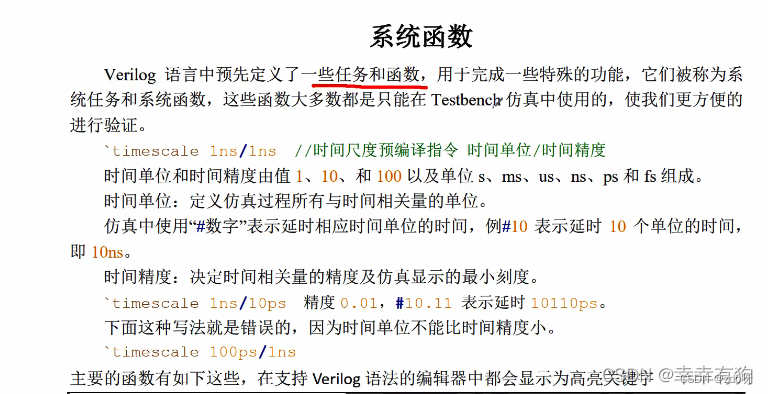

2 系统函数

常见系统函数:$display //打印信息,自动换行 $write //打印信息 $strobe //打印信息,自动换行,最后执行 $monitor //检测变量,变量发生变化就会执行这语句 $stop //暂停仿真 $finish //结束仿真 $time //时间函数 $random //随机函数 $readmemb //读文件函数- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

1、display

$display("%b+%b=%d",a,b,c); //%h,十六进制 //%d,十进制 //%o,八进制 //%b,二进制- 1

- 2

- 3

- 4

- 5

2、write

$write("%b+%b=%d\n",a,b,c); //不会自动换行- 1

参考博客

https://blog.csdn.net/yanyonglin123/article/details/123361964

-

相关阅读:

JavaWeb基础篇笔记(1)

清明作业 c++

手写一个线程池,带你学习ThreadPoolExecutor线程池实现原理

SpringBoot集成swagger

数据结构——查找

数字转型新动力,开源创新赋能数字经济高质量发展

Spectacle源码及分析3 —— Main.cpp解析2

ELK 使用 metricbeat监控数据

实用 - Java后端面试经历(经验分享)适用于2~3年

Qt5开发及实例V2.0-第一章Qt概述及Qt5的安装

- 原文地址:https://blog.csdn.net/qq_39236499/article/details/127752409