-

【UCIe】UCIe Sideband 介绍

🔥点击查看精选 UCIe 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/126960034】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

0. 缩写释义

- CfgRd - Configuration Read,配置读请求,CfgRd32/64 对应 32/64bit 配置读。

- CfgWr - Configuration Write,配置写请求,CfgWr32/64 对应 32/64bit 配置写。

- Cpl - Completion without Data,不带数据的完成事务。

- CplD - Completion with Data,带数据的完成事务。

- D2D - Die-to-Die。

- DDR - Double Data Rate,双倍数据速率。

- FDI - Flit-Aware Die-to-Die Interface。

- LSM - Link State Machine,链路状态机。

- MMIO - Memory-Mapped IO。

- MRd - Memory Read,内存读请求,MRd32/64 对应 32/64bit 内存读请求。

- MWr - Memory Write,内存写请求,MWr32/64 对应 32/64bit 内存写请求。

- Msg - Message, Message without Data,不带数据的消息。

- MsgD - Message with Data,带数据的消息。

- RDI - Raw Die-to-Die Interface。

- SB - Sideband,边带。

- SDR - Single Data Rate,单倍数据速率。

- UI - Unit Interval,单位间隔。

1. 基本介绍

UCIe 提供了两大数据通路:Mainband 及 Sideband。Mainband 用来传输业务数据流,Sideband 用来来处理一些 链路训练、链路管理、参数交换及寄存器访问 等非数据传输业务。Sideband 作为 Mainband 的 Back Channel,能够简化数据链路的建立过程、提升 Mainband 的带宽利用率、简化 Mainband 设计复杂度。

除了常规意义上的 Die 间 UCIe Link Sideband,UCIe 还有 FDI Sideband 及 RDI Sideband,在不同层次间传递边带信息。UCIe 支持类似于 PCIe 的 4 种数据包,包括配置读写、内存读写、Completion 及 Message。

2. Sideband 功能

UCIe Sideband 在 D2D 参数交换、链路训练、链路管理及寄存器访问方面发挥着不可或缺的作用,但无论是哪一方面,UCIe Sideband 做的只有两点:① 寄存器访问;② Message 传递。

2.1 寄存器访问

UCIe 是个分层协议,根据作用的不同,其寄存器也分布在协议层、Adapter、物理层等各个层次。通过 UCIe Sideband,实现同 Die 内不同层次间的直接寄存器访问,或跨 Die 的间接寄存器访问。

- Local Die 寄存器访问。同一 UCIe Die 内,上层通过 Sideband 访问下层寄存器,比如协议层访问 Adapter、物理层寄存器,比如 Adapter 访问物理层寄存器,都可以直接通过 FDI 或 RDI 上的 Sideband 接口实现寄存器访问。

- Remote Die 寄存器访问。不同 UCIe Die 间,Master Die 可以基于 Mailbox 机制,由 Adapter 发起 Sideband 寄存器访问操作,间接访问对端任何层次的 UCIe 相关寄存器。

2.2 Message 传递

UCIe 通过在 UCIe Layer 间或 Die 间的 Sideband 来传递相关 Message,从而实现参数交换、链路训练及链路管理。

- 链路训练。Sideband Message 传递贯穿整个 UCIe 链路训练过程(SBINIT->MBINIT->MBTRAIN->LINKINIT->ACTIVE)。

- 链路管理。UCIe 通过 Sideband Message 实现 PM、Retrain 等链路状态的管理。

- 参数交换。参数交换发生于链路初始化期间。Stage2 发生于 Sideband 初始化之后,Stage2 时在 UCIe 链路物理层之间通过 Sideband 交换训练参数,对 Mainband 进行训练。Stage3 时 Mainband 物理链路训练完毕,此时通过 Sideband 在 Adapter 之间交换协议参数 ,协商要采用的协议及 Flit 格式。

2.3 作用范围

采用 Sideband 进行寄存器访问及 Message 传递时,Sideband 消息在层与层之间、Die 与 Die 之间传递时并不是畅通无阻的,而是有一定“地域”限制的。比如,协议层可以通过 FDI Sideband 直接访问 Local Die Adapter 及物理层的寄存器,却不能直接访问对端 Die 上的 UCIe 寄存器,只能通过 Mailbox 机制来访问。

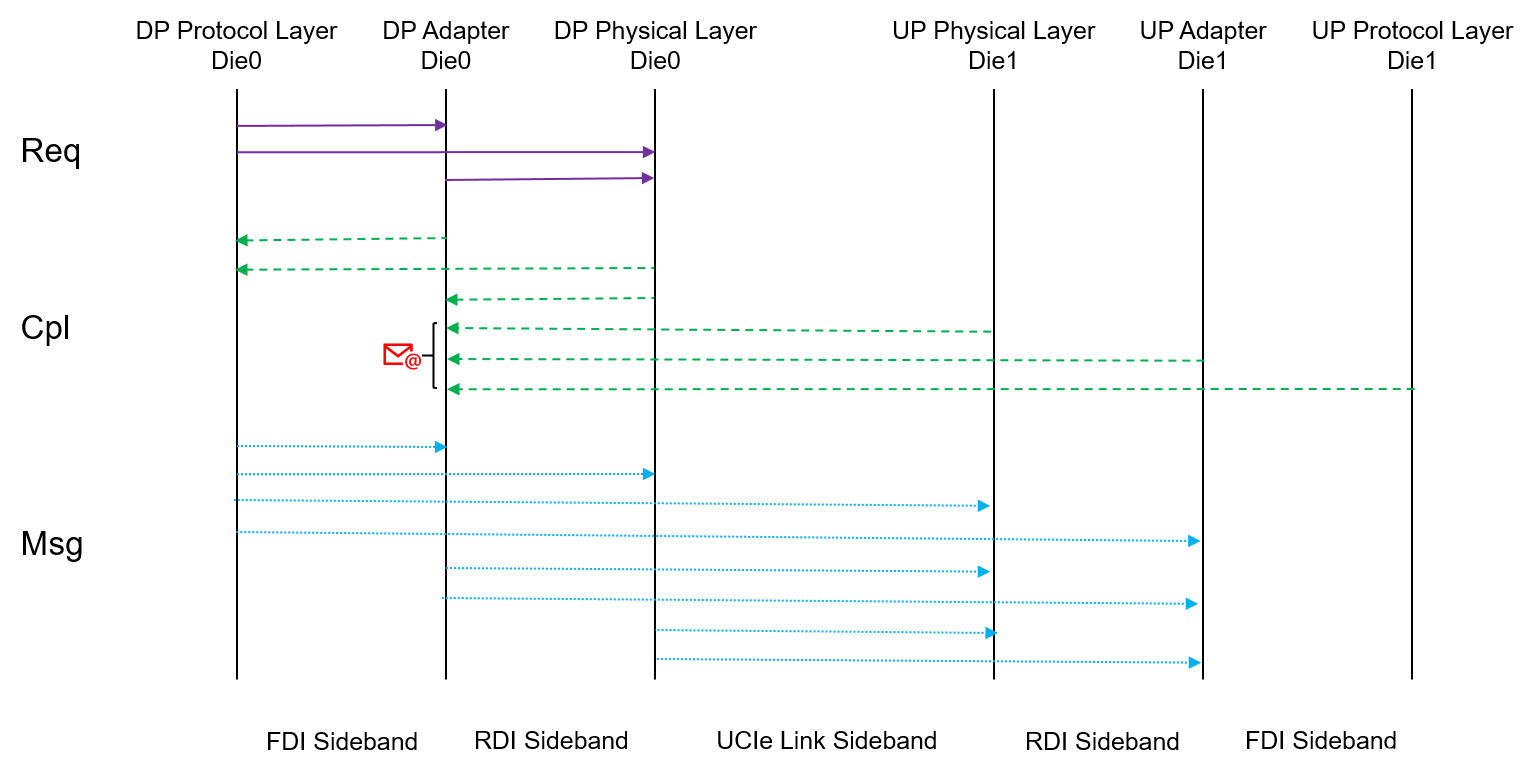

以 Die0->Die1 方向的请求、Die1->Die0 方向的 Completion、Die0->Die1 方向的 Message 为例,笔者总结了 UCIe 1.0 Spec 中明确提到支持的 Sideband 在 UCIe 层间传输路径(或有不全),如图 1 所示。

▲图 1:Sideband 层间传输

留几个问题:

- 跨 Die 的 Completion 均送到了 Adapter,想必是基于 Mailbox 机制访问远端 UCIe 寄存器得到的响应,那么这些 Completion 对应的寄存器访问请求是如何传递到对端的?Adapter Mailbox 触发的到对端 Die 的 Sideband 请求,不算请求吗?

没看到 Adapter 到物理层的寄存器访问请求,是没有吗?- 没看到 Adapter与物理层之间的 Message,是没有吗?

- 没看到物理层访问上层的 Adapter 或协议层的 UCIe 寄存器,是没有需求吗?

- 协议层到协议层之间为什么不能传递 Message?

3. 数据包

3.1 分类

UCIe Sideband 支持 4 种不同的数据包:① 配置读写(CfgRd/Wr)、② 内存读写(MRd/Wr)、③ 完成(Cpl/Cpld)及 ④ 消息(Msg/MsgD)。其中:

-

配置读写及内存读写都是用于寄存器访问,区别在于寄存器位于配置空间还是 MMIO 空间。若访问 UCIe 配置空间内的寄存器,比如 Host Die 访问 EP UCIe Link DVSEC 内的寄存器,则采用 CfgRd/Wr;若访问其他 MMIO 区域的寄存器,比如 D2D Adapter 内的寄存器,则采用 MRd/Wr。 根据寄存器数据位宽的不同,寄存器访问请求又可以分为 32bit 及 64bit。

-

Completion 一般对应寄存器访问请求的 Response。根据是否携带数据及返回数据的位宽不同,Completion 可以分为不带数据的 Cpl 及携带数据的 CplD,CplD 又分 32bit 数据及 64bit 数据。这里的 32/64bit 跟 PCIe 稍有不同,PCIe 中 32/64 bit 是指地址位宽,在 UCIe 中是指寄存器数据位宽。

-

Message 一般用于 D2D 间参数交换、链路训练、链路管理及其他 Vendor 自定义的场景。根据是否携带数据,消息分为 Msg 及 MsgD。

跟 PCIe TLP Header 的 FMT+Type 字段类似,UCIe 通过 Sideband Packet 中的操作码(Opcode)来区分是哪种类型的 Sideband 数据包、是否携带数据、地址数据的位宽。

3.2 格式

每一笔 Sideband Message 都由 64bit Header + 32 或 64bit Data 组成。每个 Clock Cycle 对 Sideband 数据接口采样一次,为 1 个 Phase,有几个 Phase 就代表当前 FDI/RDI Sideband 帧需要几个 UI 才能发送出去。以位宽 32bit 的 FDI/RDI Sideband 数据接口为例,介绍下 Sideband 的数据格式。

3.2.1 MRd/Mwr/CfgRd/CfgWr

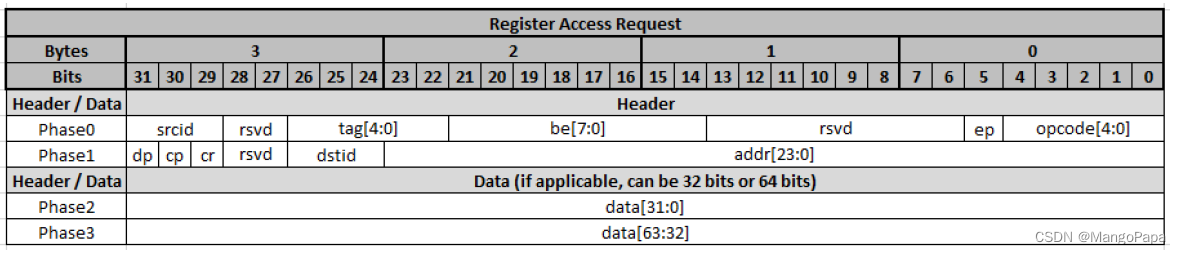

寄存器访问请求的 Sideband 帧格式如图 2 所示。重点介绍几个字段:

-

srcid 及 dstid表明了 Sideband 寄存器请求的来源及目的地(协议层、Adapter、物理层,Local、Remote)。 -

tag是 Requester 添加的标签,用以将 Outstanding 请求跟响应相对应。 -

addr只有 24bit。当寄存器访问请求为 Cfg 类型时,24 位地址由{RL[3:0], Rsvd[7:0], Byte_Offset[11:0]}组成。这里的 RL 即 UCIe Link DVSEC 中的 Register Locator,为 0 表明当前地址为 UCIe Link DVSEC 中的地址,为 F 代表 Adapter 中的一些 shadow 寄存器地址。当寄存器访问请求为 MMIO 类型时,24 位地址由{RL[3:0], Offset[19:0]}组成。无论哪种地址组成方式,这里的地址都是一个在基地址基础上的偏移,基地址由 Host 或 Register Locator 寄存器提供。

▲图 2:Sideband 寄存器访问请求帧格式

3.2.2 Completion

Completion 的 Sideband 帧格式如图 3 所示,其跟寄存器访问请求大同小异,其中有几点不同:

Status,表明当前 Completion 的状态,包括 Success、UR、CA、Stall 四种状态。- Completion 在 FDI 上的去向不依赖于 dstid 而是依赖于 tag。

- 没有 addr 地址字段。

▲图 3:Sideband Completion 帧格式

3.2.3 Message

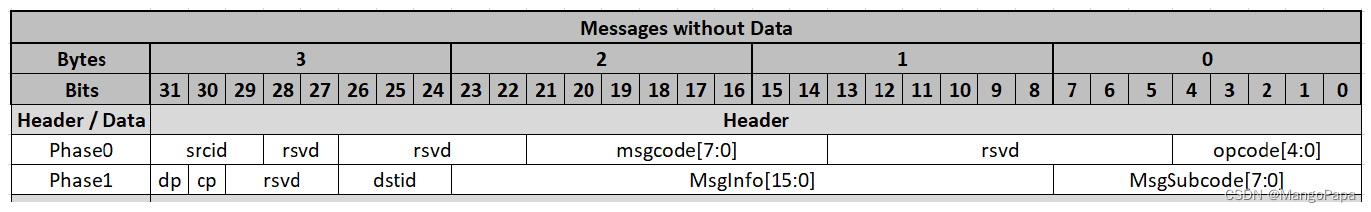

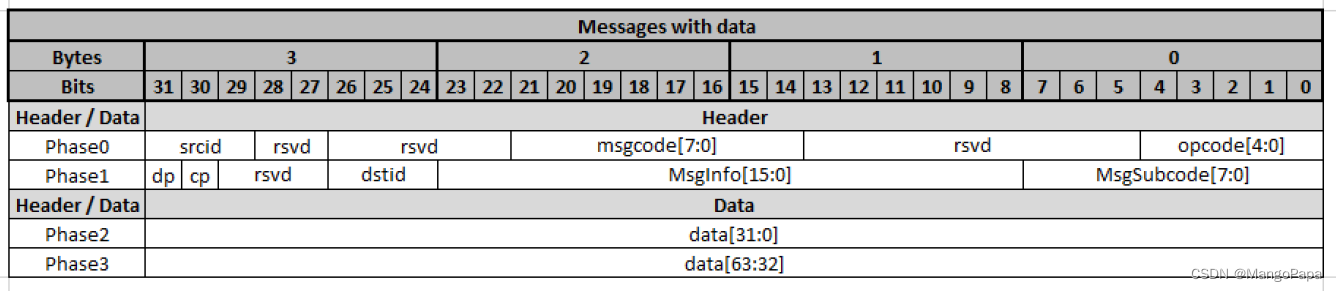

带 Data Payload 和不带 Data 的 Message Sideband 帧格式如图 4,5 所示。比较关键的几个字段位 MsgCode、MsgSubcode、MsgInfo,比较好理解,不再赘述。

▲图 4:Sideband Msg 帧格式

▲图 5:Sideband MsgD 帧格式

4. 接口及时序

4.1 接口分类

UCIe 有 3 类不同的 Sideband 接口:

-

FDI Sideband,在协议层与 Adapter 之间传递 Sideband 信息。FDI 接口上跟 Sideband 相关的信号为

pl_cfg*及lp_cfg*,协议层可以经 FDI Sideband 向 Adapter 发送寄存器访问请求,但 Adapter 不能向协议层发送寄存器访问请求(RDI 接口上存在来源于协议层、终点为远端 Adapter 的 Completion,这个 Completion 对应的请求是怎样的?Adapter 没有通过 Sideband 向协议层发送请求就能得到相关的 Completion 吗?待讨论)。 -

RDI Sideband,在 Adapter 与物理层之间传递 Sideband 信息。RDI 接口上有一组跟 Sideband 相关的信号(pl_cfg* 与 lp_cfg*),逻辑物理层从 RDI 接口接收到 Sideband 相关信息后,封装成帧转换为串行数据流通过 PHY 传输到对端。同理,对端 PHY 发来的串行 Sideband 数据在逻辑物理层解包,通过 RDI 口上的 Sideband 信号发送到 Adapter。

-

UCIe Link Sideband,在 两个 UCIe Die 之间的物理层之间传递 Sideband 信息。跟 FDI RDI Sideband 不同,UCIe Link Sideband 数据线位宽只有 1,传输的为串行 Sideband 数据流,Clock 频率为 800MHz。

4.2 发送时序

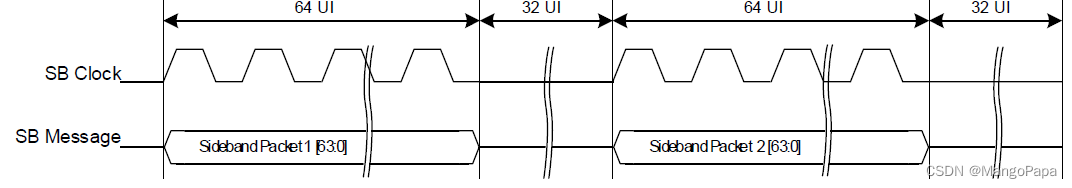

每一笔 Sideband Message 都由 64bit Header + 32 或 64bit Data 组成,若 Data 为 32bit,需要高位补 0 到 64bit。发送串行数据时,每 64bit 为 1 个 Packet,相邻 Packet 之间插入 32bit 0 以分隔不同的 Packet。每个 Clock Cycle 发送 1bit Sideband 数据,下降沿采样。如图 6 所示。

▲图 6:UCIe Sideband Message 格式及其背靠背传输

相比于支持多速率 DDR 传输的 Mainband,UCIe Sideband 采用 800Mbps 的固定速率 SDR 传输。UCIe Sideband 工作在 Always On 状态下,不受低功耗状态的影响,无论 LSM 处于哪种低功耗状态,Sideband 对应的时钟都是能够正常运行的。

5. Sideband 流控

6. 问题讨论

1. Milbox 机制需要定义 Local 和 Remote Die 吗?适用于 Local Die 吗?

不用定义 Local 和 Remote,UCIe Link DVSEC 的 Mailbox 寄存器也没有地方来定义 Local 或 Remote。Mailbox 机制就是唯一访问对端用的,访问 Local Die 的寄存器直接通过 Sideband 访问就好了,用不到 Mailbox。

7. 参考 & 友链

- UCIe Spec r1.0, Chapter 6

- 谈谈UCIe的Sideband

- UCIe协议详解(Sideband)

- UCIe 软件配置

- UCIe 物理层介绍(逻辑物理篇)

— END —

🔥 精选往期 UCIe 协议系列文章,请查看【 Chiplet 专栏】🔥

⬆️ 返回顶部 ⬆️

-

相关阅读:

英飞凌TLF35584规格书中文

[Vue 配置] Vite + Vue3 项目配置 Tailwind CSS

20min带你学习——HTTP协议、以及经典面试问题

Navicat操作数据库与Mysql常见命令操作实战

栈和队列基础

计算机网络原原理学习资料分享---第一章/第一节(为有梦想的自己加油!)

Q&A特辑 | 看了这场直播,我找到了设备指纹“从不说谎”的原因

react hooks 生命周期渲染时机简述

Docker&Kubernetes ❀ Service下Port端口区分

Linux系统编程

- 原文地址:https://blog.csdn.net/weixin_40357487/article/details/126960034