-

【UCIe】UCIe 软件配置

🔥点击查看精选 UCIe 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/126896926】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

0. 前言

UCIe 在协议层复用 PCIe 和 CXL,因此 UCIe 的一个关键目标即 尽可能多地继承/复用原有的基于 PCIe 及 CXL 的软件生态。UCIe 1.0 的确这也是这么干的。系统软件是如何发现 UCIe 链路的?如何判断 UCIe 链路的有效性?软件如何配置 UCIe 链路?如何检测 UCIe 链路状态?一起来看看。

缩写释义

- RC - Root Complex,根复合体。

- RP - Root Port,根端口。

- DSP/DP - Downstream Port,下行端口,设备中远离处理器的一端。

- USP/UP - Upstream Port,上行端口,设备中靠近处理器的一端。

- EP - End Point,终端设备。

- SB - Sideband,边带。

- RCRB - Root Complex Register Block,根复合体寄存器块。

- RCiEP - Root Complex Integrated Endpoint,集成了 EP 的 RC。

- DVSEC - Designated Vendor-Specific Extended Capability

- CiRB - UCIe Register Block?UCIe 的寄存器块,由 Host 指定。

- CiSRB - UCIe Switch Register Block?UCIe Switch 中的寄存器块。

- CIDT - UCIe Discovery Table,UCIe 设备的查找表。

- ACPI - Advanced Configuration and Power Interface,高级配置与电源接口。

1. UCIe 链路有效性及链路发现

1.1 链路有效性

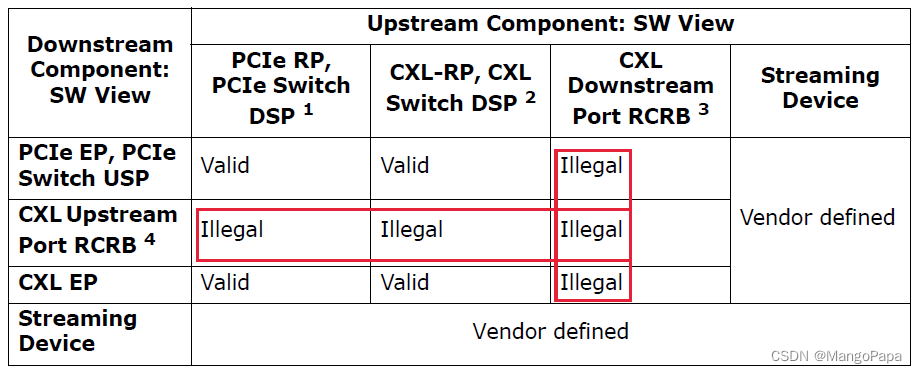

UCIe 链路两端都可以接哪些设备呢?如表 1 所示,UCIe 链路的上游组件(Upstream Component)可以为 PCIe/CXL RP,也可以为 PCIe/CXL Switch DSP,但 不支持 CXL DSP RCRB(CXL 1.1 支持 DSP/USP RCRB,到 CXL 2.0 就没有了,UCIe 不支持 CXL 1.1);UCIe 链路下游组件可以为 PCIe/CXL EP,也可以为 PCIe/CXL Switch USP,不支持 CXL USP RCRB。从软件角度来看 UCIe 设备,协议层采用 PCIe 协议的 Host DP 就是一个具备 PCIe 相关能力的 RP,协议层采用的 CXL 协议的 Host DP 就是一个具备 PCIe 能力及 CXL DVSEC 能力的 RP。对于采用 Streaming Protocol 的 UCIe 设备,Spec 中没有做规定,具体方案具体实现。

▼表 1:UCIe 链路两端支持的组件

注:Downstream Component 中没有提到 CXL Switch USP,但是 Spec 正文明确提到了支持 CXL Switch。

1.2 链路发现

软件或 Firmware 通过探查当前设备中是否存在 UCIe Link DVSEC 能力寄存器来判断系统中是否存在 UCIe 链路。

-

对于 Host 而言,UCIe Link DVSEC 寄存器块位于 RP 的 CiRB 中,每一路 UCIe Link 都对应一个独立的 CiRB。如 Host 发现某个 UCIe Link 对接多个 RP,那就是多个协议栈共享同一 UCIe Link。

-

对于 EP 而言,UCIe Link DVSEC 寄存器块位于 EP Dev0/Fn0 的配置空间中。

-

对于 Switch USP 而言,UCIe Link DVSEC 寄存器块位于 Switch USP Dev0/Fn0 的配置空间中。

-

对于 Switch DSP 而言,UCIe Link DVSEC 寄存器块位于 Switch DSP CiSRB 中,DSP CiRSB 的基地址位于 Switch USP Dev0/Fn0 的 CiRSB DVSEC Capability 寄存器中,DSP CiRSB 地址范围也处于 USP BAR 空间内。

-

对于 Retimer 而言,这都 UCIe Retimer 了,还要问?肯定是 UCIe Link 了。UCIe Link DVSEC 位于 Retimer Sideband 配置空间中。

2. UCIe 寄存器

2.1 UCIe 寄存器分类

UCIe 1.0 中寄存器一共分 5 类,其中 2 个 UCIe DVSEC Capability Block,3 个 MMIO-Mapped Register Block。UCIe DVSEC 分为 UCIe Link DVSEC 及 CiSRB DVSEC,UCIe Link DVSEC 是所有 UCIe Component 都支持的,CiSRB DVSEC 只有 Switch USP 支持。MMIO-Mapped Register Block 包括 D2D/PHY、Test/Compliance 及 Implementation Specific 三类寄存器块。

-

UCIe Link DVSEC - UCIe Link 最基本的能力寄存器,SW 通过识别该 DVSEC 来区分 UCIe 还是标准的 PCIe/CXL RP 或 Device。定义了最基本的 UCIe 相关配置,根据设备类型的不同,有效的字段也不同。

-

CiSRB DVSEC - 主要用来存放 CiSRB 的基地址。

-

UCIe D2D/PHY Register Block - Size 为 8KB,D2D Adapter 和 Physical Layer 各占 4KB。其中定义了 UCIe D2D/PHY 实现过程中的一些配置,比如链路训练初始化及修复用到的一些参数、流控、注错、FIFO 状态、Error 状态及控制等等。

-

UCIe Test/Compliance Register Block - 该部分寄存器是给 UCIe 测试及兼容性测试用的,UCIe 1.0 Spec 中没有给出详细描述。

-

UCIe Implementation Specific Register Block - 这部分为 Vendor 自定义的寄存器。

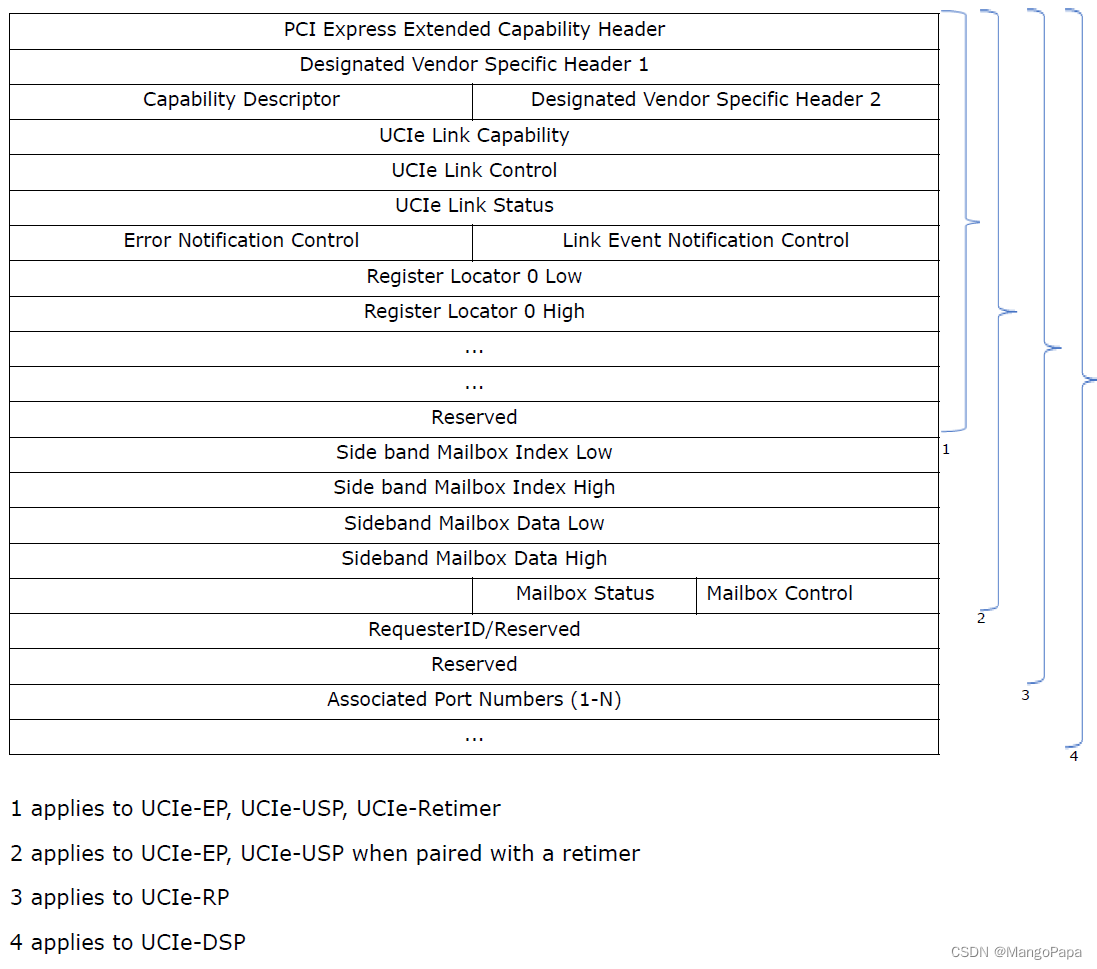

2.1.1 UCIe Link DVSEC

UCIe Link DVSEC 中定义了 UCIe Link 所需的一些最基本的寄存器(图 1)。举几个例子:

-

Capability Descriptor,用来指示当前 UCIe Link 支持几个 Register Locator、是否支持 Sideband Mailbox、跟几路 RP 有关联。

-

UCIe Link Capability、Link Control、Link Statue,用来 ① 指示当前 UCIe 模块具备的最大链路宽度、最大链路速率、是否为 Retimer、Stack 数量、封装形式等能力;② 控制 UCIe Link 工作在相关配置;③ 显示 UCIe Link 的工作状态。

-

Link Event 及 Error Notification Control,对 UCIe 链路的事件或错误进行控制。

-

Register Locator,存放 除 UCIe DVSEC 之外 D2D/PHY 等其他 MMIO-Mapped 寄存器块的基地址。

-

Sideband Mailbox Index、Data、Control、Status,存放 Sideband Mailbox 寄存器访问的访问类型(32/64bit,Mem/Cfg,Rd/Wr)、访问地址、读写数据、访问状态,下文窗口机制中稍微详细讲。

▲图 1:UCIe Link DVSEC

2.1.2 CiSRB DVSEC

CiSRB DVSEC Capability 仅存在于 Switch USP 中,其中最重要的一个寄存器就是 CiSRB Base Address,存放了 CiSRB 的基地址。CiSRB 位于 Switch DSP 中,CiSRB 中存放有(可选) UCIe Link DVSEC。一般而言,一个 Switch DSP 对应 Switch USP 中的一个 CiSRB DVSEC Capability。Switch USP 中可以只具备 CiSRB DVSEC Capability 而不具备 UCIe Link DVSEC Capability。

2.1.3 CiRB 及 CiSRB

CiRB 及 CiSRB 都是 UCIe 的一段寄存器空间,其中只能存放 UCIe 相关的寄存器,不能放置其他非 UCIe 相关的寄存器。CiRB 及 CiSRB 内包含 UCIe Link DVSEC、D2D/PHY、Test/Compliance 及 Implementation Specific 寄存器块。CiRB 是 Host 端的一段静态区域,其基地址由 Host 指定,每一路 UCIe Link 都有一个唯一的 CiRB 基地址。CiRSB 是 Switch USP BAR 范围内的一段寄存器空间,其基地址存放在 Switch USP Dev0/Fn0 的 CiSRB DVSEC Capability 寄存器中,若存在多个 CiSRB 则对应 USP 内的多个 CiSRB DVSEC Capability。

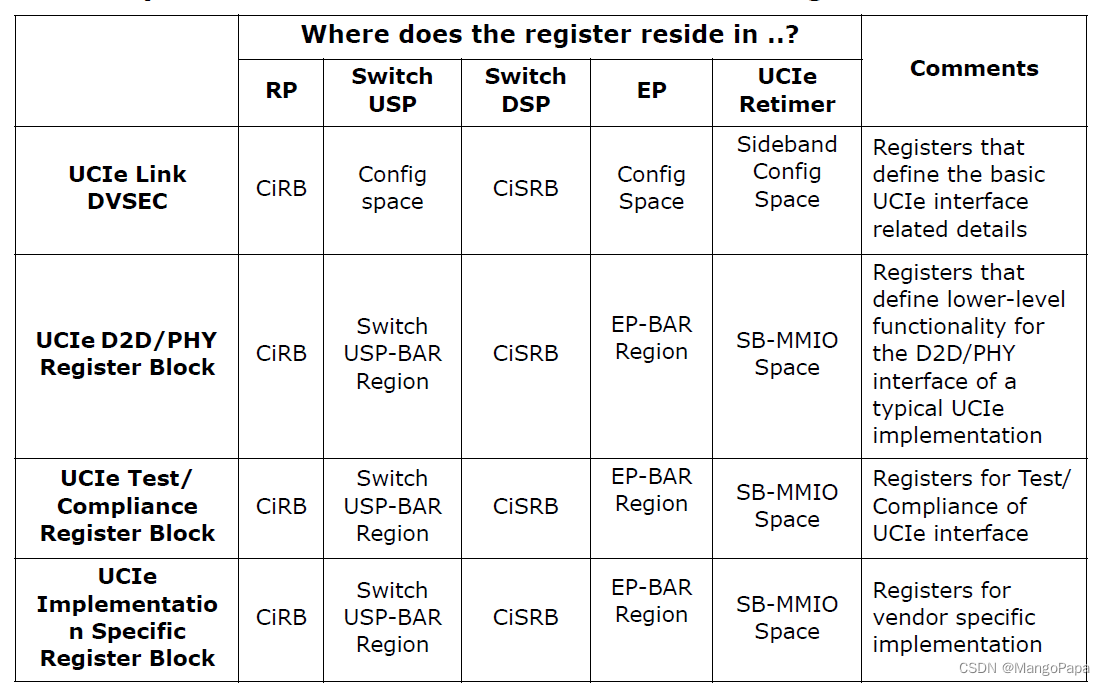

2.2 寄存器位置及访问

上文介绍了 UCIe 链路中的寄存器,接下来看看这些寄存器放在哪儿了。除 CiSRB DVSEC 只能位于 UCIe Switch USP 中之外,UCIe 链路的其他 4 类寄存器在不同 UCIe Component 中的位置如表 2 所示。

▼表 2:UCIe 链路寄存器的位置

从表中可见:

- RP 中所有 UCIe 链路相关寄存器均位于 CiRB 中。

- Switch DSP 中所有 UCIe 链路相关寄存器均位于 CiSRB 中。

- 对于 Switch USP 及 EP,其配置空间中仅保留有 UCIe Link DVSEC,其他 UCIe Link 相关寄存器位于 BAR 规定的空间内。

- 对于 UCIe Retimer,所有 UCIe Link 相关寄存器均位于 Sideband 空间内,其中 UCIe Link DVSEC 位于 SB 配置空间,其他位于 MMIO 空间。

对于 CiRB 及 CiSRB 内的寄存器,没有跨 Die,RP 或 Switch 内的软件能够直接访问到。

对于 Switch USP 及 EP 内的 UCIe 寄存器,位于配置空间内的寄存器用需要用 CfgRd 或 CfgWr 去访问,位于 Memory Mapped 空间的寄存器则采用 MemWr 或 MemRd 去访问。

Host SW 不能直接访问 Retimer 的寄存器,需要采用窗口机制(Window Mechanism)走 Sideband 去访问。一般情况下,UCIe Component 只需要访问距离它近的 UCIe Retimer,比如 RP/DSP 访问近端 Retimer 寄存器,EP/USP 访问远端 Retimer 寄存器。此外,Host SW 也可以访问远端的寄存器,但一般仅用于 Debug 或链路健康检测。采用 Sideband 访问寄存器时,仅限于前文提到的 UCIe 相关寄存器,不能访问其他寄存器。

2.2.1 窗口机制

前文介绍 UCIe Link DVSEC 时提到了 Mailbox 相关寄存器,Sideband 的窗口机制就是通过 UCIe Link DVSEC 中的 Mailbox 寄存器实现的。Mailbox 相关的四个寄存器如下:

- Sideband Mailbox Index,填充寄存器访问方式(32/64bit,Mem/Cfg,Rd/Wr)、读写类型、地址、Byte Enable。

- Sideband Mailbox Data,存放要写的数据或读回来的数据。

- Mailbox Status,Sideband 寄存器访问结果状态,包括 CA、UR、Success。

- Mailbox Control,bit0 写 1 之后会生成 Sideband 寄存器请求。

3. 问题讨论

1. CXL DSP/USP RCRB 是什么?

CXL Downstream/Upstream Port RCRB 是 CXL 的 4K Memory Mapped 寄存器空间,只有 CXL 1.1 才有。UCIe 链路两端不能出现通过 CXL DSP/USP RCRB 枚举出来的 CXL 设备,因为 UCIe 不支持 CXL 1.1 协议。

2. Spec 中,UCIe 链路支持的 Downstream Component 中,为什么没有提到 CXL Switch USP 呢?

表格中是没有提到 CXL Switch USP 的,但正文中提到了 UCIe Downstream Component 可以为 CXL Switch,所以笔者认为还是支持 CXL Switch USP 的。

3. CiSRB 和 CiSRB DVSEC Capability 是啥关系?

CiSRB 是寄存器块,位于 Switch DSP 中。CiSRB DVSEC Capability 是存放有 CiSRB 基地址等 CiSRB 能力的寄存器,位于 Switch USP 的配置空间中。

4. UCIe Link DVSEC 和 CiSRB DVSEC 区别是什么?

UCIe Link DVSEC 位于 RP 的 CiRB 中、Switch DSP 的 CiSRB 中或者其他 Component 的配置空间中,CiSRB DVSEC 位于且只能位于 Switch USP 中。UCIe Link DVSEC 中规定了 UCIe Link 相关的一些能力寄存器,是 CiRB/CiSRB/配置空间的重要组成部分;CiSRB DVSEC 中主要规定了 CiSRB 的基地址,不是 CiSRB 的组成部分。

4. 参考 & 友链

- UCIe Spec r1.0, Chapter 7

- UCIe协议详解(概述)

- ACPI 与 UEFI

- 我所认识的 ACPI

— END —

🔥 精选往期 UCIe 协议系列文章,请查看【 Chiplet 专栏】🔥

⬆️ 返回顶部 ⬆️

-

相关阅读:

iOS CGRect CGPoint NSRange等结构体的NSLog打印输出

服务器空间不足的解决方法

k8s晋级之亲和性与反亲和性

python Kmeans聚类 - CPU or GPU?

SpringBoot使用kafka事务-消费者方

php laravel 文件上传 csrf 路由route name命名

day02 mybatis

RabbitMQ配置文件_修改RabbitMQ MQTT的1883端口

远程办公软件OpenText Exceed TurboX 12.5 (最新版本)的新功能介绍

如何实现主机与容器之间数据的同步?以nginx:v1镜像为例,进行验证。提交操作步骤

- 原文地址:https://blog.csdn.net/weixin_40357487/article/details/126896926