-

Verilog HDL——条件语句

if-else语句

规范约定:

- 如果表达式的值出现0、x、z,则全部按照“假”处理,若为1,则按“真”处理;

- 无论单句还是多句,都通过“begin end”块括起来;

- 尽量保持if语句分支的完整性;

例:

/* if-else 选择语句 */ module sel(sel_in,a_in,b_in,c_in,d_in,q_out); input [1:0]sel_in; input [4:0]a_in,b_in,c_in,d_in; output [4:0]q_out; reg [4:0]q_out; always @(a_in or b_in or c_in or d_in or sel_in) begin if(sel_in == 2'b00) q_out <= a_in; else if(sel_in == 2'b01) q_out <= b_in; else if(sel_in == 2'b10) q_out <= c_in; else q_out <= d_in; end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

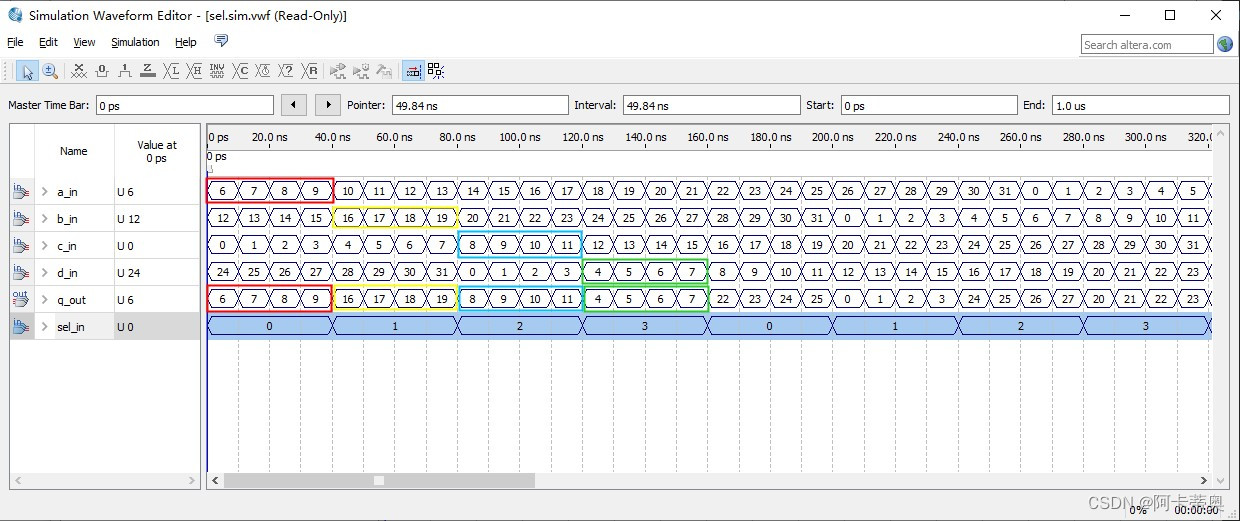

波形:

case语句

case语句的比较规则

case 0 1 x z 0 True False False False 1 False True False False x False False True False z False False False True /* case 多分支选择语句 */ module decode_opmode( a_in,b_in,opmode,q_out ); input [7:0] a_in; input [7:0] b_in; input [1:0] opmode; output [7:0] q_out; reg [7:0] q_out; always @(a_in or b_in or opmode)begin case(opmode) 2'b00: q_out = a_in + b_in; 2'b01: q_out = a_in + b_in; 2'b10: q_out = (~a_in)+1; 2'b11: q_out = (~b_in)+1; endcase end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

opmode=00时,q_out =(108 =88+20) = (110=89+21)

opmode=01时,q_out =(68 =90-22) = (68=91+23)

opmode=10时,q_out =(164 =92取反+1) = (163=93取反+1)

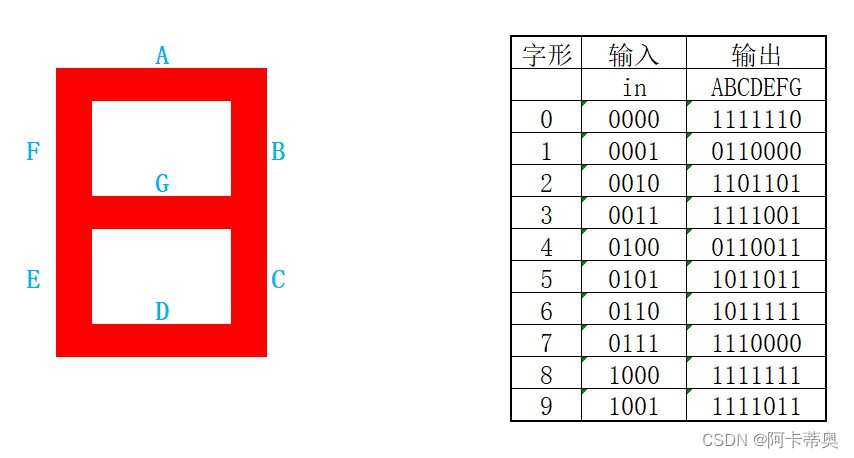

opmode=11时,q_out =(230=26取反+1) = (229=27取反+1)BCD数码管译码描述

/* BCD数码管译码描述 */ module BCD_decoder(in, out); output[6:0]out; input[3:0]in; reg[6:0]out; always@(in) begin case(in) 4'b0000:out = 7'b1111110; 4'b0001:out = 7'b0110000; 4'b0010:out = 7'b1101101; 4'b0011:out = 7'b1111001; 4'b0100:out = 7'b0110011; 4'b0101:out = 7'b1011011; 4'b0110:out = 7'b1011111; 4'b0111:out = 7'b1110000; 4'b1000:out = 7'b1111111; 4'b1001:out = 7'b1111011; default:out = 7'bx; endcase end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

casez/casex语句

casez语句的比较规则

casez 0 1 x z 0 True False False True 1 False True False True x False False True True z True True True True casex语句的比较规则

casex 0 1 x z 0 True False True True 1 False True True True x True True True True z True True True True /* casex 多分支选择语句 */ module decode_opmodex( a_in,b_in,opmode,q_out ); input [7:0] a_in; input [7:0] b_in; input [1:0] opmode; output [7:0] q_out; reg [7:0] q_out; always @(a_in or b_in or opmode)begin casex(opmode) 4'b0001: q_out = a_in + b_in; 4'b001x: q_out = a_in - b_in; 4'b01xx: q_out = (~a_in)+1; 4'b1zx?: q_out = (~b_in)+1; default: q_out = a_in + b_in; endcase end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

-

相关阅读:

【电商实战02】如何借助工具快速生成代码?初学者容易踩的坑有哪些?

制作出浪漫玫瑰?SoildWorks:“我可以!”

如何阅读文献

docker&kubernets篇(二十三)

Gif图片分解(支持批量)

[iOS开发-MVC初识]

面试:dumpsys meminfo 内存信息含义

基于象鼻虫损害优化算法求解单目标无约束问题并可视化分析(Matlab代码实现)

ZCC5429 异步升压芯片

Google Earth Engine(GEE)——全球河流宽度数据集1970—2017年

- 原文地址:https://blog.csdn.net/akadiao/article/details/126884390