-

基于FPGA的五段流水CPU设计

目 录

1 毕业设计概述 1

1.1 毕设目的 1

1.2 设计任务 1

1.3 设计要求 1

1.4 技术指标 2

2 总体方案设计 4

2.1 单周期CPU设计 4

2.2 单周期多级中断机制设计 10

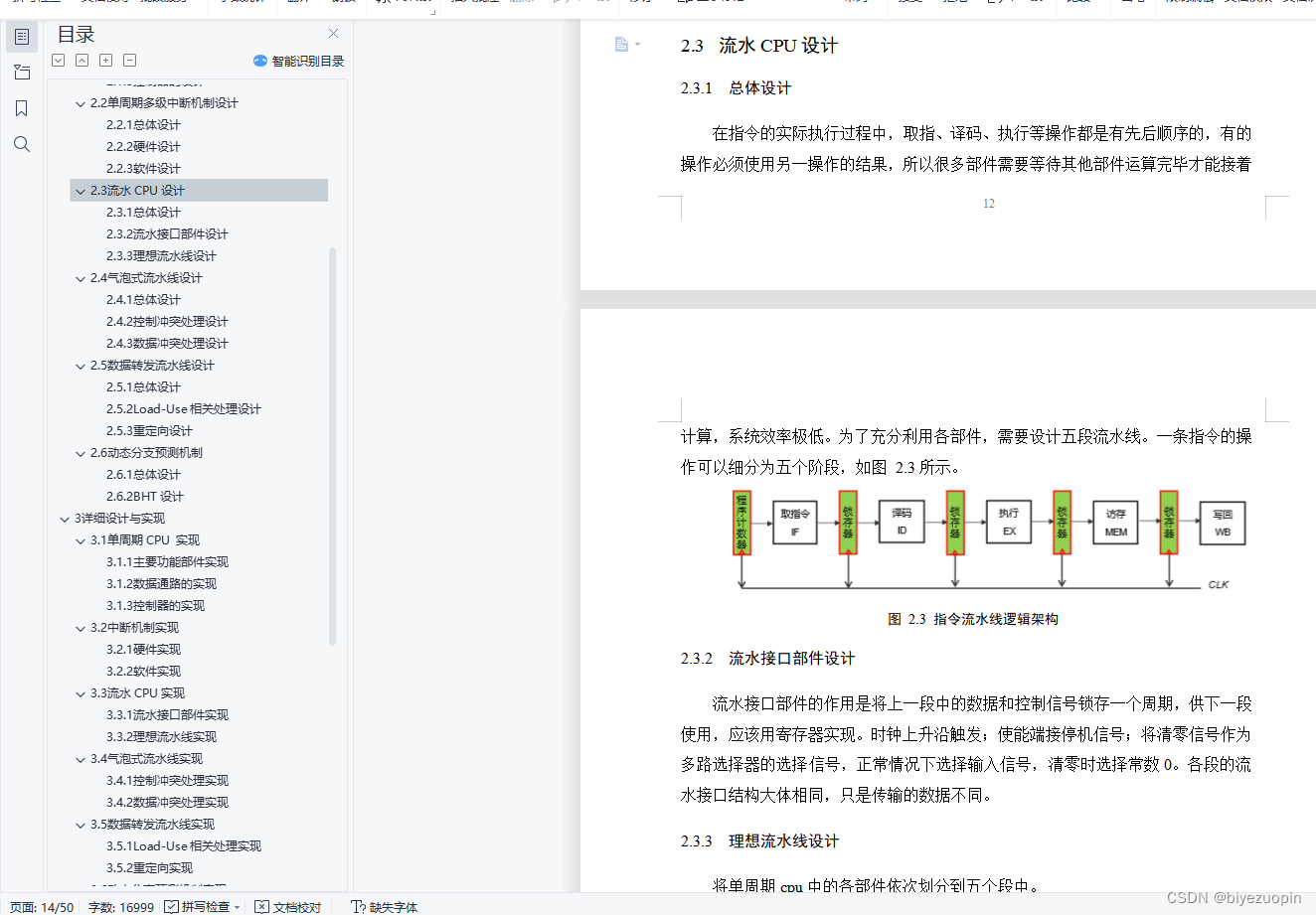

2.3 流水CPU设计 12

2.4 气泡式流水线设计 13

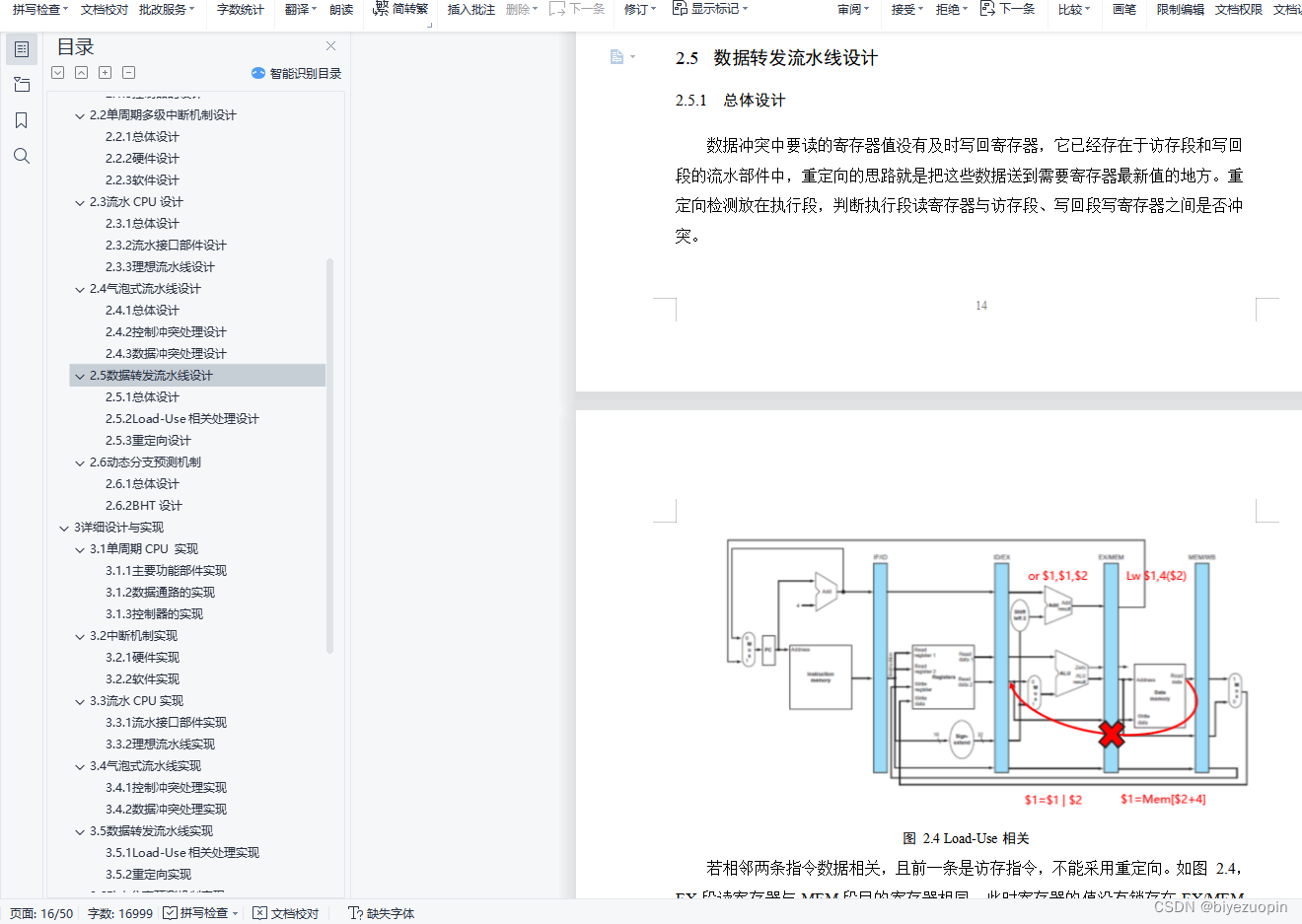

2.5 数据转发流水线设计 14

2.6 动态分支预测机制 15

3 详细设计与实现 17

3.1 单周期CPU 实现 17

3.2 中断机制实现 22

3.3 流水CPU实现 25

3.4 气泡式流水线实现 27

3.5 数据转发流水线实现 28

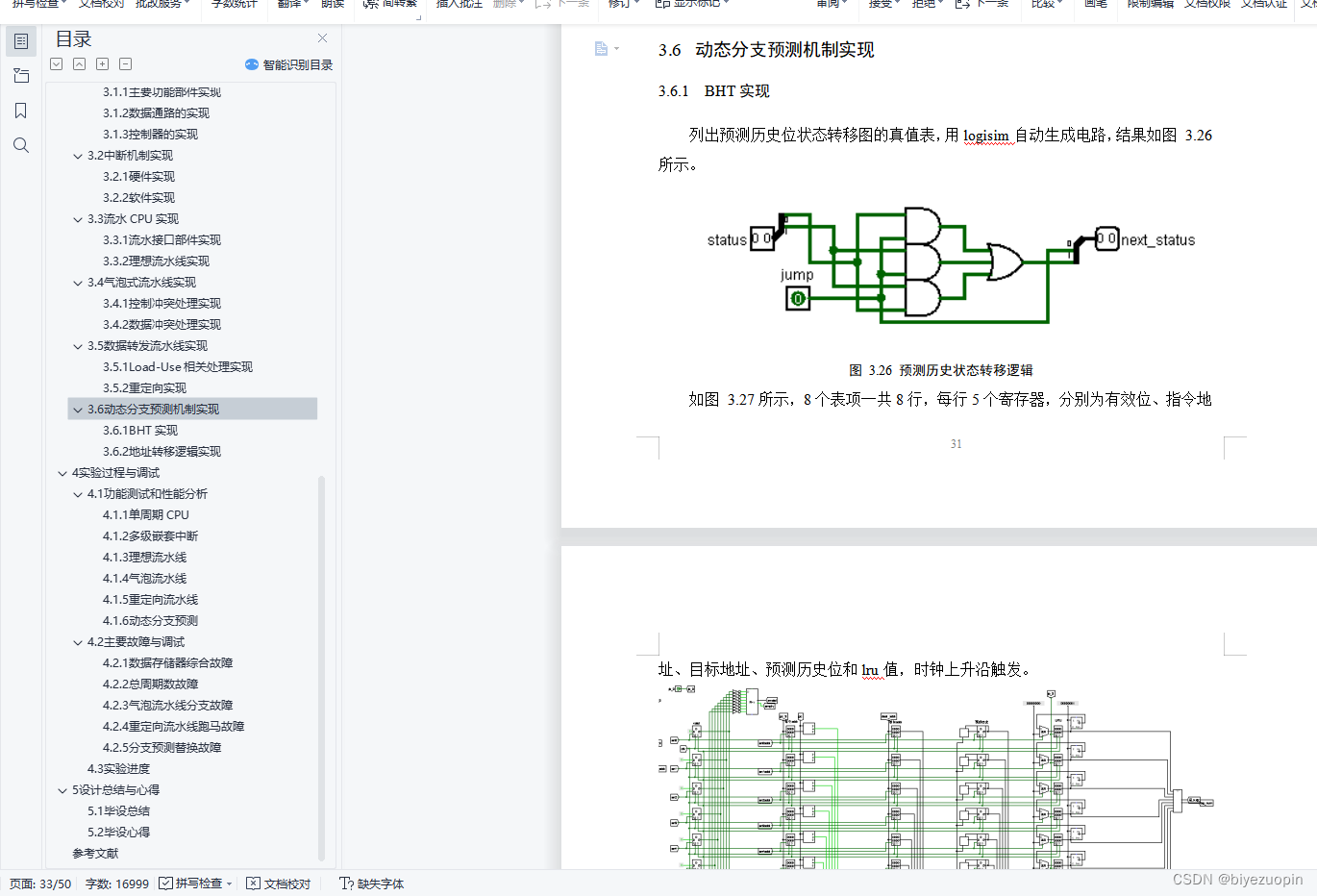

3.6 动态分支预测机制实现 30

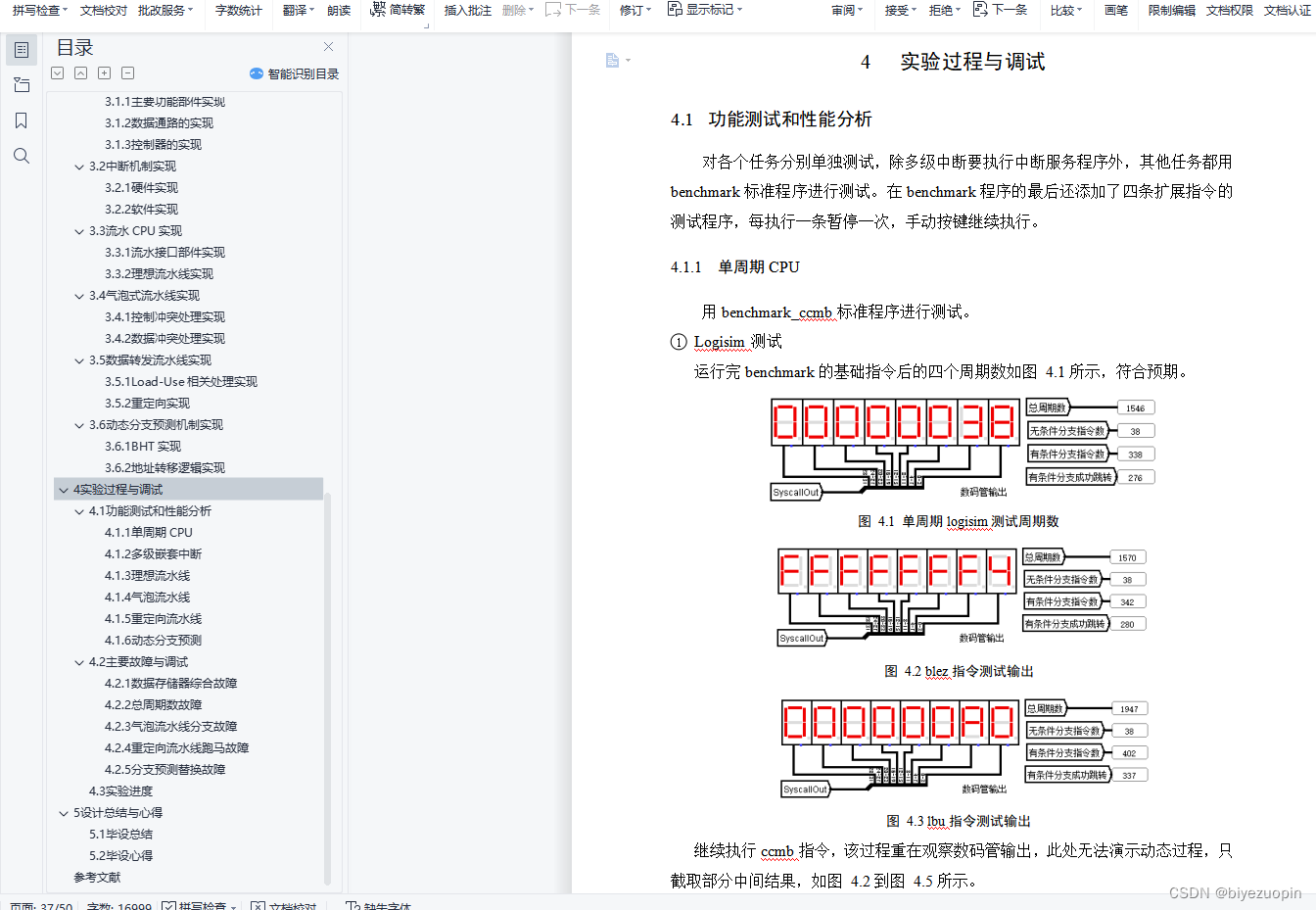

4 实验过程与调试 34

4.1 功能测试和性能分析 34

4.2 主要故障与调试 39

4.3 实验进度 44

5 设计总结与心得 45

5.1 毕设总结 45

5.2 毕设心得 45

参考文献 47

1.2设计任务

本毕业设计的总体目标是利用FPGA以及相关外围器件,在毕业实验中完成的单周期cpu基础上,完成单周期cpu在FPGA开发板上的正确运行,并改造设计五段流水CPU,要求所设计的流水CPU系统能支持自动和单步运行方式,能正确地执行存放在主存中的程序的功能,对主要的数据流和控制流通过LED、数码管等适时的进行显示,方便监控和调试。对于五段流水,要求分别使用气泡、重定向、分支预测等方式处理数据冲突和控制冲突等,此外,还要求支持中断请求。尽可能利用EDA软件或仿真软件对模型机系统中各部件进行仿真分析和功能验证。本文转载自http://www.biyezuopin.vip/onews.asp?id=15109在学有余力的前提下,可进一步扩展相关功能。

1.3设计要求

(1)根据毕业设计指导书的要求,制定出设计方案;

(2)分析指令系统格式,指令系统功能。

(3)根据指令系统构建基本功能部件,主要数据通路。

(4)根据功能部件及数据通路连接,分析所需要的控制信号以及这些控制信号的有效形式;

(5)设计出实现指令功能的硬布线控制器;

(6)调试、数据分析、验收检查;

(7)毕业设计报告和总结。

1.4技术指标

(1)支持表 1.1的27条基本32位MIPS指令;

(2)支持教师指定的4条扩展指令,即表1.1中的最后四条指令,分别任blez、xori、sltiu和lbu;

(3)支持多级嵌套中断,利用中断触发扩展指令集测试程序;

(4)支持5段流水机制,可处理数据冒险,结构冒险,分支冒险;

(5)能运行由自己所设计的指令系统构成的一段测试程序,测试程序应能涵盖所有指令,程序执行功能正确。

(6)能运行教师提供的标准测试程序,并自动统计执行周期数。

(7)对于基本指令,测试程序一次性运行,对于扩展指令,要求单步手动执行,一次执行一段。

(8)能自动统计各类分支指令数目,如不同种类指令的条数、冒险冲突次数、插入气泡数目、load-use冲突次数、动态分支预测流水线能自动统计预测成功与失败次数。- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

- 176

- 177

- 178

- 179

- 180

- 181

- 182

- 183

- 184

- 185

- 186

- 187

- 188

- 189

- 190

- 191

- 192

- 193

- 194

- 195

- 196

- 197

- 198

- 199

- 200

- 201

- 202

- 203

- 204

- 205

- 206

- 207

- 208

- 209

- 210

- 211

- 212

- 213

- 214

- 215

- 216

- 217

- 218

- 219

- 220

- 221

- 222

- 223

- 224

- 225

- 226

- 227

- 228

- 229

- 230

- 231

- 232

- 233

- 234

- 235

- 236

- 237

- 238

- 239

- 240

- 241

- 242

- 243

- 244

- 245

- 246

- 247

- 248

- 249

- 250

- 251

- 252

- 253

- 254

- 255

- 256

- 257

- 258

- 259

- 260

- 261

- 262

- 263

- 264

- 265

- 266

- 267

- 268

- 269

- 270

- 271

- 272

- 273

- 274

- 275

- 276

- 277

- 278

- 279

- 280

- 281

- 282

- 283

- 284

- 285

- 286

- 287

- 288

- 289

- 290

- 291

- 292

- 293

- 294

- 295

- 296

- 297

- 298

- 299

- 300

- 301

- 302

- 303

- 304

- 305

- 306

- 307

- 308

- 309

- 310

- 311

- 312

- 313

- 314

- 315

- 316

- 317

- 318

- 319

- 320

- 321

- 322

- 323

- 324

- 325

- 326

- 327

- 328

- 329

- 330

- 331

- 332

- 333

- 334

- 335

- 336

- 337

- 338

- 339

- 340

- 341

- 342

- 343

- 344

- 345

- 346

- 347

- 348

- 349

- 350

- 351

-

相关阅读:

基于LangChain的LLM应用开发3——记忆

Mongodb使用killCursors停止运行的cursor

目标检测|边框检测框转换,交并比计算 代码实现

FPGA project : inf_rcv

【GD32F427开发板试用】FreeRTOS移植工程

微信公众号开发基本流程(记录初级流程)

Android 11.0 framework层实现app默认全屏显示

Mac平台M1PRO芯片MiniCPM-V-2.6网页部署跑通

面向OLAP的列式存储DBMS-12-[ClickHouse]的管理与运维

C/C++教程 从入门到精通《第二十四章》——Qt制作天气预报

- 原文地址:https://blog.csdn.net/sheziqiong/article/details/126828112