-

vivado中的常用AXI接口IP核

AXI是xilinx中常用的数据接口。种类和引脚数量极多。

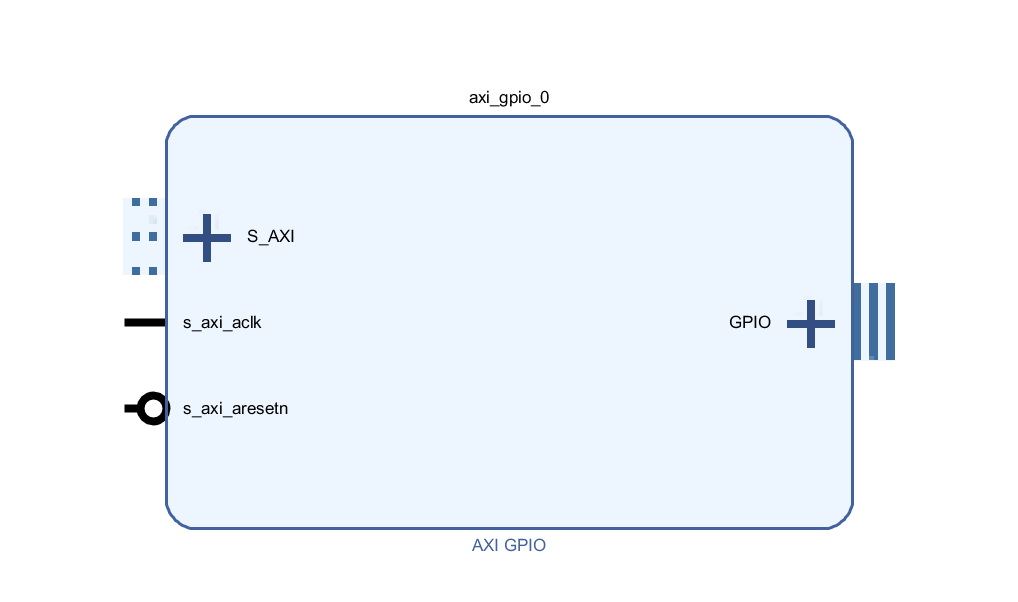

1.AXI_GPIO

AXI_GPIO为AXI接口提供了一个通用的输入/输出接口。可以配置成单通道和双通道,每个通道的位宽都可以单独设置。另外,通过打开或者关闭三通道缓冲器,AXI_GPIO还可以被动态的配置成输入输出接口。

从图中可以看出模块左侧实现了一个32位的AXI_LITE从接口,用于主机访问AXI_GPIO内部各通道的寄存器。当配置IP核使能了中断模式时,右侧接口发生变化,模块还能向主机发送中断信号。Processor System Reset

为整个处理器系统提供复位信号,会处理输入端的各种复位条件,并在输出端产生相应的复位信号。

AXI_Interconnect

将一个或者多个AXI存储映射的主器件连接到一个或者多个存储映射的从器件。管理所连接的AXI接口通信。AXI SmartConnect

也是实现一个或者多个内存映射主设备连接到一个或多个内存映射从设备,一般可以作为AXI_InterConnect的替代品且具有更好的性能。Cincat

实现了单个分散信号整合成总线信号。VDMA

用于将AXI Stream格式的数据流转化成Memory Map格式或者将Memory Map格式的数据转化成AXI Stream数据流。实现系统内存(主要指DDR3)和基于AXI4_Stream的目标视频IP之间的高速数据移动。且内嵌了多帧缓存功能。可以实现乒乓操作。

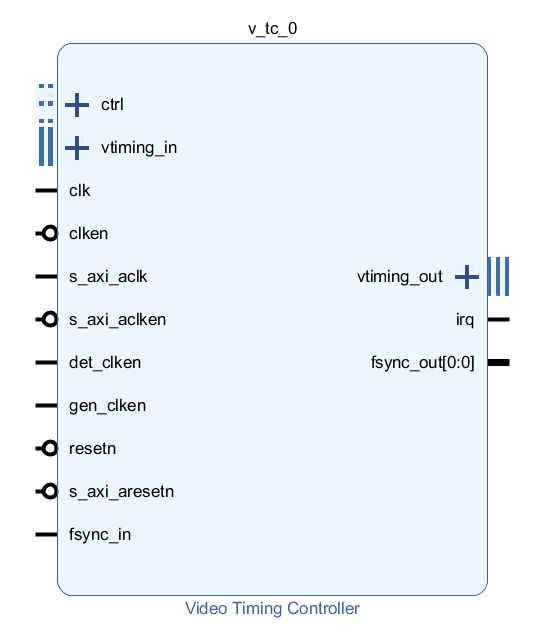

部分接口说明:名称 功能 S_AXI_LITE PS 通过这个接口配置 VDMA 的寄存器 s_axi_lite_aclk AXI VDMA AXI4-Lite 接口时钟 M_AXI_MM2S 读通道存储器端映射的 AXI4 接口,提供对存储器(DDR3)的访问 m_axi_mm2s_aclk AXI VDMA MM2S 时钟 M_AXIS_MM2S 读通道 AXI-Stream 端映射的 AXI4 接口,用于输出到外设 m_axis_mm2s_aclk AXI VDMA MM2S AXIS 时钟 mm2s_introut 读通道中断输出信号 Video Timing Controller

VGA时序产生器,可以通过AXI_LITE接口动态的配置该时序。

Video Out

部分接口说明:名称 功能 video_in AXI-Stream 接口输入数据流 s_axi_lite_aclk AXI VDMA AXI4-Lite 接口时钟 vtiming_in Video 时序输入接口 vid_io_out Video 数据流输出接口 vtg_ce VTC 时钟使能信号 -

相关阅读:

1154:亲和数

[附源码]Python计算机毕业设计Django的疫苗接种管理系统

Python爬取豆瓣电影+数据可视化,爬虫教程!

人类的态势感知可分为先验、似然、后验的三部分

DTO、VO、BO、PO等各种XO汇总

快速学习react 从入门到入土

补充:js 制作qq、微信 的表情 缺少的微信表情图片

如何阅读 Paper

高能整理,性能测试-寻找TPS性能拐点与脚本Error报错排查(超细)

Redis的各种部署

- 原文地址:https://blog.csdn.net/q1594/article/details/126819274