-

SCAN BASIC --- PARTIII scan and atpg flow

前面章节介绍了scan 的基本概念以及测试流程。本小节介绍scan 的形成和atpg flow。

1. overview

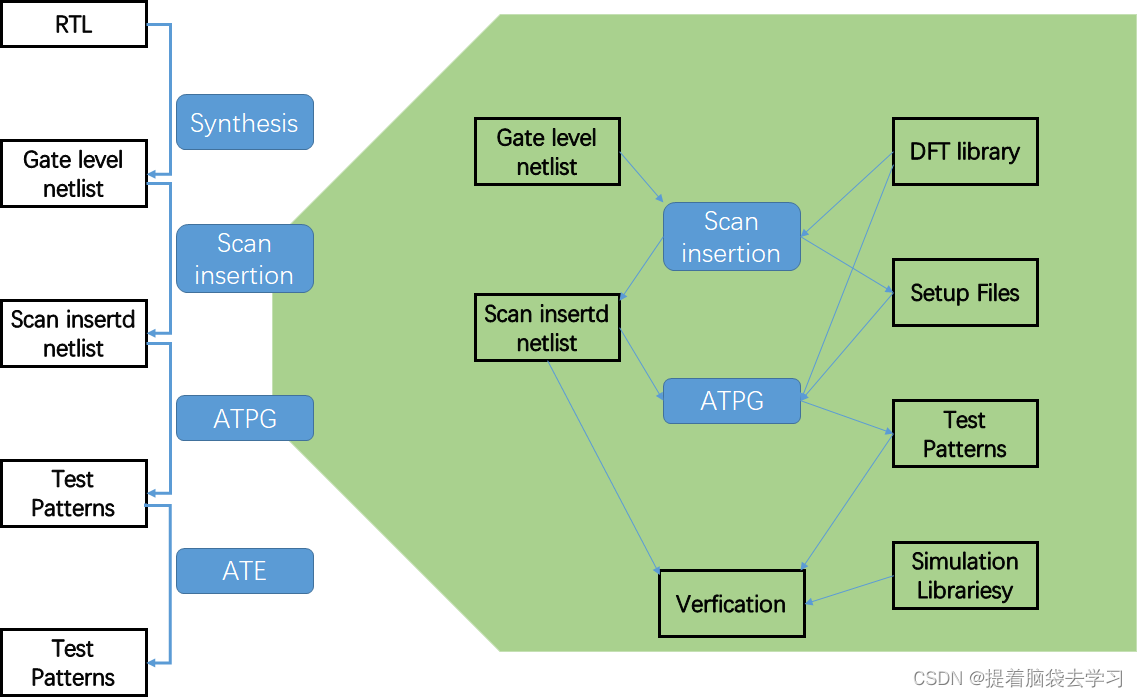

如图所示,scan 的插入是在综合之后进行的。由rtl到gate level 的netlist是通过synthesis步骤(如果是rc那么需要generic/map/opt,如果是dc只有一个syn)生成的gate level net通过scan insert 的方式进行scan chain的连接生成dft netlist,具体的操作可以在scan chain 如何形成去找。这个时候的net基本已经完成了rtl到网表的实现过程,后续就是给到后端团队做PR,后端团队拿到net 之后,会进行place &route,然后再交由signoff 团队进行STA 检查。PR团队相关的工作将在这个PR内容进行介绍。

另外还会给到DFT团队做atpg。如下图绿色框内容所示,是把scan insert和aptg展开进行 的解释。其中scan insert步骤是拿到gate level的netlist再加上DFT library可以实现为dft netlist。然后拿到dft netlist和DFT library以及一些setup file就可以进行ATPG操作,推向量然后仿真。

2. Scan insertion

2.1 DFT library

其实之前的内容有介绍过,如果要形成scan chain,就需要把普通的reg替换成scan reg,这个时候就需要保证替换完成的reg有相应的lib对应。如下图所示的情况,如果我们的design不需要做dft内容,那么只需要左侧的DFF即可,但是现在有了DFT,就需要增加右侧所示的SDF的model对应,二者是不同的cell 类型。那如何能保证我们所需要的dff可以成功替换成SDF呢,这个其实是可以靠工具实现的,在综合的map过程中,我们有相关的命令可以把dff修改成我们需求的SDF,但是这个是有前提的,就是我们已经读入了DFT reg 相关的library。现在的design中一般会把这两种reg的内容都做到同一个库里面,这样一起吃进来,那么综合时候只需要指定相关cell 类型即可。

2.2 scan insertion过程

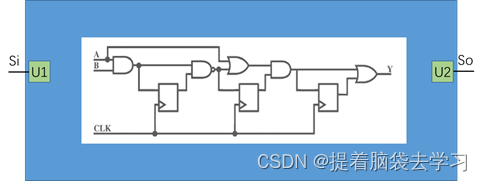

还拿这个DFF链来做实验,如下图所示是正常的map之后的设计,此时还没有正式的串链,而且此时的DFF还没有替换成scan的DFF。

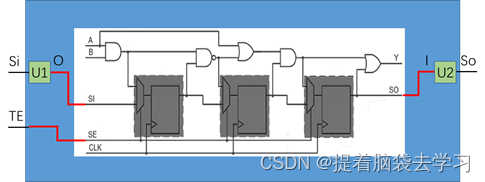

通过命令:> add_scan_pins chain1 U1/O U2/I > set_scan_enable –TEN TE > insert_test_logic –scan on –number 1- 1

- 2

- 3

就可以把相应的普通的DFF cell替换成SCAN DFF cell,并进行穿链,如下图所示为穿好链的一条chain。依次类推,对于design中存在的很多的reg,可以穿成很多的chain,可以通过工具进行自动的穿chain

另外在design中往往会有一个步骤:add test point/add test logic,这是因为在design中有些地方存在不可控的情况,比如一个reg的rst端口可能是悬空的,那么它默认就是X 态,这就是不可控的,这时候就需要增加test logic提高测试覆盖率。再者比如在测试不包含mem的dft时候,对于mem的一些interface 信号,比如地址/数据输入位,因为没有穿过mem所以没有办法测试到,因此可以增加test point点去观测它的准确性。

那么一条chain应该多长呢?由之前的知识知道,chain越长,那么需要shift的次数也就越多。对于测试时间来说越不友好。那chain越短越好么?也不是的,chain如果很短的话,就意味着需要chain的数量就越多,这就表明需要更多的pad来用。所以说,design中的chain一般都会进行规整和统一,一般chain会保持在一定的数量比如,200~300之间。edt 的引入其实有效的提高了我们测试的效率和能力,因为edt 的解压缩逻辑使得我们一个edt channel可以解压缩100+的chain,这样使得我们需求的pad数量大大减少,当然测试时间也会相应增加,但是相对来说的效果是更加好的。3. ATPG

ATPG全称auto pattern generated ,是在rtl逻辑插入完scan chain之后对scan chain进行的pattern的产生和仿真操作。主要分为SETUP/DRC check/ATPG config/Pattern gen等等。接下来详细介绍各个步骤

3.1 ATPG Setup

1) 首先需要一个scan inserted netlist,也就是上面说到的dft netlist ,通过read_verilog的方式把网表读入。设置好需要读入的dft library以及一些black box。

2) Constraint的设置,有些primary input需要在setup mode时候设置为常值。

3) 还需要有test procedure file,这个文件干什么用的,主要是定义design的test operation。在其他的内容有介绍过scan test的过程,也就是shift/capture的过程。Procedure file中主要包含三部分Test_Setup/Load_Unload/Capture

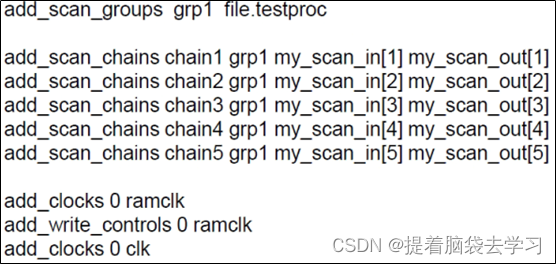

- dofile文件需要ready,dofile文件中包含了scan insertion 过程的一些setup信息,design的测试结构也就是链接了多少条chain,排列顺序,每条chain长等等相关信息都会放进去。另外还有一些clock和control 信号的定义等。如下图所示为一个示例

3.2 DRC check

Design rule 的check。其中包含很多RAM rules,clocks rules,data rules,edt rules等等。每一个rule都会被表示为一个简短的标识语句。比如clocks rule用C1表示。而关于违反clock rule中的情况又会分出来很多类。比如C1-1用来表示clock rule违反中的情况:clock都设置off state,但是依然有scan cell可以capture 数据的情况。依次类推C1-2, C1-3,D1-1等等有很多种情况

另外每一个violation都有不同的重要程度。有的可能是不能忍受的,必须解决掉,有些是需要check的,有些是需要了解的,有些事可以忽略的。这种用户可以通过命令对违反rule的情况进行设定:

set_drc_handling C1 error

set_drc_handling D3 warning

set_drc_handling P5 ignore3.3 ATPG config

对design中的blocks或者instance,设置add faults or nofaluts。这个是针对比如有些instance我们压根不需要测试,又或者其他的测试能够覆盖到这个instance,我们就会设置上add_nofault,这样就不会gen相关的pattern

设置明确的fault model,比如你需要gen stuck at pattern还是trans pattern又或者graybox的pattern等等。指定了stuck_at的pattern,就会产生0/1相关的一串串的测试pattern出来。3.4 Generate Patterns

当我们的设置和inputs数据都ready好,就可以真正的gen pattern了。

create_patterns命令,工具会解决一些drc问题,然后add all faults,当然除了你设置的add_nofault的那些。然后工具识别产生自认为最合适的向量出来。整个过程中,工具也会对pattern数量,coverage等等进行监测和打印。在gen pattern完成之后,可以通过write_pattern命令把pattern写出来。也可以把其他需求的内容写出来。 -

相关阅读:

【C++】C++11新特性

【编程100%】22-12 基本算法之 大整数截取

Linux检查端口nmap

网络安全(黑客)自学

计算机视觉——飞桨深度学习实战-深度学习网络模型

Node.js的基本使用(三)数据库与身份认证

《痞子衡嵌入式半月刊》 第 101 期

Tsinghua:Finding Skill Neurons in Pre-trained Transformer-based Language Models

手撕code

安全事件管理处置——操作实例

- 原文地址:https://blog.csdn.net/sinat_27691203/article/details/126739586