-

Tessent scan&ATPG(9) simulation mismatch(debug向量仿真问题)

了解在向量仿真时出现mismatch的原因;

了解parallel和serial pattern的特点

识别shift和capture的issue

识别仿真设置和建模的问题对仿真结果的影响什么是Simulation mismatch

ATPG 工具在生成pattern的时候 使用的是没有时序信息的模型;

使用testbench对向量进行仿真的目的是验证ATPG的期望值是否和仿真器的仿真值相同;

这种mismatch必须在pattern用于测试之前解决掉;模型抽取

并不是来自top level的所有功能模型都是需要的;

ATPG目的的模型抽取,会使得测试向量的生成变得容易.

ATPG模型和仿真模型的区别如下:

仿真模型除了有inverter的功能描述之外,还存在时序信息;

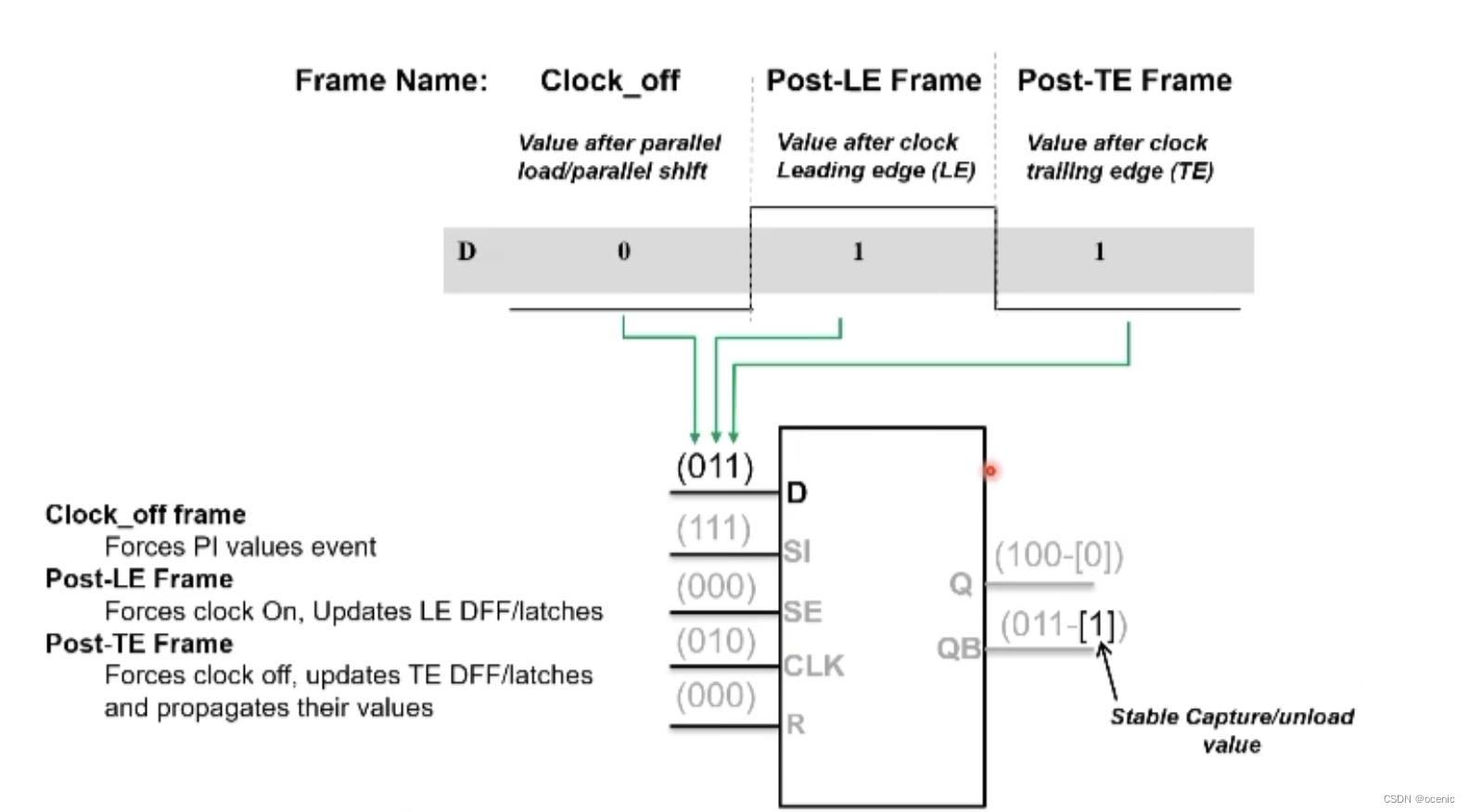

ATPG clock frames definition

XXX-[X] 最后一位为capture到的稳定值或者 unload 的值;如果设置了multi-cycle path 或者做了ATPG的constrains [X]为期望值不一定是这个单元capture的值.

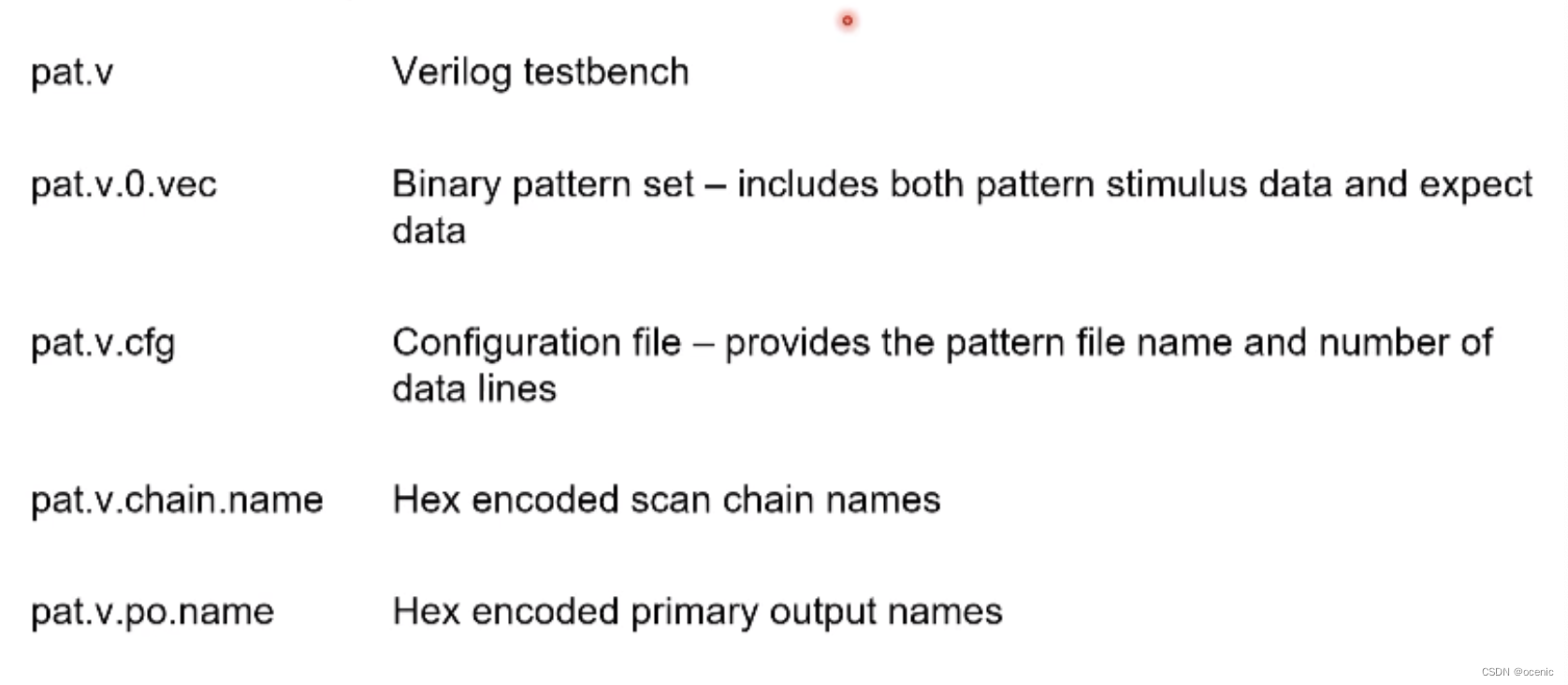

tessent shell生成verilog testbench

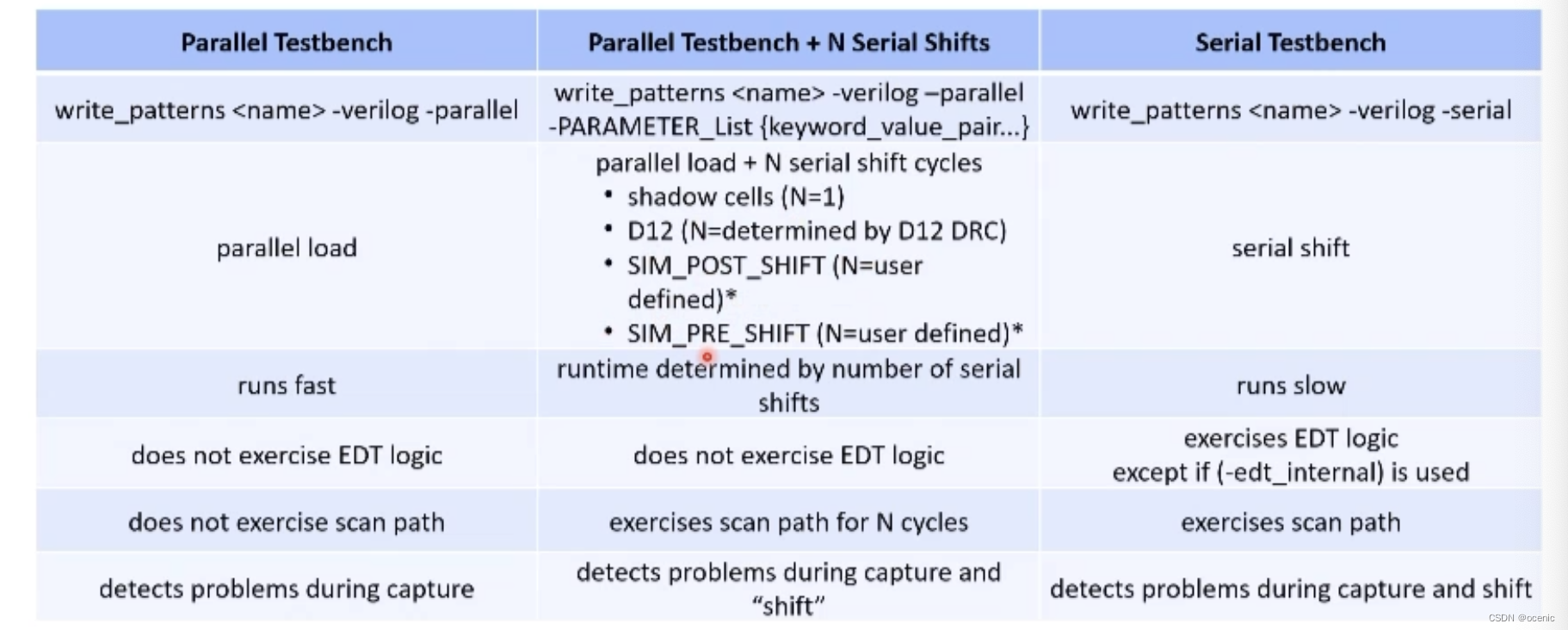

工具能够生成两种类型的verilog testbenches;

- parallel

write_pattern-verilog -parallel - 1

- serial

write_pattern-verilog -serial - 1

使用parameter file控制和报告参数能帮助debug mismatches

write_pattern-Parameter_file / -Parameter_list #这些参数可以: #创建指定的debug waveform #修改 parallel testbench的delay #在parallel testbench中应用串行shift #记录mismatch的信息等 - 1

- 2

- 3

- 4

- 5

- 6

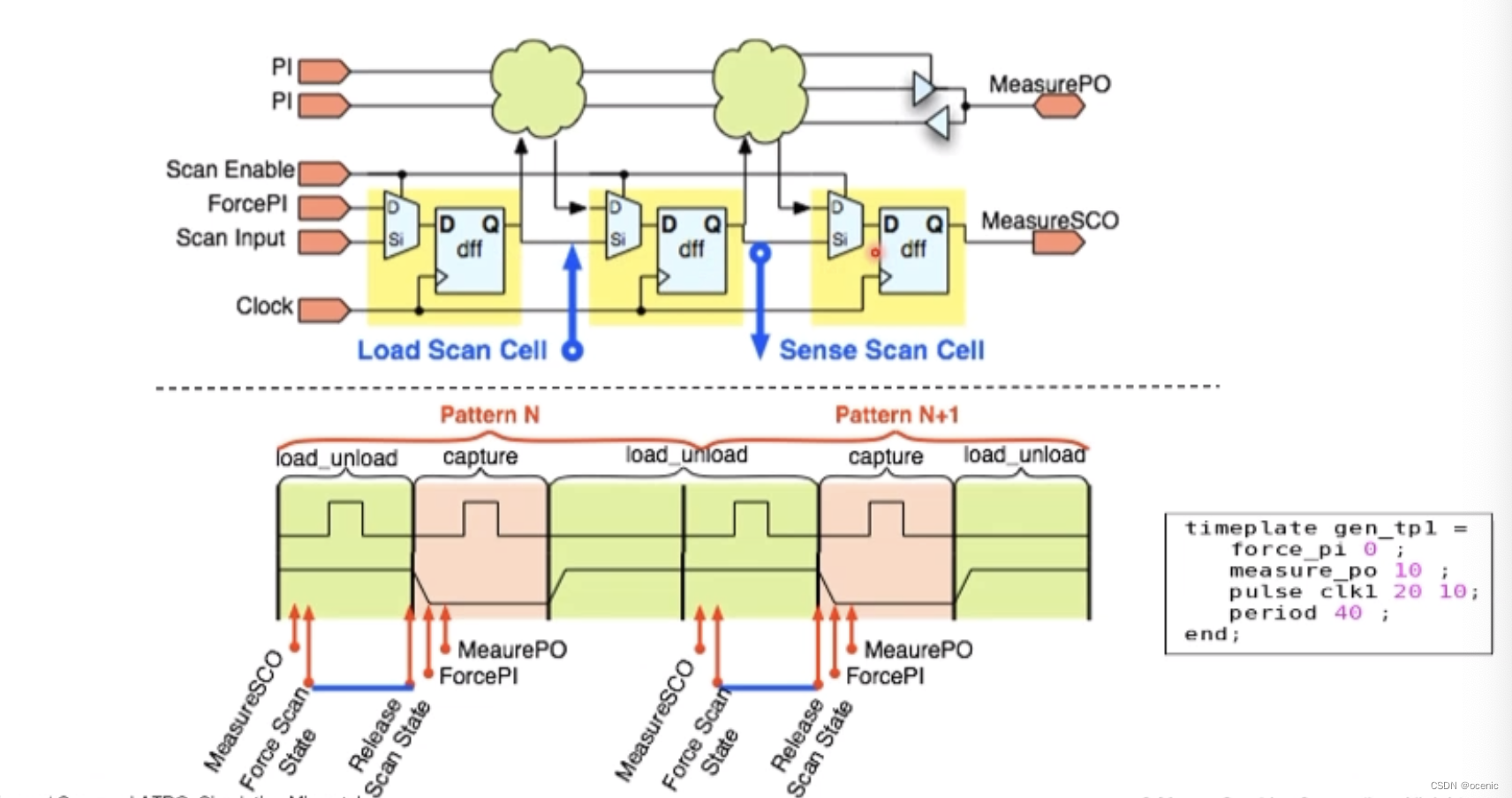

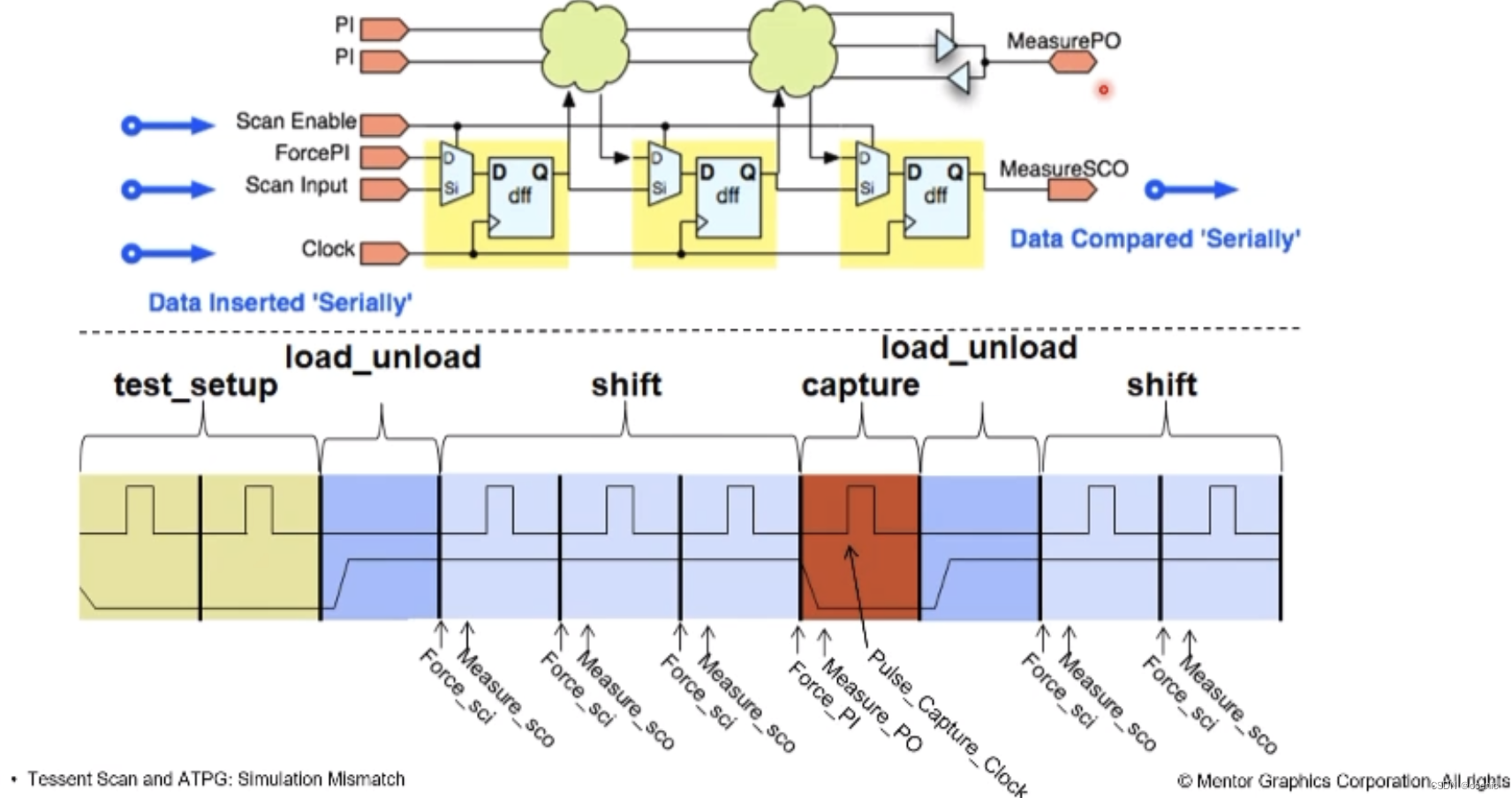

parallel和serial testbench的区别

parallel:

强制所有的scan flops从scan input pin 并行输入;

所以仅有单个并行shift cycle

可以大大减少仿真时间和debug的难度;

仅能发现 capture cycle的mismatch

serial:

数据是有扫描链的scan input端串行输入到 scan cell之中(和实际的测试条件一致);

shift cycle 的长度取决于最长的扫描链,且 EDT逻辑的load cycle 也会延长仿真时间.

只有被观测的扫描输出引脚可以被报告;

仿真时间也会很长,特别是在做后仿的时候;

能发现存在于 shift cycle和capture cycle的问题;

所以为了发现和debug simulation mismatches;建议首先进行parallel testbench的仿真 detect parallel shift的问题和capture的问题;

其次使用 parallel with N shift 去detect serial shift和parallel shift的问题 以及capture的问题;

再次使用 bypass EDT的serial testbench去detect serial shift的问题以及capture的问题;使用EDT 的serial testbench去附加detect EDT裸机的问题;verilog testbench文件包含

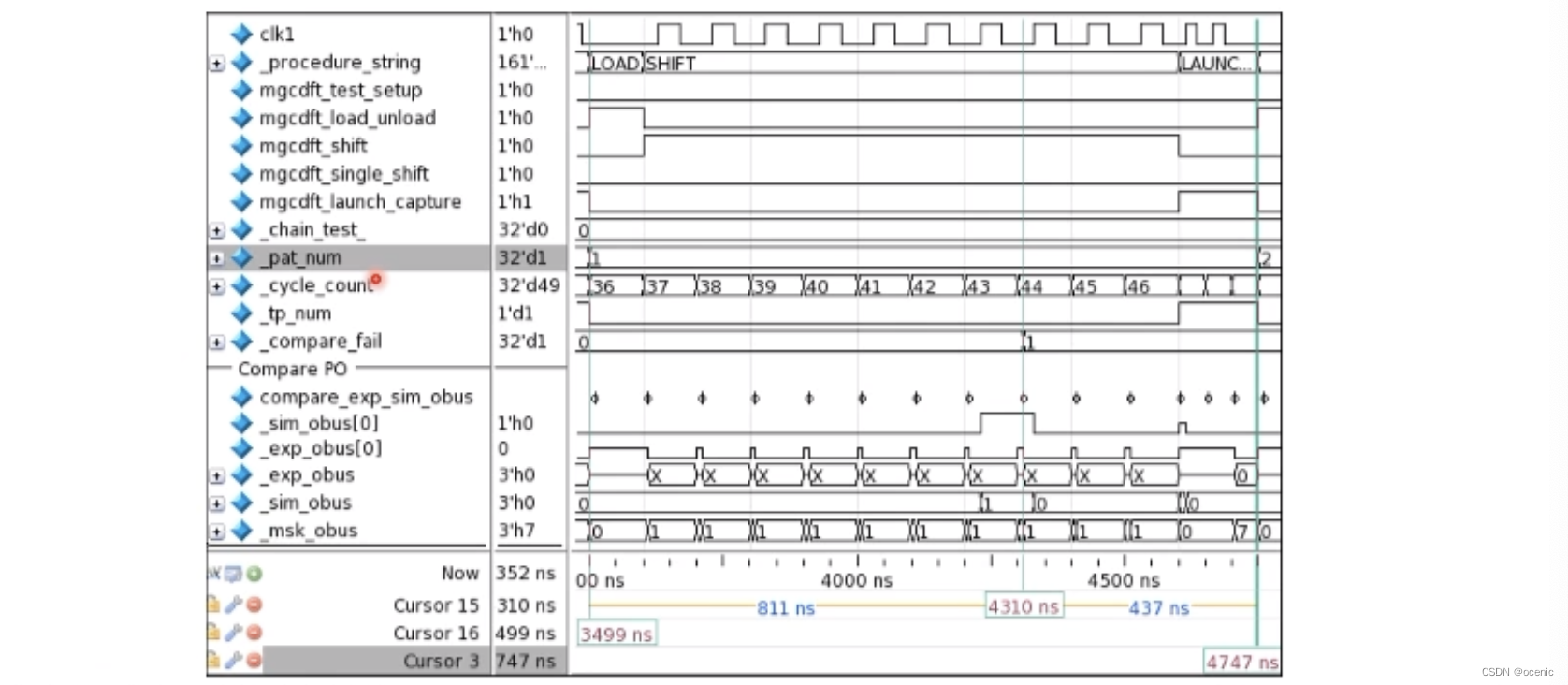

parameter:SIM_VECTYPE_SIGNAL

这个参数会向waveform中添加一些关于test pattern的信息;如 pattern number 和cycle number等

判断mismatch 发生的位置

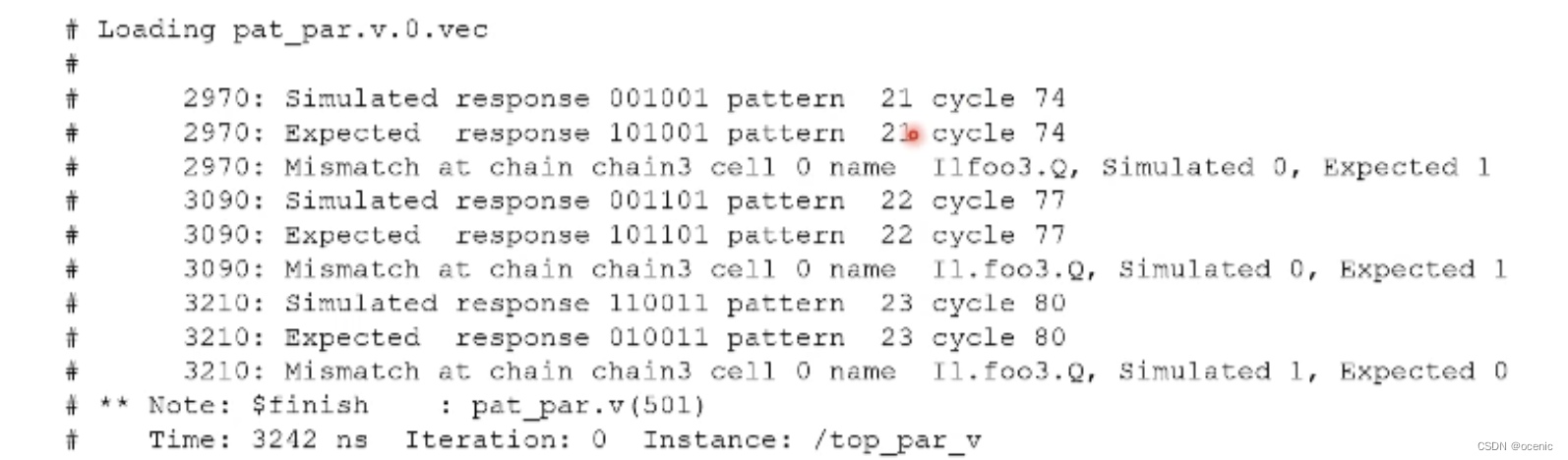

跑testbench ,simulation mismatch会像如下报告:

#设置pattern的类型 set_context pattern -scan #读取扁平设计 read_flat_model#读取pattern数据 read_patterns #加parameter,将pattern的ID set_get_report pattern -external #报告 report_scan_cells -display hierarchical_schematic - 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

Trace back(追溯)

定位是哪个pattern 哪个register,可以使用Tessent visualizer和波形去追溯;

确定造成问题的原因: 60%的问题是由timing不满足造成,35%由CCD/NCP 和internal pins造成(内部时钟,不正确的时钟,内部pin不正确的value定义),2%由DRC(C6,T24,D1,K)造成,2%由工具不正确的setting造成;1%由初始化设计方案有关;timing

时序上的问题分下面几个方面:

- clock skew; serial pattern仿真中存在多个失败的shift cycle就很有可能是clock skew的原因;flop的输出位X态且报告setup/hold的违例;数据变化且flop capture到新的数据这种情况都可以考虑是否为clock skew的原因;

- Zero delay; 反标没标好,或者约束不完整,导致一些逻辑行为立刻发生,比如clock skew 就不该为0延迟;前后两级flop的时钟是不能同时toggle的;

- parallel shift cycle(时序违例) parallel force太靠近clock pulse 导致setup的违例,parallel release 太靠近clock pulse导致hold违例;parallel release 太靠近下一个 clock pulse导致setup的违例;

- 小故障, 时钟 set/reset存在问题;具体啥问题不清楚;

- false 和multi-cycle path;

CCD/NCP & internal pins

CCD(clock control definition)

NCP(named clock procedure)

问题分以下几个方面:- clock pulses(在 sim中有clock pulse 在ATPG的时候没有 反之亦然,或者clock pulse在不正确的cycle);

- reference clock;(reference clock没有pulse,reference clock在不正确的时间pulse);

- CCD/NCP(在CCD和NCP中错误的条件描述);

- 追溯问题到了黑盒的内部引脚;

pattern Masking

对于一些mismatch, 逻辑中确有这种情况,或者ATPG存在overtest的情况; 知道原因不可解决,可以通过添加Pattern Mask的方法进行解决;

#通过 re-simulation的放置创建mask pattern; #那些需要约束为观测X 或者OX的可以通过re-simulation的方式解决; set_system_mode analysis read_patterns pat_ascii.gz add_cell_constraints chain1 7 OX add_flaults -all simulate_patterns -source external -store_patterns all report_statistics write_patterns <>- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

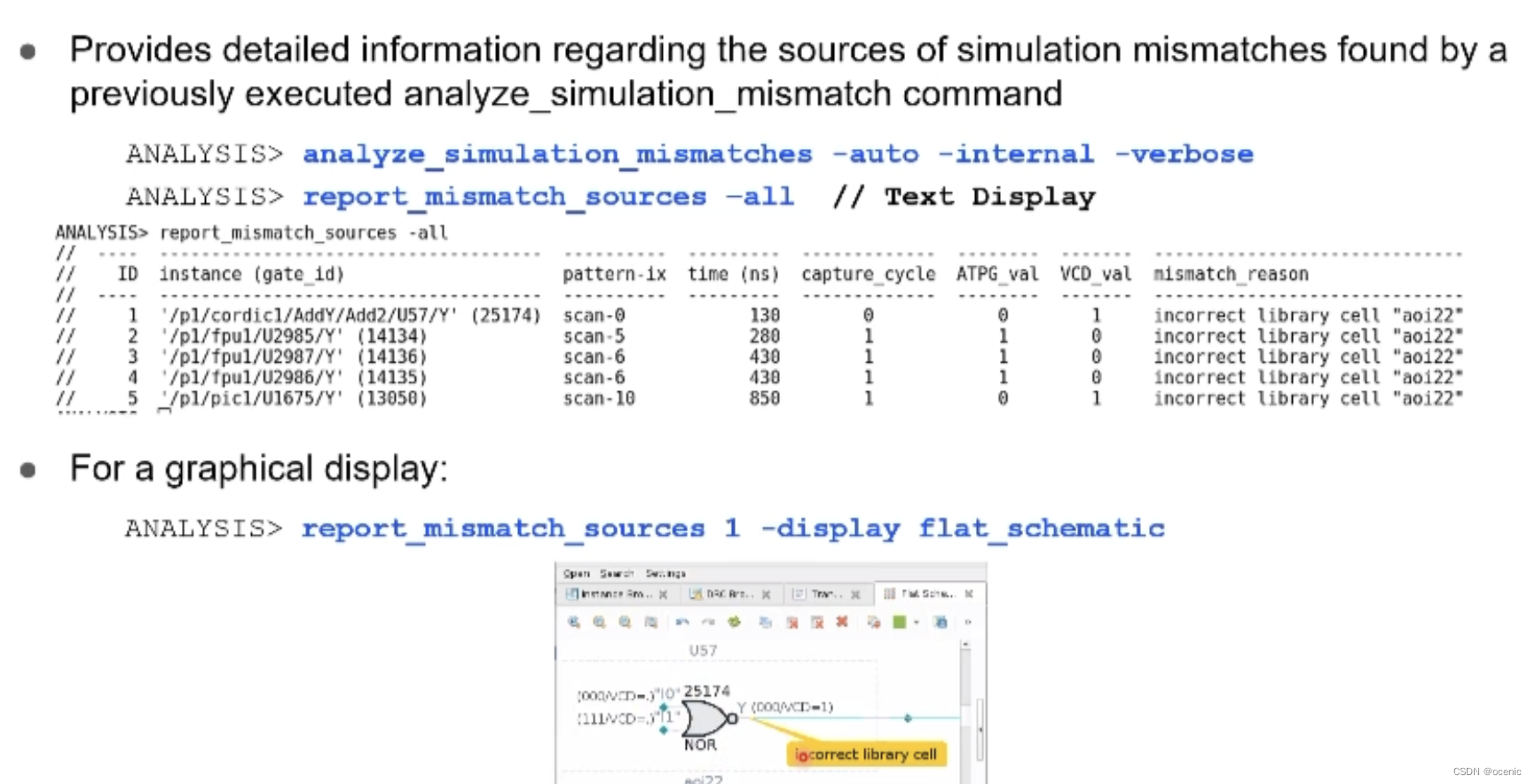

Auto simulation

-

相关阅读:

IDEA修改jvm内存

吃透Chisel语言.20.Chisel组合电路(二)——Chisel编码器与解码器实现

ENVI_常用扩展工具名

ThreadLocal使用及原理

9 HDFS架构剖析

Redis运行为什么快

SSM整合(详解)

【Javadoc生成开发文档(Terminal或IDEA中)】

如何查看SAP版本及HANA版本?

CTF-反序列化

- 原文地址:https://blog.csdn.net/weixin_41464428/article/details/126720378