-

SCAN BASIC --- PARTII scan test

本章节对scan进行一个比较简要的介绍。

1. Scan test

1.1 什么是可测试性

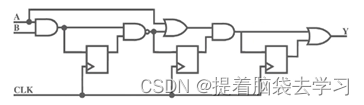

其实就是可控制性和可观察性。首先可控制性,指的是我可以控制我的逻辑的值的灌入,也就是激励的灌入。可观测性,就是可以通过灌入的激励得到一些值,从这些值可以判断出来我的逻辑有没有问题。如下图所示的正常的逻辑,当我们AB给激励的时候,寄存器必须经过时钟翻转才能把数据朝后面传递,这是一个clock domain,design里面那么多的clock domain,用哪个时钟去翻转寄存器呢?打多少拍才能把激励送到所有的寄存器呢?如何通过激励就能判断是寄存器出现问题了还是组合逻辑出现问题了呢?但从下面的连接方式上,很难看出来。那如何解决呢,就要用到下一个小节的扫描链测试。

1.2 扫描链测试

实际上scan test是一个比较复杂的流程,并不是简单的一开一关的操作,它包含如下内容:

1) 通过把普通的flip-flop替换为专用的scan cell

2) 把scan flops穿在一起组成scan chains

3) 通过送激励和观测结果来判断逻辑中是否存在问题1.2.1 scan cell

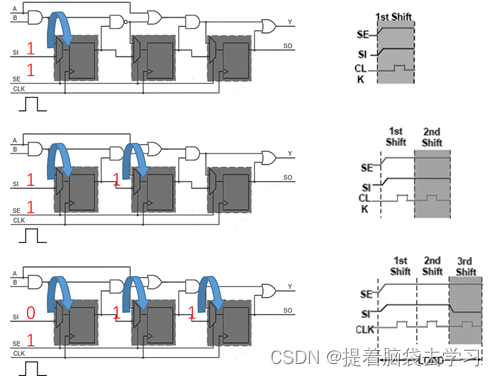

如下图所示为普通FF替换为scan cell。相比于普通的flops,scan cell在D端口增加了一个mux,由SE控制,SE取决于是否进行scan chain的scan操作。D端口为正常的连接逻辑功能的端口,SI为扫描链寄存器之间的连接端口。当SE为1时候,扫描链进行扫描,数据通过寄存器SI到Q一拍一拍朝后传,SE为0时候,SI无效,D端口正常从逻辑上捕获数据。

1.2.2 穿chain

如下图所示,把scan cell相应的SI端口前后连接起来,组成一条scan chain。下图中只展示了chain 长度为3 的一条,实际的design中,scan chain的长度会控制在100以上,当然也不会太长。之所以不能太短是因为,chain太短就需要非常多的chain条数,这样就需要好很多的激励,这样就需要很多的pad口,而design中往往pad数量是有限的。Chain之所以不能太长是因为如果chain太长,那么我们一拍一拍朝里面灌激励就会用很久的时间,对于测试不友好。另外edt的引入也需要我们的chain不需要太长,影响压缩的效果。这样以来,所有的dff都可以通过一个clk来控制,那么通过这一个频率的clock上进行数据的shift就好很多了。

1.2.3 Base Scan test flow

Basic scan test 包含几个步骤:

1) load scan chain(cycle数取决于最长的chain的长度,所以说一般design设计中我们会设置一个chain 长的最大范围值,保证整个design差别不是太大)如下所示。当scan test setup之后就可以开始scan chain的load了。首先force SE=1,然后依次force SI 101,同时pulse shift clock。这样101数据就会依然传入三个寄存器中,如下所示。在最后一个pulse

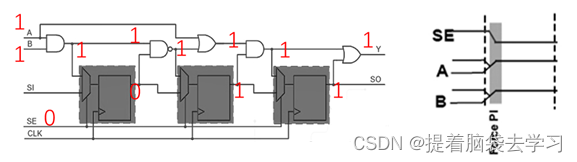

2) Force primary inputs (PI),对输入端口进行激励的灌入

由第一步知道,寄存器的值已经灌进去了,现在把SE置位0,此时scan cell中的mux就会走D端而不走SI端,但是这个时候没有clk的pulse,因此所有的值都是固定的不动的。此时force A/B均为1值,那么逻辑中的所有的值都是可以预测的,如下图所示

3) Measure primary output(PO),对输出端口进行测量如2)所示,可以预测到Y端口的值为1

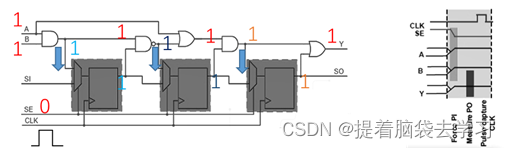

4) Pulse capture clock,捕获逻辑数据

如下图所示,此时SE依然是0,SI端口无数据,此时进行clk pulse,就会使得D端口的逻辑传递到DFF的q端口,如下所示,对应不同颜色的值为传递方向。此时D端口刷新了新的数据。怎么判断这些刷新的数据没有问题呢,需要下个步骤

5) Unload value from scan cells(load next pattern)

此时SE又设置为1,SI有效,D端口无效。这一步就是把寄存器的数据从SO一个个的unload出来,同时会在SI端口force新的pattern。上个步骤说到寄存器的值进行了刷新,这一步就可以对刷新的寄存器进行一个读的比较看寄存器是否有问题。这样多个pattern就可以依次进行测试了。重复了步骤1) -

相关阅读:

介绍一款特别好用的java反编译工具jd-gui

容器安全之镜像扫描

05 pyecharts 基本图表(示例代码+效果图)

C++ Qt 学习(八):Qt 绘图技术与图形视图

【soar-w5学习和使用】

vue 时间戳转日期格式

(附源码)ssm基于SSM的南昌旅游网站管理系统设计与实现 毕业设计 101407

MAC MINI 2012安装Montery折腾笔记

第五章Maven依赖的特性-进阶篇

【vue+nestjs】qq第三方授权登录【超详细】

- 原文地址:https://blog.csdn.net/sinat_27691203/article/details/126612062