-

以太网PHY原理介绍

一、以太网分层模型

基于 OSI 七层网络模型, 车载以太网的网络拓扑结构如图1-1所示。

图1-1 车载以太网网络拓扑结构图

从图中可以看到位于 Layer1 和 Layer2 的为物理层和数据链路层。 Layer3 以上各层包含了 TCP/IP、 DOIP、SomeIP 等协议, 由 EthStack 软件包实现。

物理层由 PHY 和以太网连接线构成; 数据链路层也就是常说的 MAC, 通常作为 MCU 内嵌的功能模块。 通过MII 接口可以建立 PHY 和 MAC 间的通讯, MII 接口支持多种模式, 如 MII/RMII/SMII/GMII/RGMII 等,这里主要介绍下 MII、 RMII 和 GMII 接口。二、MII接口

MII 接口示意图如图 1-2 所示,共有 16 根信号线。

图1-2 MII 接口示意图

- TXD/RXD 为数据发送/接收信号, 分别有四根信号线;

- TXER 为发送数据错误信号, 同步于 TX_CLK,高电平有效,当 TX_ER 拉高时表示传输数据无效;

- RXER 为接收数据错误信号, 同步于 RX_CLK,高电平有效,当 RX_ER 拉高时表示传输数据无效;

- TX_EN 为发送使能信号,只有在 TX_EN 有效期内传的数据才有效;

- RX_DV 为接收使能信号,只有在 RX_DV 有效期内传的数据才有效;

- TX_CLK 为发送参考时钟, 由 PHY 提供,当传输速率为 100Mbps 时, TX_CLK 频率为25MHz;当传输速率为 10Mbps 时, TX_CLK 频率为 2.5MHz;

- RX_CLK 为接收参考时钟, 由 PHY 提供,当传输速率为 100Mbps 时, RX_CLK 频率25MHz;当传输速率为 10Mbps 时, RX_CLK 频率为 2.5MHz;

- CRS (Carrier Sense) 为载波侦测信号, 只要数据传输, CRS 即有效,在发送和接收均空闲时撤销; CRS仅在以太网工作在半双工模式下生效;

- COL (Collision Detected) 为冲突检测信号, 由 PHY 提供,表示介质检测到了冲突状态, COL 仅在以太网工作在半双工模式下生效

MII 发送时序图如图1-3 所示

图1-3 MII 发送时序图

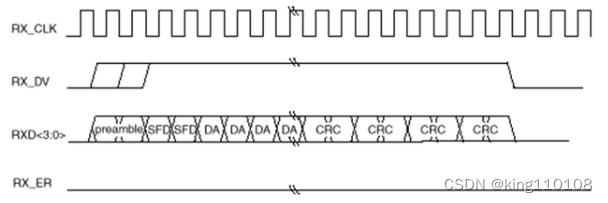

MII 接收时序图如图1-4 所示

图1-4 MII 接收时序图

1. RMII 接口

RMII 接口示意图如图 1-5所示,共有 8 根信号线。 RMII 为 MII 的简化版,信号线数量减半。

图1-5 RMII 接口示意图

- TXD/RXD 为数据发送/接收信号,分别有两根信号线, 为 MII 的一半;

- TX_EN 同 MII 一致;

- RX_ER 同 MII 一致;

- CLK_REF 为 50MHz 参考时钟, 可以由 PHY 提供,也可以由 MAC 提供;

- CRS_DV 为 CRS 与 RX_DV 联合的信号。

2. GMII 接口

GMII 接口示意图如图 1-6 所示, 共有 24 根信号线。相比于 MII, GMII 可支持千兆速率传输, 通常 GMII 接口可以兼容 MII 接口。

图1-6 GMII 接口示意图

GMII 大部分信号线与 MII 一致,区别在于:- TX_CLK 发送参考时钟由 MAC 提供, RX_CLK 接收参考时钟由 PHY 提供,两者均为 125MHz;

- TXD/RXD 发送/接收数据信号分别为 8 根信号线,为 MII 的两倍。

3. MDIO 接口

MII接口除了上述的发送/接收数据、 状态指示信号外,还包含了MAC与PHY间用于状态管理的接口,由MDIO和 MDC 两根信号线组成, MAC 通过 MDIO 接口可以对 PHY 的寄存器进行读写操作。 MDIO 通讯有两种规范,分为 IEEE 802.2 Clause22 和 Clause45, Clause45 向前兼容 Clause22。

MDIO Clause22 的写时序图如图 1-7 所示

图1-7 MDIO Clause22 的写时序图

- PRE 为帧前导码,由 32 个连续的 bit 1 构成;

- ST 为帧开始标志, Clause22 的开始标志为“01”;

- OP 为操作码, “01”表示写操作, “10”表示读操作;

- PHYAD 表示 PHY 的物理地址, 共 5 个 bit,每个 PHY 都会先将这 5 个 bit 与自己的地址进行比较,若匹配一致再进行后面的操作,若不一致,则忽略后面的数据;

- REGAD 表示 PHY 的寄存器地址;

- TA 为状态转换域, 当为读操作时, TA 第一个 bit 为高阻态, 第二个 bit 由 PHY 将其置为“0”; 当为写操作时, TA 由 MAC 控制,直接为“10”;

- DATA 为寄存器的数据,共 16bit, 当为读操作时, 由 PHY 提供;当为写操作时, 由 MAC 提供;

- IDLE 为帧空闲状态, MDIO 处于高阻态

MDIO Clause45 的写时序图如图 1-8 所示

图1-8 MDIO Clause45 的写时序图

- PRE 为帧前导码,由 32 个连续的 bit 1 构成;

- ST 为帧开始标志, Clause45 的开始标志为“00”;

- OP 为操作码,分为 4 种状态, 比特“00”表示设置当前寄存器地址,比特“01”表示写当前寄存器。比特“10”表示读当前寄存器,比特“11”表示读当前寄存器读完后把当前寄存器的值加 1,用于顺序读;

- PRTAD 为端口地址, 即 PHY 的物理地址;

- DEVAD为器件地址, 共5个bit, 为Clause45新增, 目前包含00000(Reserved)、 00001(PMD/PMA) 、00010(WIS) 、 00011(PCS) 、 00100(PHY XS) 、 00101(DTE XS) ;

- TA 为状态转换域;

- REGAD / DATA, 当 OP 为“00”时, TA 后面的 16 个 bit 表示 REGAD, 为 PHY 的寄存器地址; 当 OP 不为“00”时, TA 后面的 16个 bit 表示 DATA,为寄存器数据, 当为读操作时, 由 PHY 提供;当为写操作时, 由 MAC 提供;

- IDLE 为帧空闲状态, MDIO 处于高阻态。

Clause22 与 Clause45 的主要区别在于: Clause22 一帧报文包含了 PHYAD、 REGAD 和 DATA,而 Clause45将 REGAD 和 DATA 分为 2 帧传输,从而扩展了可支持寄存器的数量。

-

相关阅读:

Python+OpenCV实用案例应用教程:安装OpenCV

【Linux】进程地址空间

Zookeeper 集群的应用场景

一个项目应对各式各样环境-profile完美应付

Redis 内存管理

自动化测试的生命周期是什么?

opencv中的仿射变换

《第一行代码》核心知识点:Android简介

FDCAN硬件过滤器详解

如何设定员工满意度调研的维度?

- 原文地址:https://blog.csdn.net/king110108/article/details/126575631