-

STA series --- 8.Timing Verification (PARTII)

本篇内容,基于阅读J. Bhasker • Rakesh Chadha著作《Static Timing Analysis for Nanometer Designs》后进行的总结以及自己的观点和感想,如有不正确的地方,还请指点。读者有微电子基础将更好理解内容。(图片内容绝大部分直接引用书中)

本章节介绍STA check中各种timing相关的check。本节主要介绍false path/半周期检查/recovery/removeal check

前面有做过介绍,timing path一共分为4类,i2reg, reg2reg, reg2o,i2o,其中大量的检查应该是reg2reg。对于reg2reg的timing检查项又分为很多种,其中setup/hold check最为常见。

3. false path

在STA中,只要存在timing arc ,且相应的clock有正常流过,那么就会有timing path ,但是有些timing不是我们期望看的,比如可能是跨clock domain的。可能刚好因为满足timing check的必备条件,因此有了这条path,但又有很大的vio。这个时候可以通过false path的形式给拿掉。设置false path可以有多种方法,clk和clk之间设置,CK到D端设置,到reg设置,through某个cell/pin的设置。Through这个选项用的时候是需要谨慎的,因为一旦thr了某个pin/cell设置了false path,那么经过这个cell/pin的所有的timing都不会检查。False path的设定,一方面可以减少不必要的timing优化,另一方面,减少eco的effort

set_false_path –from CLK1 –to CLK2 set_false_path –from reg1/CK –to reg2/D- 1

- 2

4. 半周期路径

所谓半周期的路径,起始就是半周期检查,对应的是前后两个reg的CK端口clock反相的情况。这种也分为两种情况,一种是正沿触发reg到负沿触发reg,另一个则相反。

4.1 沿触发到负沿触发

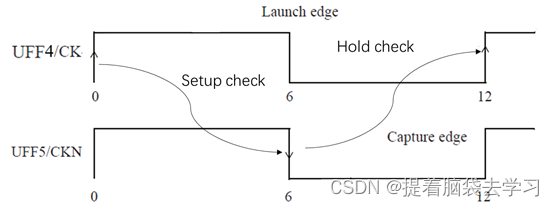

如上图所示,红色框框内,UFF4到UFF5为正沿触发到负沿触发的check,对应的波形如下图所示。Setup check,launch clock起始点为0,capture clock起始点为6,这个时候setup check有6ns的时间要求。对于hold,capture沿理论上应该是setup 沿超前挪一个周期,但是这样就挪出了波形,同理可以把launch clock朝后挪一个周期,因此launch clock起始点为12ns,capture clock为6ns。

4.2 负沿到正沿触发

本节第一张图中的绿色框框,对应负沿到正沿触发的check,对应的波形如下图所示

关于setup/hold的分析方式和正沿到负沿类似。对于setup,launch clock起始位置6ns,capture clock位置12ns。对于hold来说,launch clock起始位置为6ns,capture clock位置为0ns。

从timing上来看,这样的timing无论是对setup还是对于hold都有很好的裕度,能够较好的保证STA。关于这种半周期的检查,遇到比较多的情况如下:

1) 对于scan chain中跨clock domain的情况,往往会在chain中间插入负沿的latch(前提是chain上reg都是正沿触发,一般都是这样)从而防止跨clock domain的reg原本skew太大导致hold出现问题。

2) 另外对于design输出端口的reg,往往也期望是一个负沿的reg,因为这样到另一个design时候,就会是负沿到正沿的reg的check,这样hold天然满足了。5 Recovery/Removal timing check

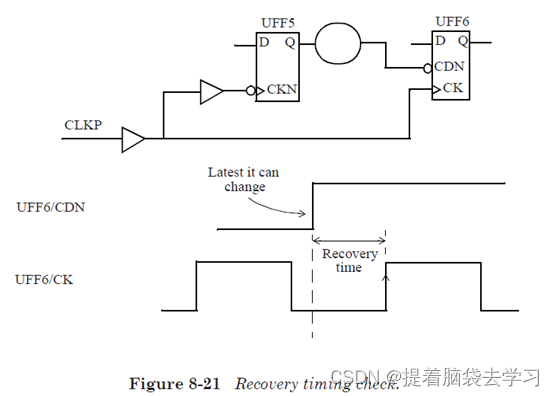

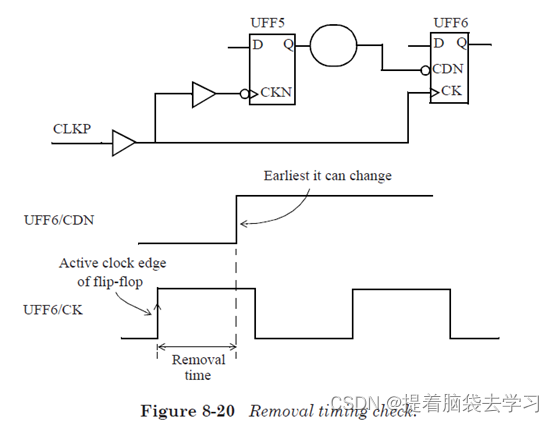

无论是recovery还是removal,都是异步信号的无效时刻和有效时钟沿之间的关系检查。比如recovery代表在有效时钟沿来之前多久,允许reset信号变得无效,如果rst信号变无效与时钟沿来离得很近,那么可能这个时钟沿不会起作用。同理,removal指的是时钟沿来之后多久,rst才可以便无效。因为如果时钟沿来之后,立马reset变无效了,本身不期待起作用的时钟沿,可能起作用了。总结一下,recovery期望时钟沿能正常起作用,不受rst变无效的时刻影响,removal期望时钟沿能正常不起作用,不受rst便无效的时刻影响。接下来详细解释。

5.1 Recovery timing check

Recovery timing check和setup timing check非常类似,只不过setup check是在上升沿来之前要求数据就要到达,recovery check是上升沿来之前要求rst无效信号要到达。相应的recovery time在lib里面都有对应的描述

5.2 Removal timing check

Remove check和hold check非常类似,后者要求上升沿有效之后,数据保持一定的时间才能发生变化,前者要求上升沿有效之后,rst信号保持一段时间才可以变得无效。

-

相关阅读:

Ubuntu安装docker及docker-compose

SpringBoot基础(九)-- 配置文件优先级

机器人视觉教学实训平台

C++智能指针,强制类型转换

LeetCode —— 复写零(双指针)

【数据结构】查找算法和堆栈的应用

Maglev: 一种快速可靠的负载均衡器

Oracle数据库如何定位trace file位置

静态代码块Vs构造代码块

2022年11月24日 复习指针与数组练习

- 原文地址:https://blog.csdn.net/sinat_27691203/article/details/126422981