-

Lecture 14 IO System(IO系统)

1 I/O硬件

1.1 硬件概念

- BUS

总线:⼀组线路和通过线路传输信息的⼀个协议。有两种:

- 并⾏:Multiple Lane

- 串⾏:Single Lane

任何⼀个微处理器都要与⼀定数量的部件或外围设备连接,但如果将各部件和每⼀个外围设备分别⽤

⼀组线路与CPU直接连接,那么连线会错综复杂,甚⾄难以实现。为了简化硬件电路设计、简化系统

结构,常⽤⼀组线路,配置以适当的接⼝电路,与各部件和外围设备连接,这组共⽤的连接线路被称

为总线。

从⼴义上说,计算机通信⽅式分为并⾏通信和串⾏通信,相应的通信总线被称为并⾏总线和串⾏总

线。并⾏通信速度快,实时性好,但是由于占⽤的⼝线多,不适合⼩型化产品;⽽串⾏通信效率虽

低,但在数据通信吞吐量不是很⼤的微处理电路中显得更加简易、⽅便、灵活。- PERIPHERALS COMPONENT INTERCONNECT

PCI总线(Peripheral Component Interconnect,外部设备互联)由Intel公司提出,

其主要功能是连接外部设备;北桥,南桥是主板上芯⽚组中最重要的两块,它们都是总线控制器。南桥主要是负责IO,北桥⽤于

CPU和内存、显卡、PCI交换数据。随着集成技术的不断发展,北桥被继承到了CPU⾥⾯,那么南桥要承担⼀部分北桥的功能,然后合成

到了 Platform Controller Hub- 设备类型

- 块设备(block device)

◦ 存取单位是⼀个block

◦ 如磁盘、磁带、DVD等 - 字符设备(character device)

◦ 存取单位是⼀个字符

◦ 如显⽰器、键盘、⿏标等

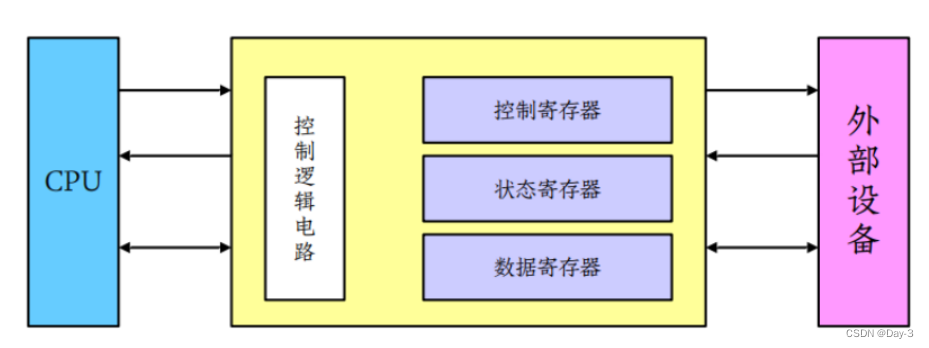

1.2 CONTROLLER

◦ 控制器是可以操作端⼝、总线或设备的电⼦设备的集合。

◦ 串⾏端⼝控制器是⼀个简单的设备控制器。 它是计算机中的单个芯⽚(或芯⽚的⼀部分),⽤

于控制串⾏端⼝线路上的信号

◦ SCSI 总线控制器并不简单,因为 SCSI 协议很复杂。 它通常包含⼀个处理器、微码和⼀些私有

内存,以使其能够处理 SCSI 协议消息

◦ 有些设备有⾃⼰的内置控制器。 您将看到连接到磁盘驱动器⼀侧的电路板。 该板是磁盘控制

器。 它为某种连接实现协议的磁盘端⸺例如 SCSI 或串⾏⾼级技术附件 (SATA)。 它有微码和处

理器来执⾏许多任务,例如坏扇区映射、预取、缓冲和缓存。

cpu⽆法直接控制io设备的机械部件,因此io设备还要⼀个电⼦部件作为cpu和io设备机械部件之间

通信的桥梁,⽤于实现cpu对设备的控制。我们就称这个部件为

io控制器。

如何对控制器分布命令

•控制器有⼀个或多个⽤于数据和控制信号的寄存器。CPU通过读写这些寄存器来控制通信。

◦ 控制寄存器:可以被主机发布命令或改变设备状态

◦ 状态寄存器:包含⼀些主机可读的位信息

◦ 数据寄存器:记录主机可读或写⼊的数据

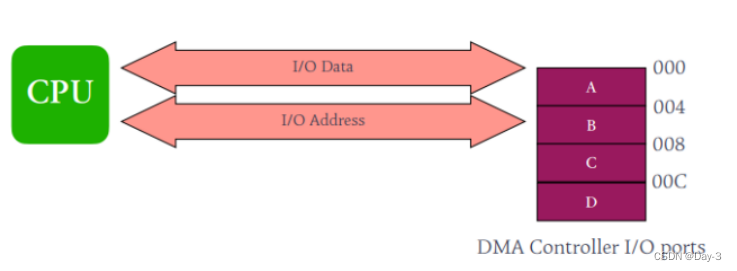

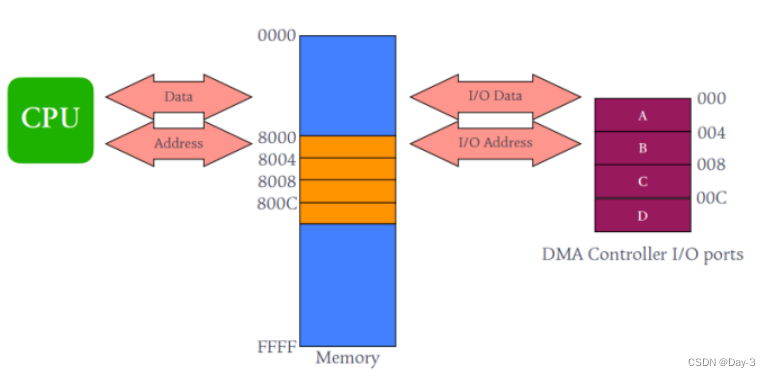

I/O地址•I/O地址:控制寄存器地址 •编址⽅式

◦ I/O独⽴编址:使⽤独⽴的I/O指令,如IN、OUT;

◦ 内存映射编址:划出⼀块内存地址,将I/O的端⼝地址映射进来,这样就

可以使⽤访问内存指令对控制寄器进⾏读写

2 I/O控制⽅式

2.1 轮询

步骤

◦ 重复测试busy位,直到清零;

◦ 设置控制寄存器为write操作,并将要写⼊的字节X存⼊数据寄存器;

◦ 设置ready位

◦ 若ready位为1,则设置busy位

◦ 执⾏write命令,将字节X写⼊设备

◦ 清除ready位和busy位3 内核I/O结构

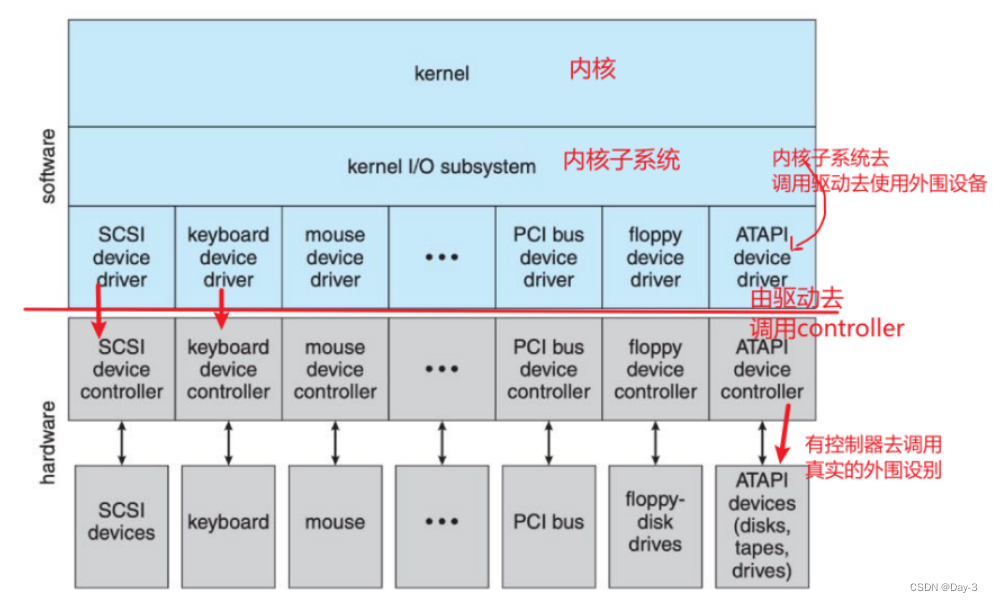

内核I/O结构包括I/O硬件和I/O软件两个部分,I/O软件的设计⽬标主要体现在:

•⾼效率(efficiency):通过⼀些⼿段提⾼I/O设备的访问效率。

•通⽤性(generality):屏蔽硬件细节,让⽤⼾使⽤统⼀的接⼝⽅便地使⽤不同的硬件

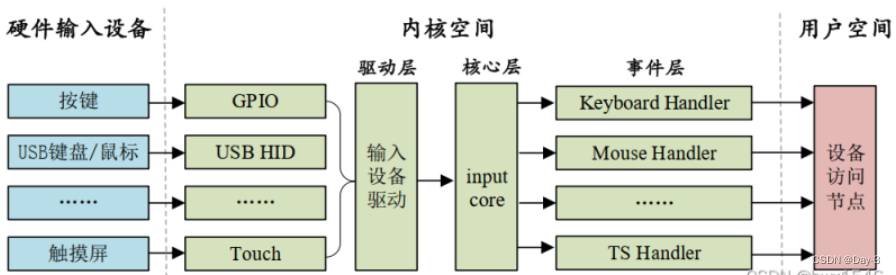

3.1 设备驱动层

设备驱动层通过隐藏设备控制器之间的差异,使 I/O ⼦系统独⽴于硬件我们结合IO结构图看,不同的IO设备有不同的驱动,⽐如⿏标有⿏标的驱动,磁盘有磁盘的驱动,我们的I/O⼦系统要去调⽤这些驱动完成相应的IO事件。就可以使得IO⼦系统独⽴于硬件。我们⽤⼾不关系怎么调⽤驱动去运⾏设备,只要想⽤⼾暴露⼀个接⼝就⾏。不同的硬件⼚商根据OS系统规定的设备驱动层协议去进⾏设计,就可以使得让OS驱动调⽤控制器

3.2 内核I/O⼦系统

◦ ⼀些服务⸺调度、缓冲、缓存、假脱机、设备保留和错误处理⸺由内核的 I/O ⼦系统提供,

并建⽴在硬件和设备驱动程序基础设施之上。

◦ I/O ⼦系统还负责保护⾃⼰免受错误进程和恶意⽤⼾的侵害。

3.3 I/O请求⽣命周

- BUS

-

相关阅读:

Python Playwright 基本使用(步骤详细)

mindspore训练retinanet时报错无法计算loss,停止训练

redis淘汰策略

32/100 二叉树的层序遍历 33/100 二叉树的最大深度 34/100 平衡二叉树

Ubuntu 20.04上安装Datalog Disassembly工具的过程

电脑翻译软件-在线电脑实时翻译软件

速锐得解码匹配驾培驾考吉利几何E萤火虫数据应用智能评判系统

触摸屏如何利用无线PPI通信模块远程采集PLC数据?

JavaScript:js基础2

美元兑换日元价格分析:日图均线形成熊叉

- 原文地址:https://blog.csdn.net/weixin_61823031/article/details/126431939