-

南京邮电大学电工电子(数电)实验报告——组合逻辑电路 & 时序逻辑电路

一、组合逻辑电路

(1)实验目的

5、使用ISE软件完成组合逻辑设计的输入并仿真

6、掌握Testbech中组合逻辑测试文件的写法

7、下载并测试实现的逻辑功能(2)实验原理或设计过程

①4选1数据选择器

- RTL代码

module m4_1(in0,in1,in2,in3,S,F); input in0,in1,in2,in3; input [1:0]S; //定义输入 output reg F; //定义输出,F定义为reg型 always @* //敏感词使用* begin case(S) //case语句实现选择输出 2'b00:F<=in0; 2'b01:F<=in1; 2'b10:F<=in2; 2'b11:F<=in3; //实现输入S=00、01、10、11时,输出 in0,in1,in2,in3 endcase end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 仿真测试模块代码

`timescale 1ns / 1ps module m4_1_tb; reg in0,in1,in2,in3; reg [1:0] S; wire F; m4_1 uut ( .in0(in0), .in1(in1), .in2(in2), .in3(in3), .S(S), .F(F) ); //例化模块 initial begin in0=0; in1=0; in2=0; in3=0; S = 0; //初始化输入 #100; fork //fork-join实现并行输入 repeat(5) #400 S=S+1; //每400ns S+1 repeat(100) #20 in0=~in0; repeat(50) #40 in1=~in1; repeat(25) #80 in2=~in2; repeat(10) #200 in3=~in3; //输入in0,in1,in2,in3信号为不 同的脉冲信号,方便选择后观察 join end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

②3-8译码器

- RTL代码

module d3_8(D,Y); input [2:0]D; //定义三位输入 output reg[7:0]Y; //定义八位输出 always@(D) //使用always块,敏感词选用D begin case(D) //case语句实现3-8过程 3'b000:Y=8'b1111_1110; 3'b001:Y=8'b1111_1101; 3'b010:Y=8'b1111_1011; 3'b011:Y=8'b1111_0111; 3'b100:Y=8'b1110_1111; 3'b101:Y=8'b1101_1111; 3'b110:Y=8'b1011_1111; 3'b111:Y=8'b0111_1111; //输入和输出一一选择对应 endcase end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 仿真测试模块代码

`timescale 1ns / 1ps module d3_8_tb; reg [2:0] D; wire [7:0] Y; d3_8 uut ( .D(D), .Y(Y) ); initial begin D = 0; #100; //进行输入端口初始化 repeat(10) //重复十次 begin D=3'b000; #20; D=3'b001; #20; D=3'b010; #20; D=3'b011; #20; D=3'b100; #20; D=3'b101; #20; D=3'b110; #20; D=3'b111; #20; //依次使D等于0-7,观察输出 end end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

③8-3优先编码器

- RTL代码

module en8_3(en,I,Y,Yx,Yn); input en; input [7:0]I; output reg[2:0]Y; output reg Yx,Yn; always@(I) begin if(!en) begin Y=3'b111; Yx=1; Yn=1; end else begin if(I==8'b1111_1111) begin Y=3'b111; Yx=1; Yn=0; end else begin Yx=0; Yn=1; if(I[7]==0) Y=3'b000; else if(I[6]==0) Y=3'b001; else if(I[5]==0) Y=3'b010; else if(I[4]==0) Y=3'b011; else if(I[3]==0) Y=3'b100; else if(I[2]==0) Y=3'b101; else if(I[1]==0) Y=3'b110; else if(I[0]==0) Y=3'b111; end end end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 仿真测试模块代码

`timescale 1ns / 1ps module en8_3_tb; reg en; reg [7:0] I; wire [2:0] Y; wire Yx; wire Yn; en8_3 uut ( .en(en), .I(I), .Y(Y), .Yx(Yx), .Yn(Yn) ); initial begin en = 0; I = 0; #100; en=1; repeat(20) begin I=8'b1111_1111; #20; I=8'b0111_1111; #20; I=8'b1011_1111; #20; I=8'b1101_1111; #20; I=8'b1110_1111; #20; I=8'b1111_0111; #20; I=8'b1111_1011; #20; I=8'b1111_1101; #20; I=8'b1111_1110; #20; end end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

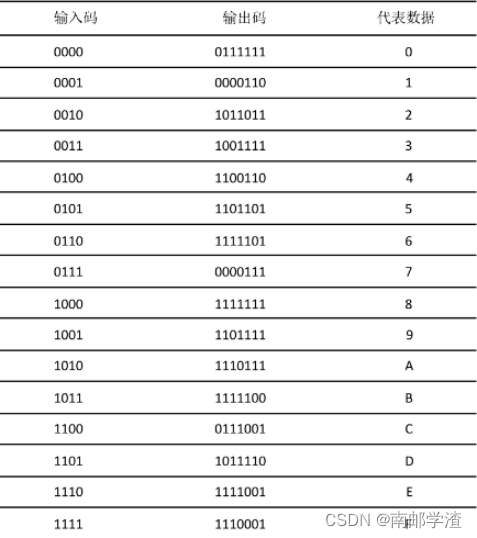

④十六进制七段LED显示译码器

- RTL代码

module led7(D,Y,en); input [3:0]D; input en; output reg[6:0]Y; always@(D) begin if(!en) Y=7'b000_0000; else case(D) 4'b0000:Y=7'b011_1111; 4'b0001:Y=7'b000_0110; 4'b0010:Y=7'b101_1011; 4'b0011:Y=7'b100_1111; 4'b0100:Y=7'b110_0110; 4'b0101:Y=7'b110_1101; 4'b0110:Y=7'b111_1101; 4'b0111:Y=7'b000_0111; 4'b1000:Y=7'b111_1111; 4'b1001:Y=7'b110_1111; 4'b1010:Y=7'b111_0111; 4'b1011:Y=7'b111_1100; 4'b1100:Y=7'b011_1001; 4'b1101:Y=7'b101_1110; 4'b1110:Y=7'b111_1001; 4'b1111:Y=7'b111_0001; endcase end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 仿真测试模块代码

`timescale 1ns / 1ps module led7_tb; reg [3:0] D; reg en; wire [6:0] Y; led7 uut ( .D(D), .Y(Y), .en(en) ); initial begin D = 0; en = 0; #100; en=1; repeat(10) begin D=4'b0000; #20; D=4'b0001; #20; D=4'b0010; #20; D=4'b0011; #20; D=4'b0100; #20; D=4'b0101; #20; D=4'b0110; #20; D=4'b0111; #20; D=4'b1000; #20; D=4'b1001; #20; D=4'b1010; #20; D=4'b1011; #20; D=4'b1100; #20; D=4'b1101; #20; D=4'b1110; #20; D=4'b1111; #20; end end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

(3)实验数据分析和实验结果

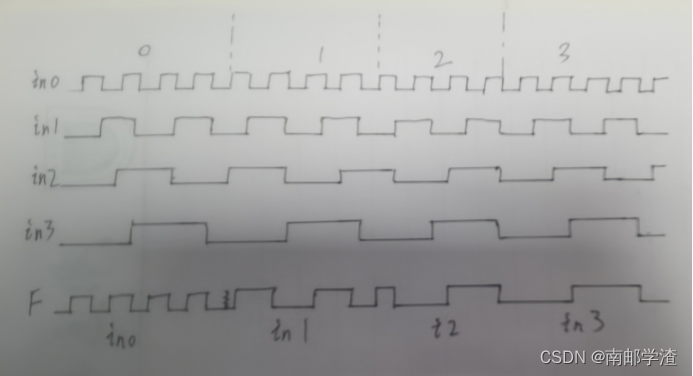

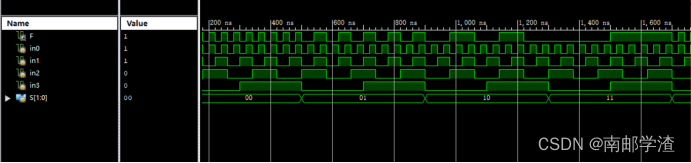

1、四选一数据选择器波形图:

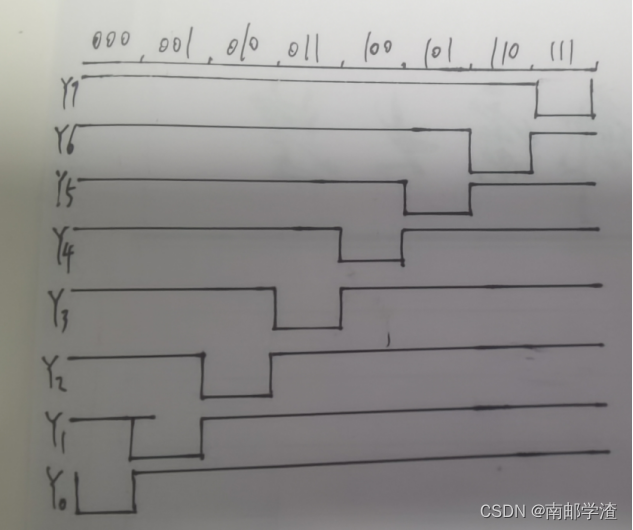

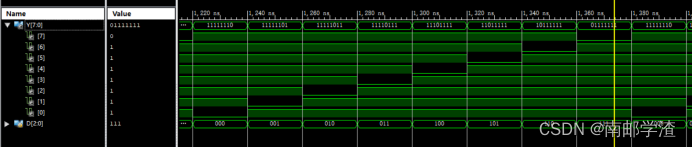

2、3-8译码器波形图:

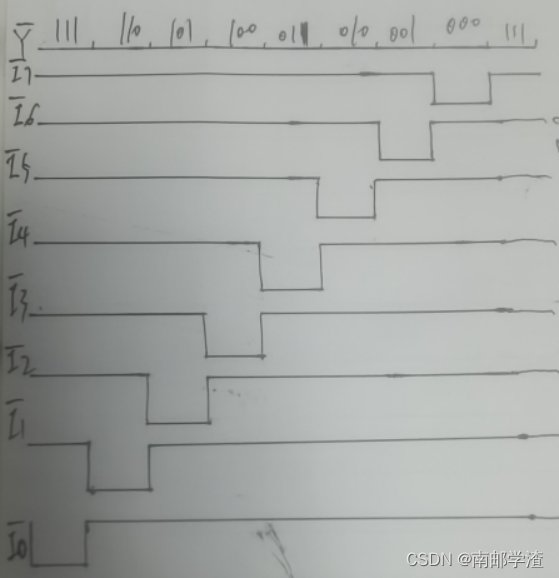

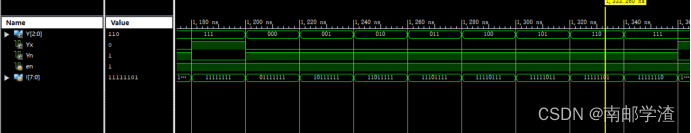

3、8-3优先编码器波形图:

(4)仿真波形图

1、四选一数据选择器仿真图:

2、3-8译码器仿真图:

3、8-3优先编码器仿真图:

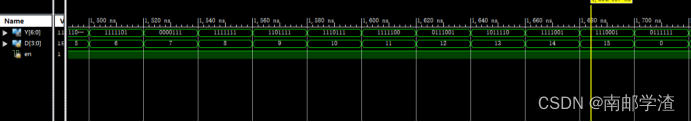

4、十六进制7段led显示译码器:

二、时序逻辑电路

(1)实验目的

1、使用ISE软件完成时序逻辑电路的设计输入并仿真

2、掌握tb中时序逻辑测试文件的写法

3、下载并测试实现的逻辑电路(2)实验原理或设计过程

①74161计数器

- RTL代码

module and74161(CR,ld,P,T,clk,Q,rst,A,B,C,D); input CR,ld,P,T,rst; input clk; input A,B,C,D; output reg[3:0]Q; always @(posedge clk,negedge rst) begin if(rst==0) Q<=4'b0; else if(CR==0) Q<=4'b0; else if(CR&ld==0) Q<={A,B,C,D}; else if(CR&ld&P&T) Q<=Q+1; else if(CR&ld&P==0) Q<=Q; else if(CR&ld&T==0) Q<=Q; end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 仿真测试模块代码

`timescale 1ns / 1ps module and74161_tb; reg CR; reg ld; reg P; reg T; reg clk; reg A,B,C,D; reg rst; wire [3:0] Q; and74161 uut ( .CR(CR), .ld(ld), .P(P), .T(T), .clk(clk), .Q(Q), .A(A), .B(B), .C(C), .D(D), .rst(rst) ); initial begin CR = 0; ld = 0; P = 0; T = 0; clk = 0; A=0; B=0; C=0; D=0; rst=0; #100; A=0; B=1;C=0;D=1; rst=1; CR=1;ld=0;#50; //ABCD rst=1; CR=0;ld=1;P=1;T=1; #20; //清0 rst=1; CR=1;ld=0;P=0;T=0; #20; //清0 rst=1; CR=1;ld=1;P=0;T=1; #20; rst=1; CR=1;ld=1;P=1;T=0; #20; rst=1; CR=1;ld=1;P=1;T=1; #2000; end always #7 clk=~clk; endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

②D触发器(异步复位与同步时能、异步置位与异步复位)

- RTL代码

module dff(D,EN,CLK,sd,rd,Q,QN); input D,EN,CLK,sd,rd; output reg Q; output reg QN; always @(posedge CLK) begin if(EN&sd==0) begin Q<=1;QN<=0; end else if(EN&sd==1&rd==0) begin Q<=0;QN<=1; end else if(EN&sd==1&rd==1) begin Q<=D;QN<=~D; end else begin Q<=Q;QN<=QN; end end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 仿真测试模块代码

`timescale 1ns / 1ps module dff_tb; reg D; reg EN; reg CLK; reg sd; reg rd; wire Q; wire QN; dff uut ( .D(D), .EN(EN), .CLK(CLK), .sd(sd), .rd(rd), .Q(Q), .QN(QN) ); initial begin D = 0; EN = 0; CLK = 0; sd = 0; rd = 0; #100; EN=1; end initial fork forever #100 rd=rd+1; forever #200 sd=sd+1; forever #20 D=D+1; join always #10 CLK=~CLK; //输入时钟 endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

③模M计数器(实现模5计数器,五个状态为3,4,5,6,7)

- RTL代码

module counter5(en,clk,cnt,co,rst_n); input en; input clk; input rst_n; output reg [3:0]cnt; output co; always @(posedge clk,negedge rst_n) begin if(!rst_n) cnt<=4'b0011; else if(en&cnt==4'b0111) cnt<=4'b0011; else if(en) cnt<=cnt+1'b1; else cnt<=cnt; end assign co=cnt[0]&cnt[1]&cnt[2]; endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 仿真测试模块代码

`timescale 1ns / 1ps module counter5_tb; reg en; reg clk; reg rst_n; wire [3:0] cnt; wire co; counter5 uut ( .en(en), .clk(clk), .cnt(cnt), .co(co), .rst_n(rst_n) ); initial begin en = 0; clk = 0; rst_n = 0; #100; en=1; rst_n=1; end always #7 clk=~clk; endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

④移位寄存器74194

- RTL代码

module reg74194(cr,clk,sr,sl,M,Q,D); input cr,clk,sr,sl; input [3:0]D; input [1:0]M; output reg[3:0]Q; always @(posedge clk) begin if(!cr) Q<=4'b0000; else if(cr&M==2'b11) Q<=D; else if(cr&M==2'b01) begin Q[2:0]<=Q[3:1]; Q[3]<=sr; end else if(cr&M==2'b10) begin Q[3:1]<=Q[2:0]; Q[0]<=sl; end else Q<=Q; end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 仿真测试模块代码

`timescale 1ns / 1ps module reg74194_tb; reg cr; reg clk; reg sr; reg sl; reg [1:0] M; reg [3:0] D; wire [3:0] Q; reg74194 uut ( .cr(cr), .clk(clk), .sr(sr), .sl(sl), .M(M), .Q(Q), .D(D) ); initial begin cr = 0; clk = 0; sr = 0; sl = 0; M = 0; D = 0; #100; cr=1;M=2'b11; D=4'b1011; #50; cr=1;M=2'b01;sr=1'b1; #50; cr=1;M=2'b01;sr=1'b0; #50; cr=1;M=2'b10;sl=1'b1; #50; cr=1;M=2'b10;sl=1'b0; #50; cr=1;M=2'b00; #50; end always #7 clk=~clk; endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

(3)实验数据分析和实验结果

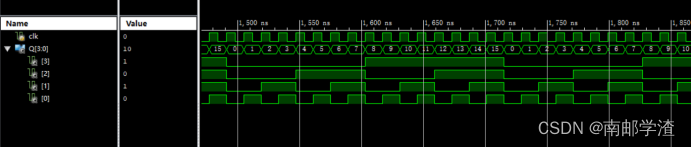

1、74161仿真波形图:

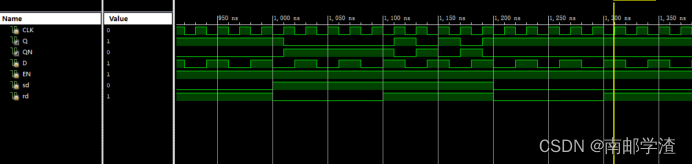

2、D触发器(异步复位与同步使能、异步置位与异步复位)

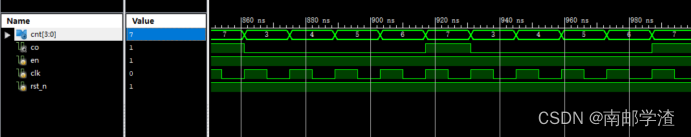

3、模M计数器(实现模5计数器,五个状态为3,4,5,6,7)

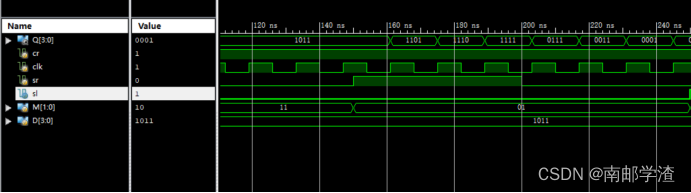

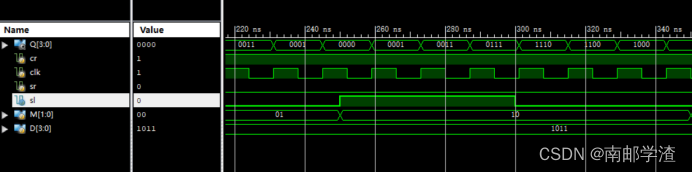

4、移位寄存器74194

左移:

右移:

-

相关阅读:

【ADS-01】TC264实现LED灯闪烁

软件开发项目文档系列之二如何撰写项目建设方案

去面试了几家BATJ等N家互联网大厂

辅修计算机的机械专业大二同学的跨考准备

iOS 硬件解码相关

NetAssist使用

同样的数据图片和模型,在kaggle上训练和在本地训练差距怎么那么大

flutter 递归

springboot毕设项目宠物商城系统的设计与实现pcz03(java+VUE+Mybatis+Maven+Mysql)

ArcGIS JS API 4.23 Web服务器部署

- 原文地址:https://blog.csdn.net/qq_52450571/article/details/126413982