-

操作DAC模块

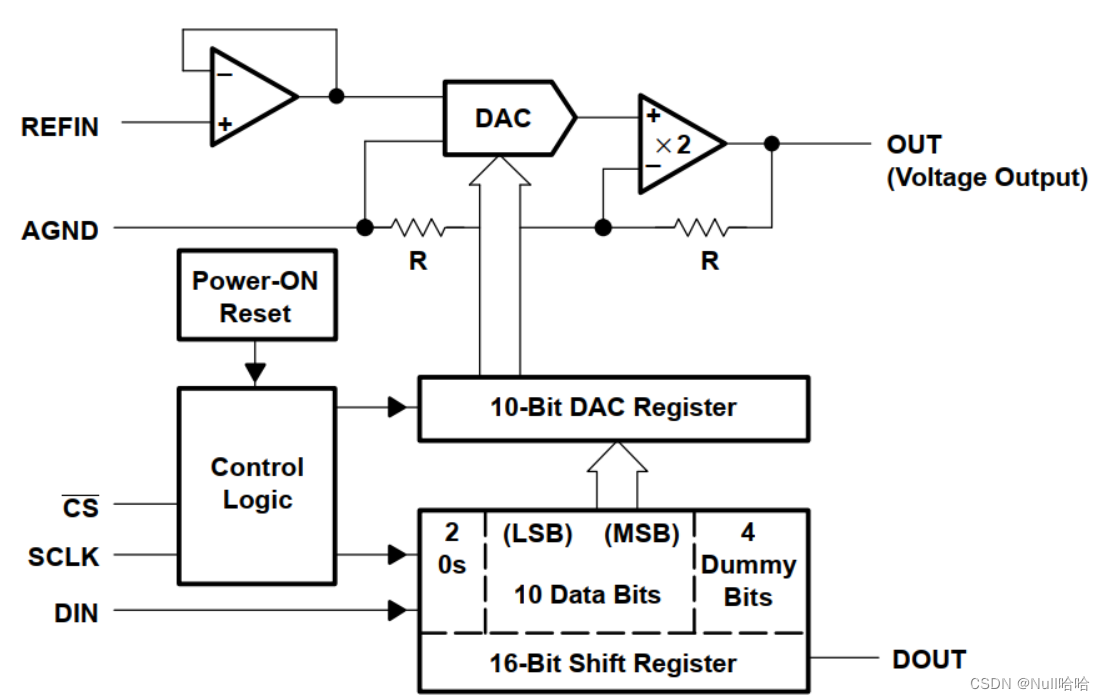

DAC的操作原理图如下:

输入数据从DIN进入16为的移位寄存器,其中低2位必须为0,高4位为无效数据,中间的10位为有效数据,将中间的10位有效数据上传到DAC寄存器。DAC寄存器把10位的数据转换成模拟信号输出。

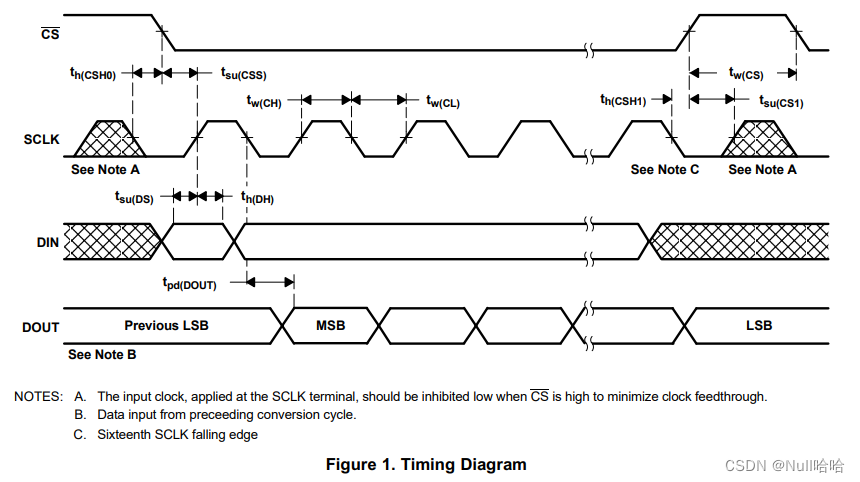

DAC模块时序图:

操作步骤:

1.CS:电平从高到低下降沿期间选中芯片

2.SCLK(时钟引脚)的上升沿把数据移入16位移位寄存器(先移最高位MSB,最后移最低位LSB)

3.CS(片选引脚)从低变高的上升沿期间把其中的10位有效数据传入DAC寄存器。发出DOUT信号DOUT数据来自16位移位寄存器第1个数据是上次数据遗留下的LSB位(最低位),其余15个数据来自16位移位寄存器的高15位,16位移位寄存器的LSB在下一个周期的第1个时钟传输,LSB必定是0,所以当前的周期里读出16位移位寄存器的15位数据也足够了。

1.编写应用程序

2.修改设备树

进入Linux内核源码目录

输入/ecspi1查找spi1

参考红色框内写dac的设备树。

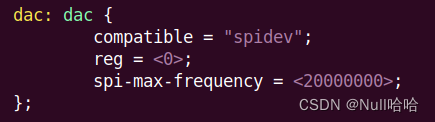

①compatible设置为spidev

②reg = <0>表示dac为ecspi1中的第0个设备,使用<&gpio4 26 GPIO_ACTIVE_LOW>这个片选引脚。

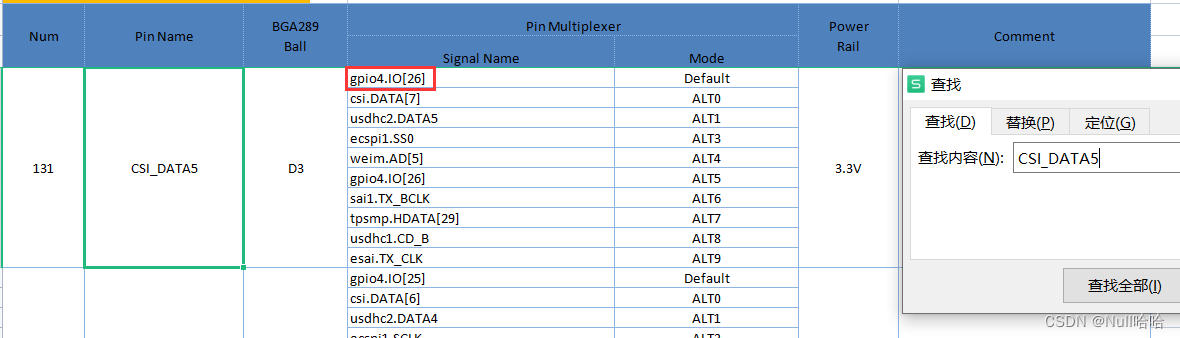

通过查询拓展版原理图:

可以看出SPI CS0 所使用的20号引脚。

查询底板原理图:

可知20号引脚接到CSI_DATA5引脚。

查询核心板引脚表MYC-Y6ULX_Pin_list_V13:

CSI_DATA5

所以可知使用的是<&gpio4 26 GPIO_ACTIVE_LOW>这个片选引脚。③spi-max-frequency为最大频率。通过查询模块芯片手册

将时钟引脚的低电平25ns+高电平25ns =50ns

1秒=1000000000 纳秒(ns);

F=1000000000/50=20,000,000Hz = 20MHz写入的节点为:

:wq保存退出,执行make dtbs,编译设备树。

编译完成后拷贝到开发板输入vi drivers/spi/Makefile查看spidev

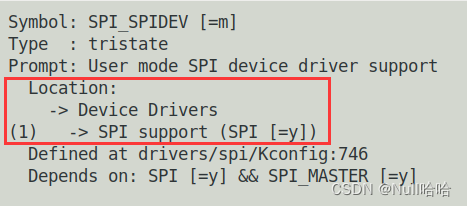

输入vi .config,查询CONFIG_SPI_SPIDEV是否配置进内核

上图说明没有配置进。

输入make menuconfig

输入/CONFIG_SPI_SPIDEV

可知该设置的目录。

进入该目录。

找到User mode SPI device driver support,输入M。使其编译为模块,单独加载。

按右箭头,选择Exit,一直选择Exit退出保存。回到终端输入make modules,编译内核模块。

编译完后拷贝到开发板 cp drivers/spi/spidev.ko ~/nfs_rootfs/

将dtb文件拷贝到开发板boot目录下,重启。

重启后

可看出dac已经编译进设备树。

输入insmod spidev.ko,安装驱动

输入./dac_test /dev/spidev0.0 运行程序即可

-

相关阅读:

chapter6——流水线的艺术

Redis 内存淘汰和过期删除策略

两分钟打造一个转属于你的网址导航(零基础,告别广告困扰)

通过Docker安装ElasticSearch和Kibana

CCS9.1导入F28069M例子工程 遇到的一些问题

Intellij 自定义MyBatis映射文件模板

docker 环境部署

【C++】day2学习成果:引用、结构体等等。。。

民生银行信用卡中心金融科技24届春招面经

Java中获取Class对象的三种方式

- 原文地址:https://blog.csdn.net/qq_44823010/article/details/126349481