-

FPGA零基础学习:VGA协议驱动设计

VGA(Video Graphics Array)视频图形阵列是 IBM 于1987年提出的一个使用模拟信号的电脑显示标准。VGA具有分辨率高、显示速率快、颜色丰富等优点。VGA 接口不但是CRT 显示设备的标准接口,同样也是 LCD 液晶显示设备的标准接口,具有广泛的应用范围。

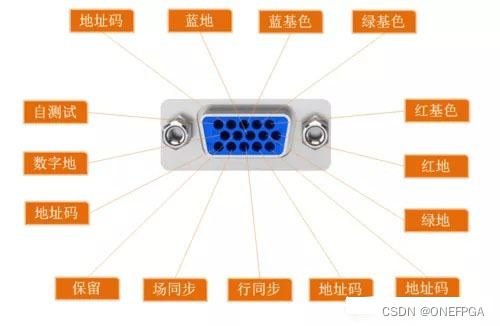

VGA接口即电脑采用VGA标准输出数据的专用接口。VGA接口是一种D型接口,上面共有15针孔,分成三排,每排五个。其中比较重要的是3根 RGB 彩色分量信号和2根扫描同步信号 HSYNC 和 VSYNC 针。其母头插座引脚编号图如下图所示:

三基色是指通过其他颜色的混合无法得到的“基本色”。由于人的肉眼有感知RGB(红绿蓝)三种不同颜色的锥体细胞,因此色彩空间通常可以由RGB三种基本色来表达。

自然界中的绝大部分彩色,都可以由三种基色按一定比例混合得到。

所以VGA接口中,表示颜色分量的只有红绿蓝三种基色。由于VGA接口的三基色为模拟信号值,FPGA无法输出,所以在FPGA的IO到VGA接口中间要有对应的数字量转模拟量的电路。

SANXIN – B01中采用电阻网络来实现数字量转模拟量的功能。

像素是指由图像的小方格组成的,这些小方块都有一个明确的位置和被分配的色彩数值,小方格颜色和位置就决定该图像所呈现出来的样子。可以将像素视为整个图像中不可分割的单位或者是元素。不可分割的意思是它不能够再切割成更小单位,它是以一个单一颜色的小格存在。每一个点阵图像包含了一定量的像素,这些像素决定图像在屏幕上所呈现的大小。

VGA显示器上每一个像素点可以很多种颜色,由R、G、B三种颜色构成。如果每个像素点采用3位二进制数表示,即R用1bit表示,G用1bit表示,B用1bit表示,则此像素点一共可以显示8种颜色;如果每个像素点采用8位二进制数表示,即R用3bit表示,G用3bit表示,B用2bit表示,则此像素点一共可以显示256种颜色。在SANXIN – B01开发板中,采用RGB332的进行表示。

在VGA显示器中,像素点RGB的二进制数越多,能够表示的颜色就越多,此时,显示的图像就会越清晰。

在VGA显示器中,像素点的个数也是一个非常重要的一个指标。

我们可以打开自己电脑的显示分辨率。

分频率有各种模式,但是基本都是固定好的。分辨率都是长乘宽,前面的数为长,后面的数为宽。长表示屏幕横向可以有多少个像素点;宽表示屏幕纵向可以用多少个像素点。一般来说屏幕都是扁平的,所以长一般都会比宽大。

像素的多少不改变实际物理的尺寸大小,只是呈现的清晰度不同。可以对比500万像素的相机拍的图片和2000万像素的相机拍的图片,大小相同的情况下,清晰度是不同的。

只要我们按照显示器能够支持的分辨率的长和宽,将对应的像素点传输给VGA接口就可以了。但是VGA协议中,要求进行传输像素点的同时,还需要去传输一部分的同步信号。

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。在此我们选择逐行扫描的方式。

VGA的时序主要包括行时序与场时序两个部分。其中行时序主要包括:行同步(Hor Sync) 、行消隐(Hor Back Porch) 、行视频有效(Hor Active Video)和行前肩(Hor Front Porch)这四个参数,行时序的时序图如下图所示:

场时序主要包括:场同步(Ver Sync) 、场消隐(Ver Back Porch) 、场视频有效(Ver Active Video)和场前肩(Ver Front Porch)这四个参数,场时序的时序图如下图所示:

需要注意的有三点:

1、行时序是以”像素”为单位的, 场时序是以”行”为单位的。

2、VGA 工业标准显示模式要求:行同步,场同步都为负极性,即同步脉冲要求是负脉冲。

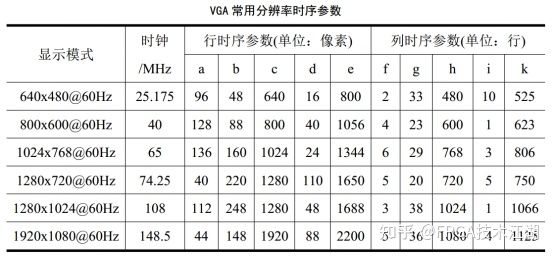

3、VGA 行时序对行同步时间、 消隐时间、 行视频有效时间和行前肩时间有特定的规范, 场时序也是如此。常用VGA 分辨率时序参数如下表所示:

本实验中选择640x480@60Hz。时钟的速率为25.175MHz,我们在设计时,时钟速率选择为25MHz 即可。

设计要求

控制VGA显示器显示全屏红色或者其他颜色。

设计分析

当我们选择640x480@60Hz的标准后,根据对应格式可以发现,此标准的一行为800个像素值,共有525行。也就是说并不是所有的像素值都可以显示出来,显示出来的只有中间的640列和480行,其他的像素值不显示(要求其他的像素值为黑色,即RGB全部给0)。

选择标准需要25MHz的时钟,我们可以选择使用锁相环来进行生成25MHz的时钟。

扫描方式为逐行扫描,从左上角开始。定义一个列坐标计数器(cnt_hs),每个驱动时钟周期加1,当一行结束后,计数器也同时清零。一行为800个像素值,所以计数器将会在0到799无限循环。HSYNC信号在此计数器的前96的计数值拉低,其他时间拉高即可。

定义一个行坐标计数器(cnt_vs),扫描完一行后,进行加一,当一帧图片结束后,计数器清零。一行为800个像素值,所以等cnt_hs为799时,cnt_vs进行加一或者清零,由于一帧图片共有525行,所以计数器在0到524之间无限循环。VSYNC信号在此计数器的前两个计数器拉低,其他时间拉高即可。

根据cnt_hs和cnt_vs,按照对应的标准,就可以得出显示的640列和480行的具体位置。

列显示的范围为:hs_a+hs_b+hs_c>cnt_hs>hs_a+hs_b-1.

行显示的范围为:vs_f+vs_g+vs_h>cnt_vs>vs_f+vs_g-1.

同时在两个有效显示区范围内,就可以显示出来。

设计架构和信号说明

此设计命名为vga_drive。

pll_vga为锁相环,利用外部输入的50MHz的时钟,产生VGA协议所需要的25MHz的时钟。

vga_ctrl为VGA协议的驱动模块。

更改颜色为绿色,vga_rgb <= 8’b000_111_00,生成配置文件后,下板。

绿色全屏为:

根据RGB332的排列,可以自由更改。不同的基色也可以进行混搭,进行验证。

大家好,我是【FPGA功夫熊猫】精益求精,不断推荐好文章。

-

相关阅读:

深度学习环境安装教程-anaconda-python-pytorch

ABAP中FIELD-SYMBOLS的详细用法

温度报警器

【10套模拟】【2】

linux驱动开发:PWM驱动编写

鸿蒙 游戏来了 鸿蒙版 五子棋来了 我不允许你不会

网络编程 10.26

目标检测算法——遥感影像数据集资源汇总(附下载链接)

leetcode做题笔记125. 验证回文串

Scala基础

- 原文地址:https://blog.csdn.net/ONEFPGA/article/details/125483256