-

RH850P1X芯片学习笔记-Generic Timer Module -ATOM

文章目录

- ARU-connected Timer Output Module (ATOM)

- Overview

- ATOM Channel architecture

- ATOM Channel modes

- ATOM SYNCHRONOUS UPDATE

- ATOM Interrupt signals

- ATOM Register overview

- ATOM Register description

- GTM0ATOMiAGCGLBCTRL (i = 0 to 2)

- GTM0ATOMiAGCENDISCTRL (i = 0 to 2)

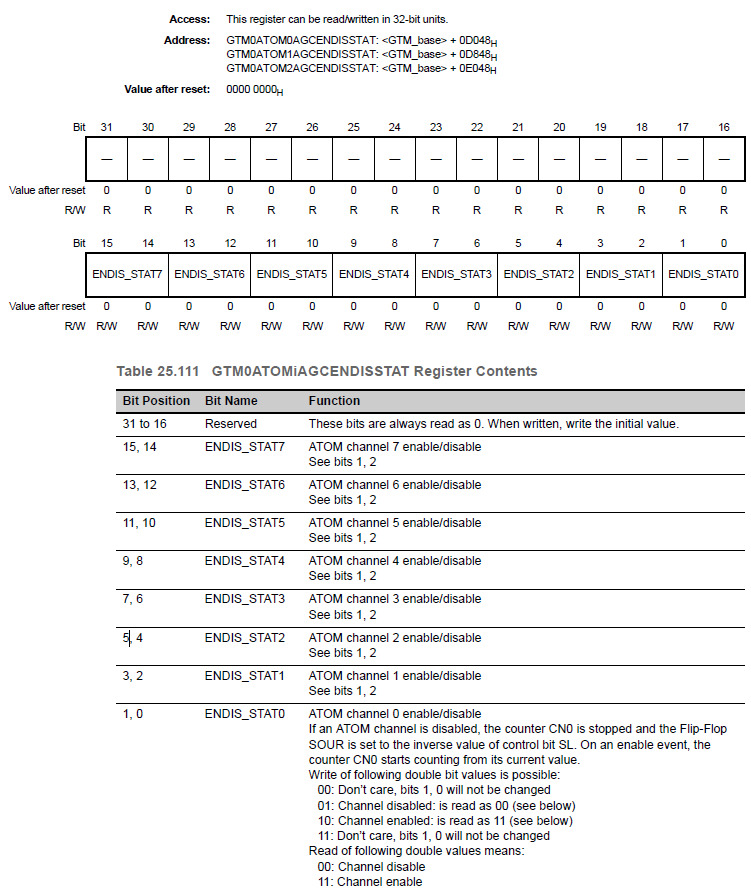

- GTM0ATOMiAGCENDISSTAT (i = 0 to 2)

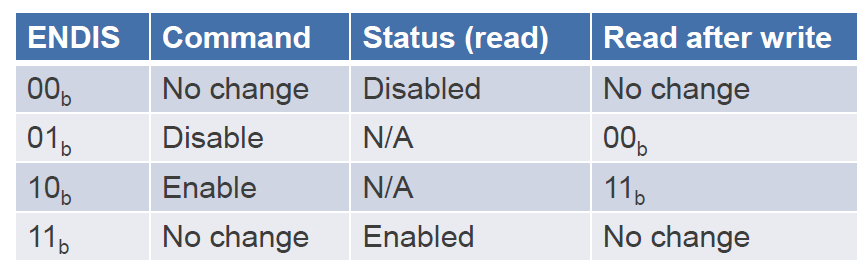

- GTM0ATOMiAGCACTTB (i = 0 to 2)

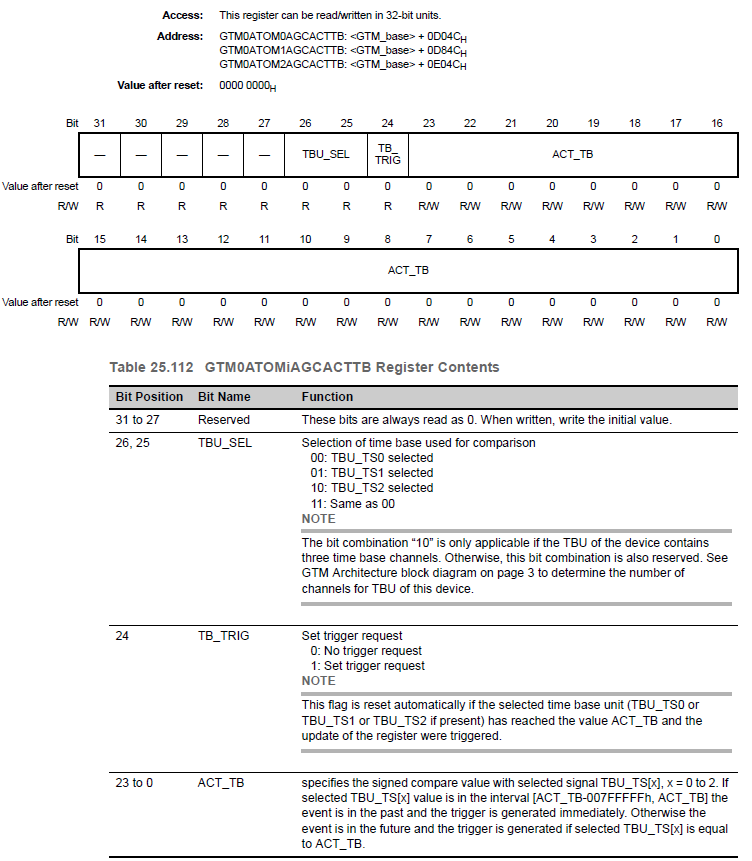

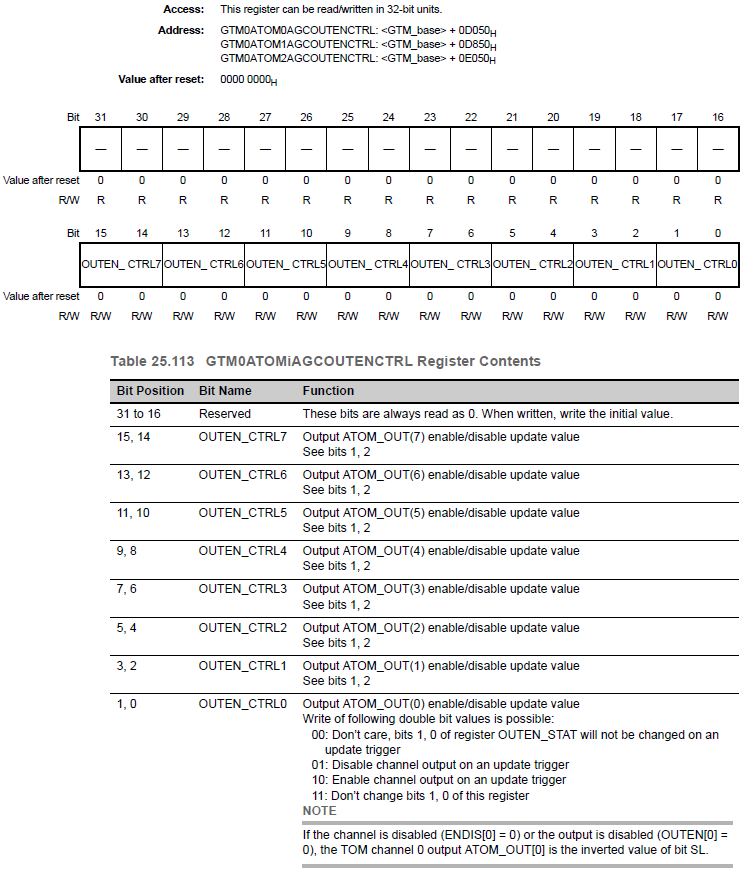

- GTM0ATOMiAGCOUTENCTRL (i = 0 to 2)

- GTM0ATOMiAGCOUTENSTAT (i = 0 to 2)

- GTM0ATOMiAGCFUPDCTRL (i = 0 to 2)

- GTM0ATOMiAGCINTTRIG (i = 0 to 2)

- GTM0ATOMixCTRL (i = 0, x = 0 to 7,i = 1, x = 0 to 7,i = 2, x = 0 to 4)

- GTM0ATOMixSTAT (i = 0, x = 0 to 7,i = 1, x = 0 to 7,i = 2, x = 0 to 4)

- GTM0ATOMixRDADDR

- GTM0ATOMixCN0

- GTM0ATOMixCM0

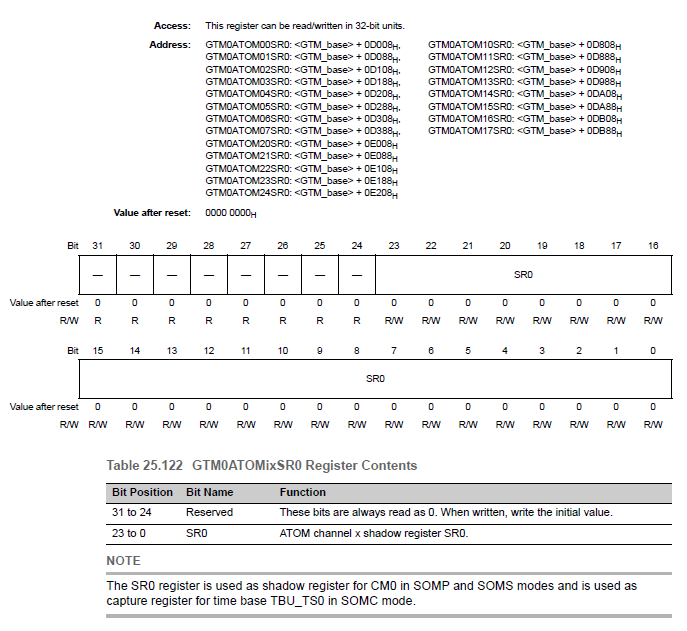

- GTM0ATOMixSR0

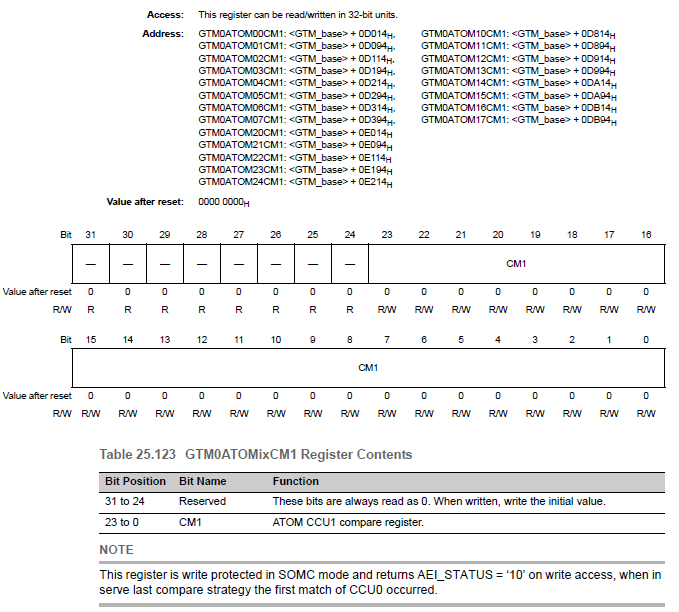

- GTM0ATOMixCM1

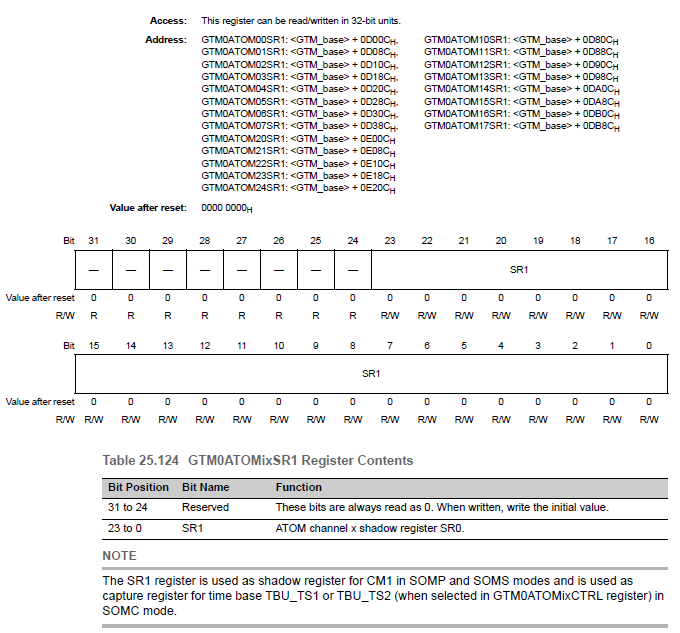

- GTM0ATOMixSR1

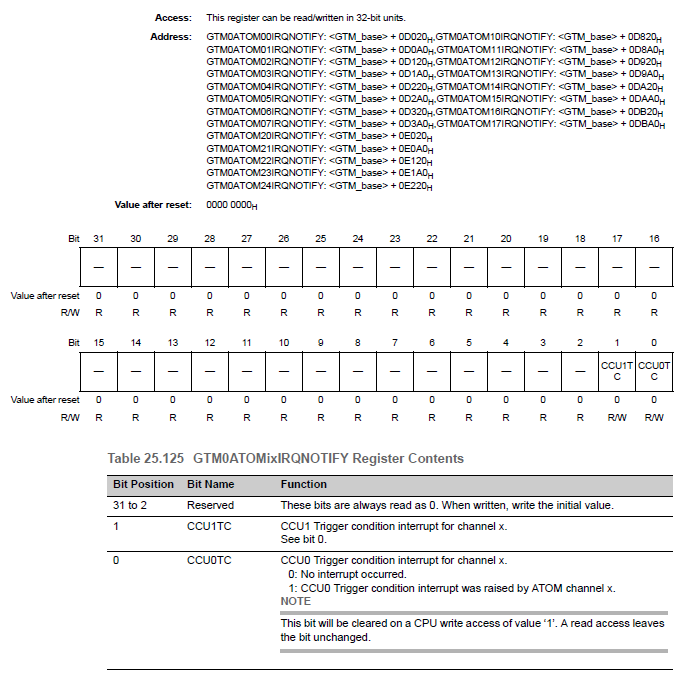

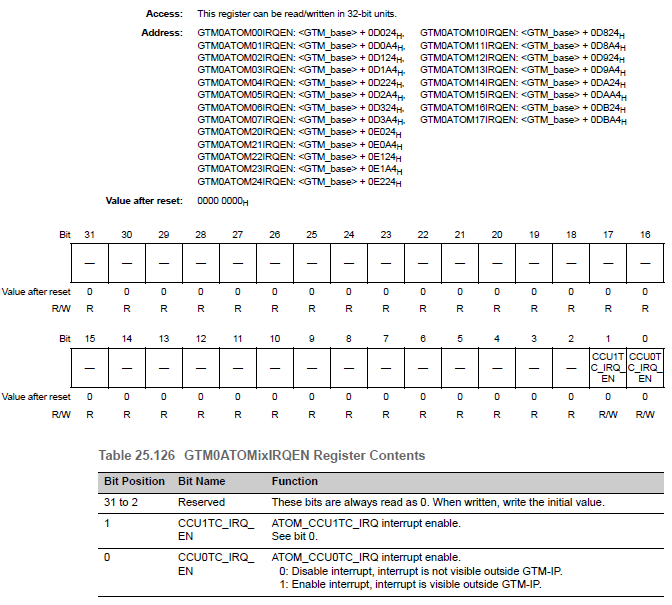

- GTM0ATOMixIRQNOTIFY (x = 0 to 7)

- GTM0ATOMixIRQEN (x = 0 to 7)

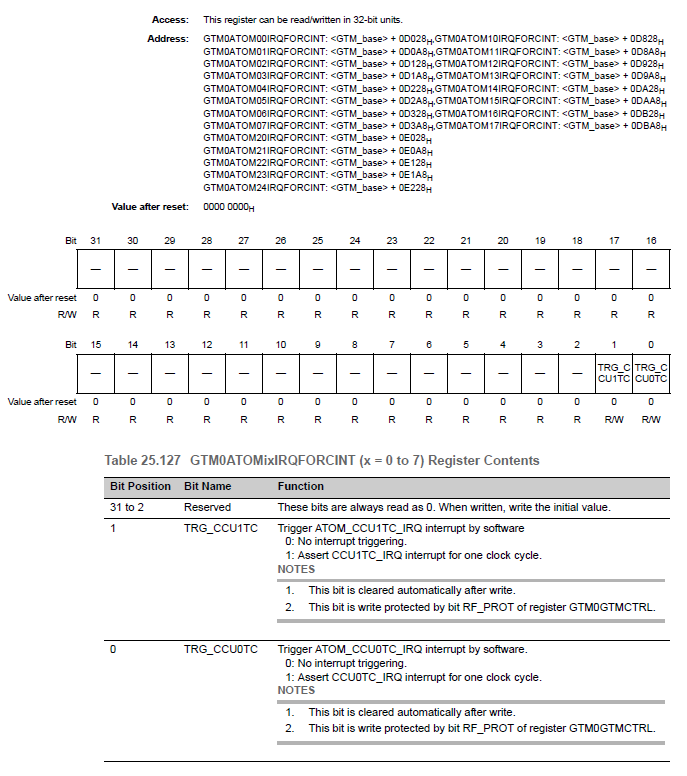

- GTM0ATOMixIRQFORCINT (x = 0 to 7)

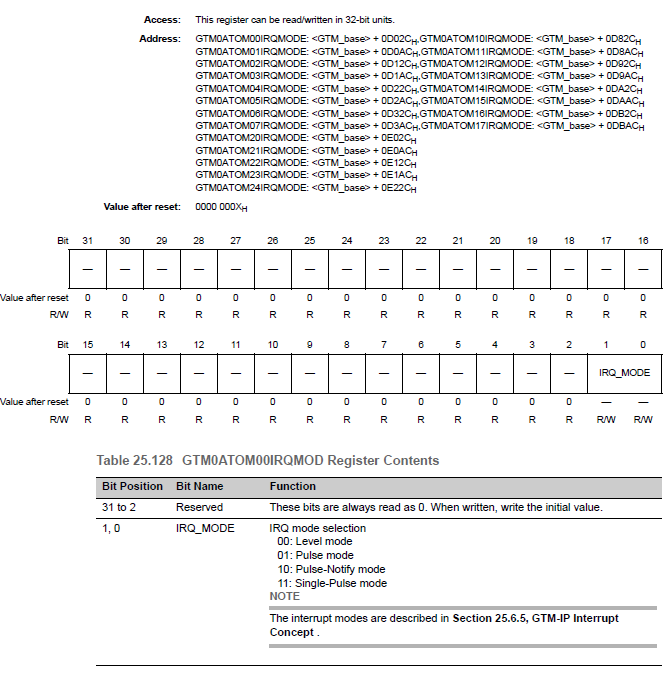

- GTM0ATOM00IRQMOD (x = 0 to 7)

ARU-connected Timer Output Module (ATOM)

Overview

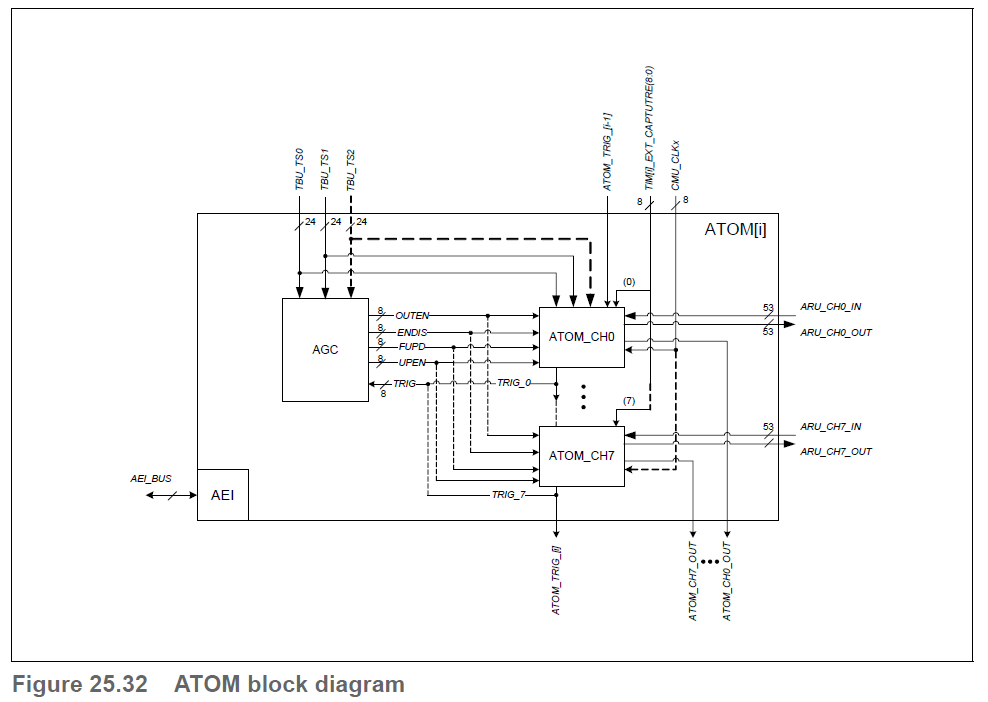

连接ARU的定时器输出模块(ATOM)由于其与ARU的连接,能够在没有CPU交互的情况下生成复杂的输出信号。通常,通过连接到ARU的子模块(例如MCS、DPLL或PSM)在ARU连接上提供输出信号特性。每个ATOM子模块包含八个输出通道,这些通道可以在几种可配置的操作模式下相互独立操作。ATOM子模块的框图如图25.32所示

ATOM子模块的架构与TOM子模块类似,但有一些不同。首先,ATOM只集成了八个输出通道。因此,存在用于ATOM通道的一个ATOM全局控制子单元(AGC)。ATOM连接到ARU,可以设置来自ARU的单独读取请求和对ARU的写入请求。此外,ATOM通道能够代表时间戳生成信号,ATOM通道能够代表内部移位寄存器生成串行输出信号。GLOBAL CHANNEL CONTROL BLOCK

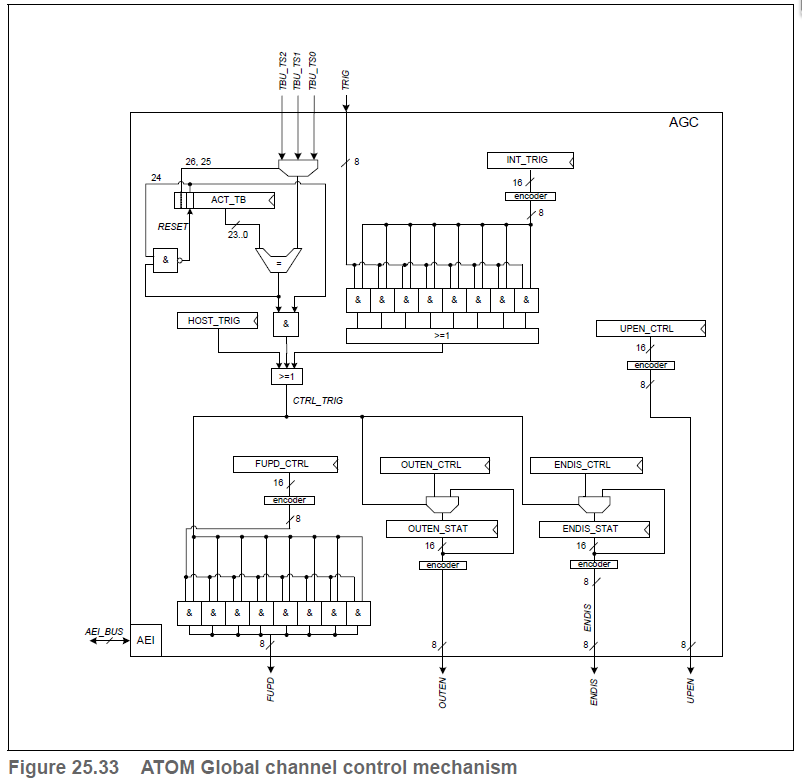

TBU_CH0-2 (ACT_TB)时基匹配寄存器

HOST trigger

强制更新触发器(FUPD)

输出启用控制(OUTEN_STAT) w/ shadow (OUTEN_CTRL

通道启用控制(ENDIS_STAT) w/影子寄存器(ENDIS)

通道更新启用控制(UPEN_CTRL)

内部TRIG_0信号选择(INT_TRIG)

ATOM Channel architecture

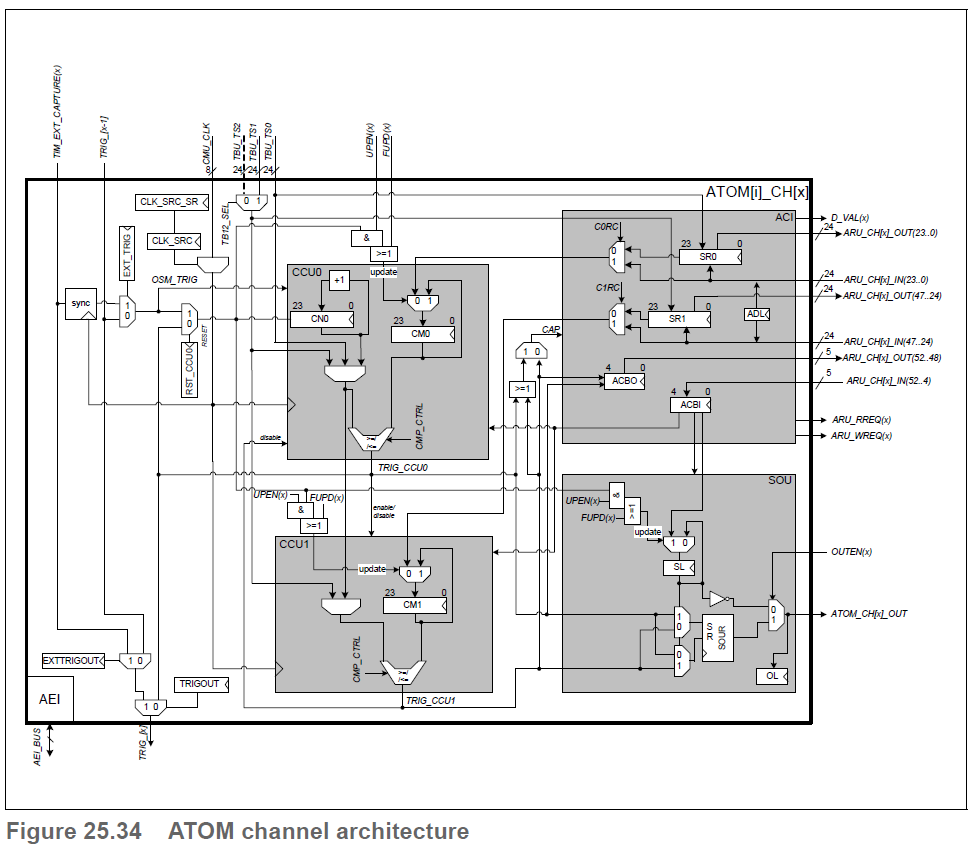

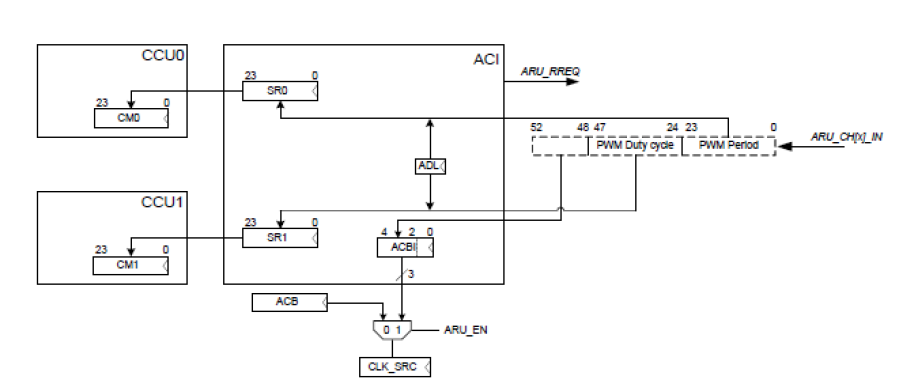

每个ATOM通道能够根据四种操作模式生成输出信号。ATOM通道的体系结构类似于TOM通道的体系结构。ATOM通道的一般架构如图25.34所示。

两个计数器/比较单元CCU0和CCU1

24位计数器寄存器(CN0)时钟w/选择输入频率(CMU_CLK0-7)

信号输出产生单元(SOU)

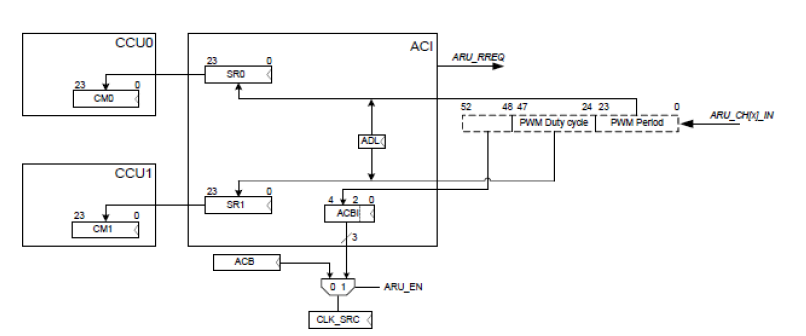

ARU接口单元(ACI)

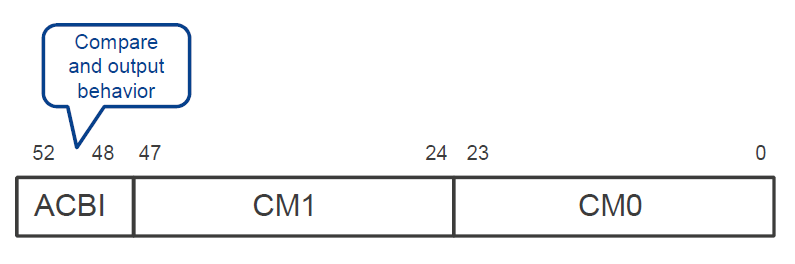

两个比较寄存器CM0和CM1与影子寄存器SR0和SR1连接到ARU

时钟源(CLK_SRC) w/ shadow (CLK_SRC_SR)

相对于TOM来说,主要多了一个ARU接口-ACI模块ATOM Channel modes

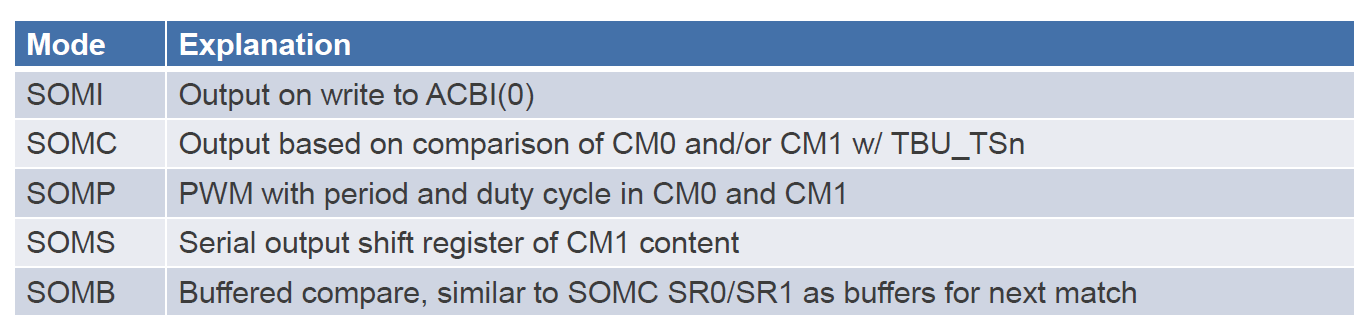

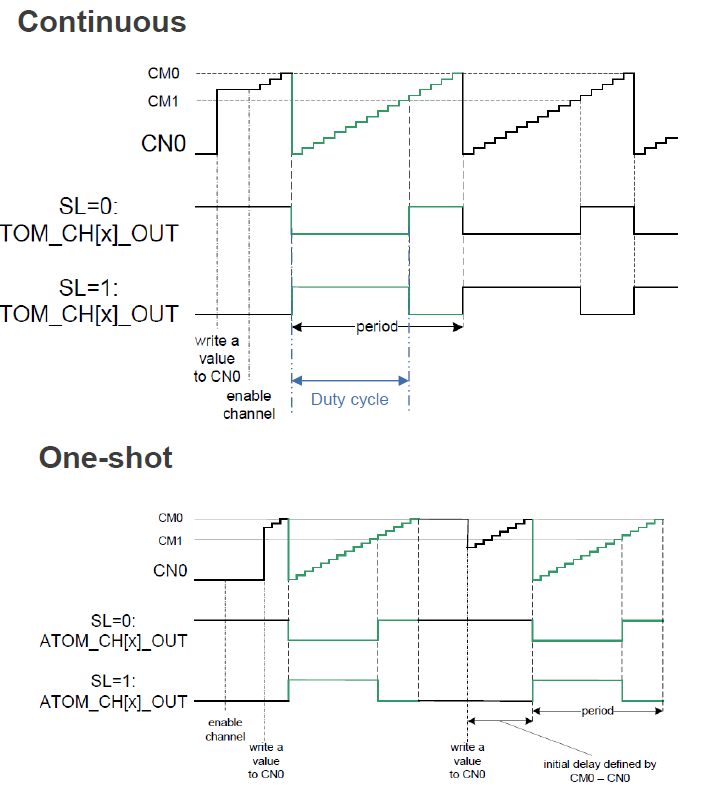

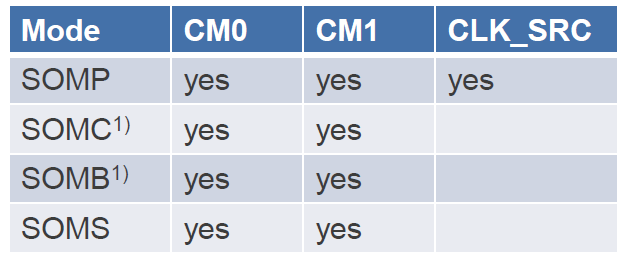

SOMP-Signal Output Mode PWM

输出PWM

TOM功能,当CN0达到CM0或CM1时输出切换

一次或连续操作

CM0定义周期,CM1定义占空比

通过AEI总线进行同步/异步更新

通过ARU同步更新可以使用w/ or w/o ARU

SOMP - ARU

仅同步更新ARU SR0, SR1和CLK_SRC_SR(影子寄存器)

在ARU传输期间阻止从影子寄存器更新CM0和CM1以确保数据一致性

SR0保存CM0,即PWM周期,SR1保存CM1,即PWM占空比

SOMC-Signal Output Mode Compare

输出比较

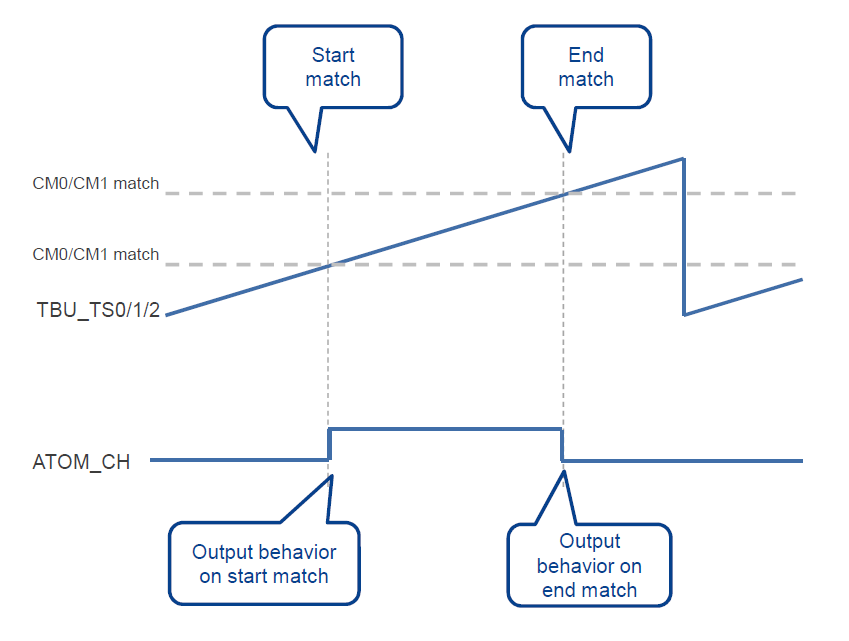

基于CM0/CM1与TBU_TS0/TS1比较的输出动作

较大/相等或较小/相等比较

在CM0/CM1的时间戳匹配存储在通道阴影寄存器(SR0/SR1)

在编程匹配和输出动作后禁用ATOM通道- 读取SR0/SR1并写入新的CM0/CM1后进行下一步匹配

必须配置并启用TBU

SOMC - ARU

在ARU控制CM0、CM1下,由ARU发送匹配行为和输出行为

非阻塞:如果没有匹配,ARU数据将连续传输到CM0, CM1和ACBI

阻塞:在CM0和CM1更新后,不向ARU请求新的数据,直到匹配

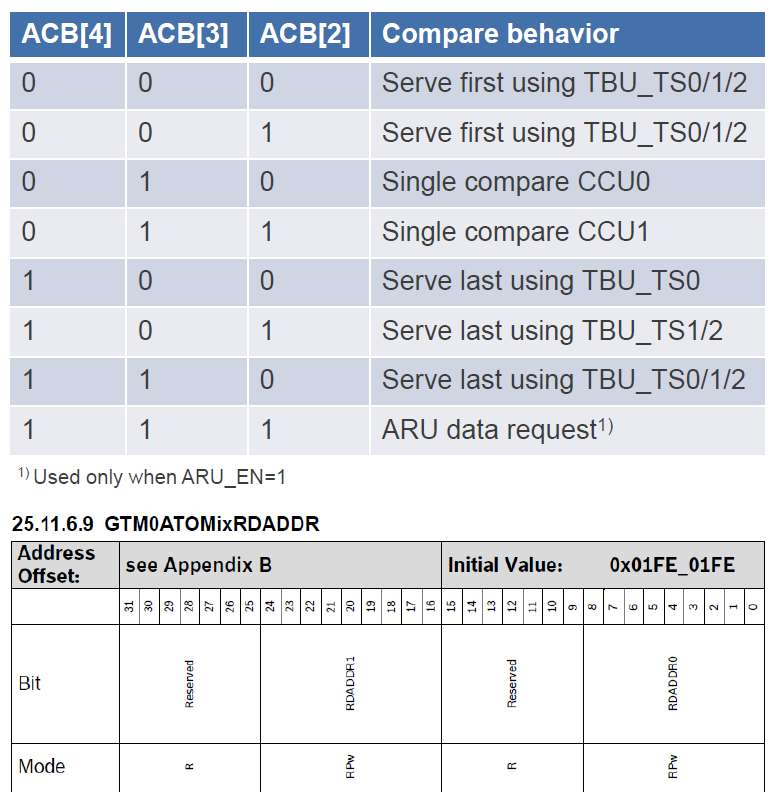

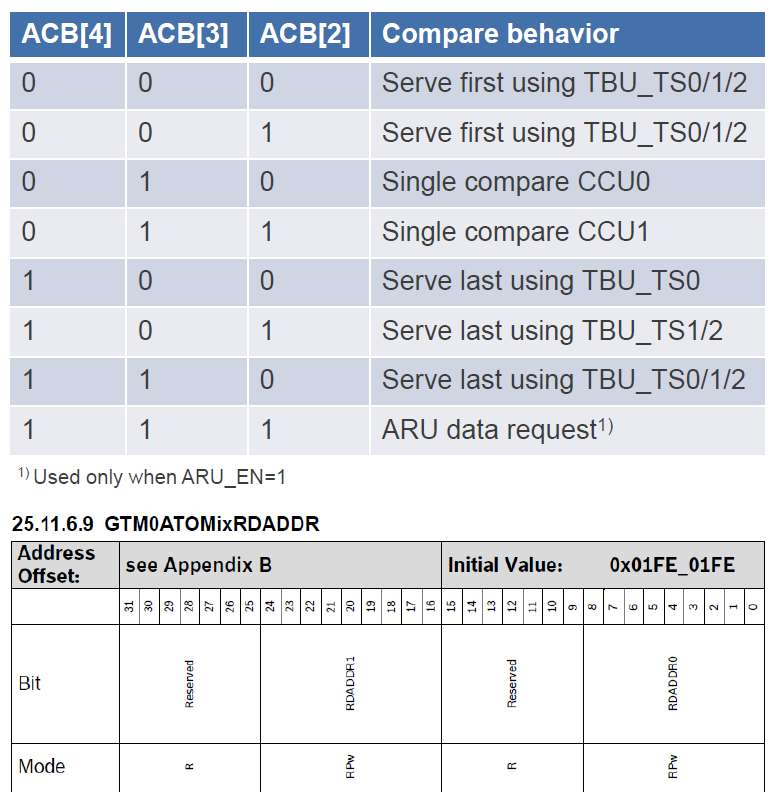

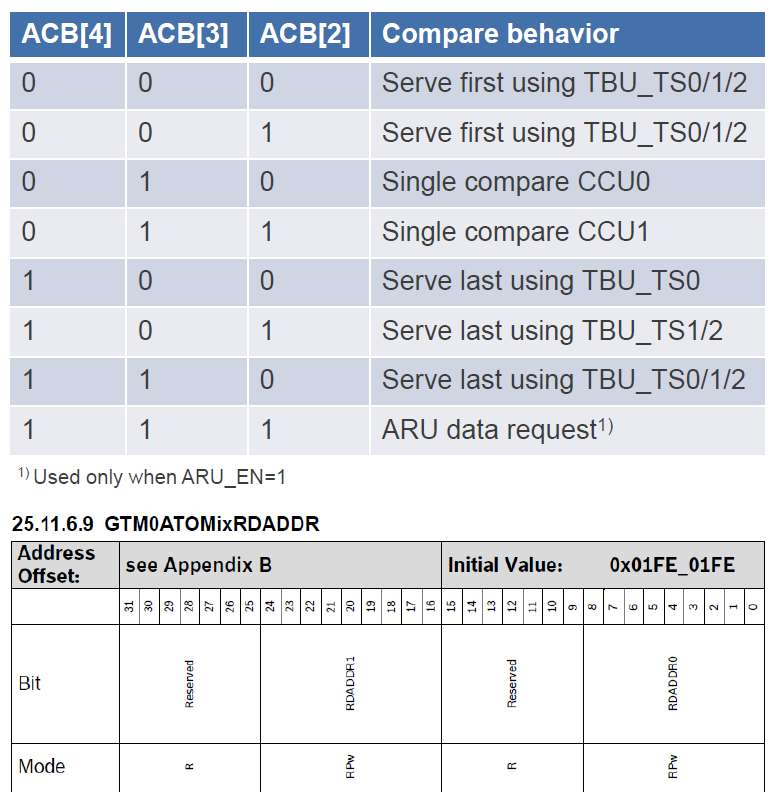

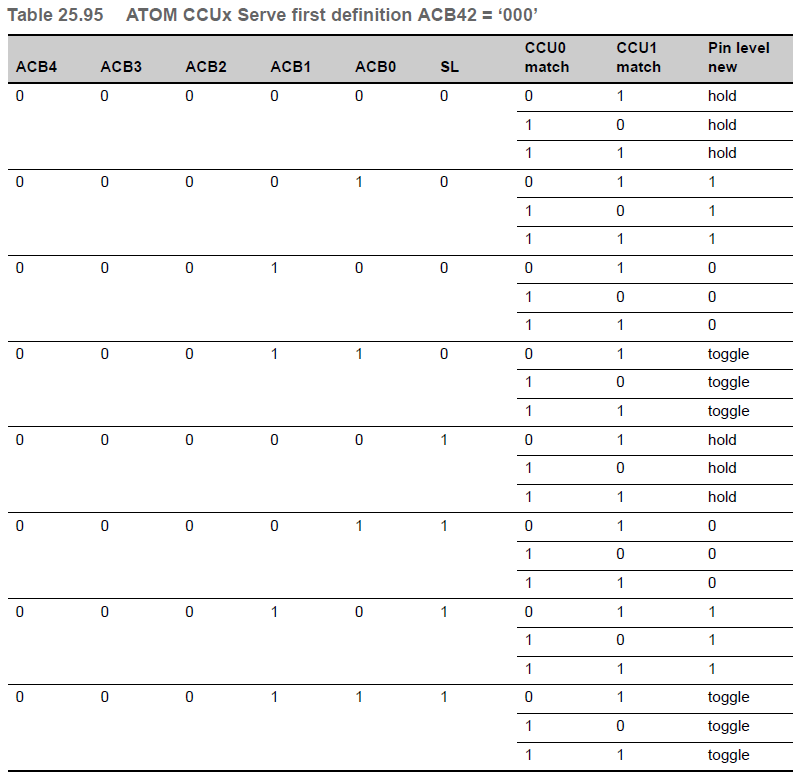

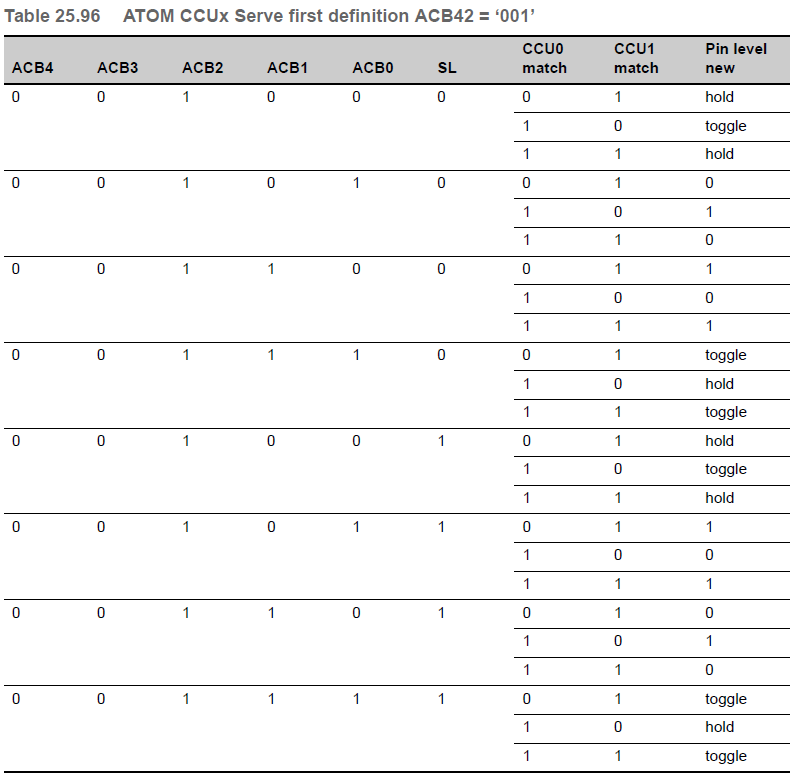

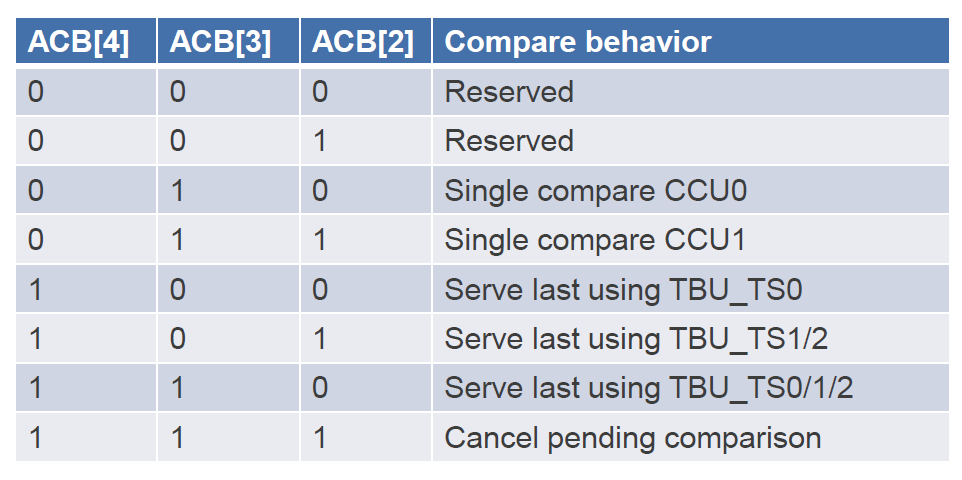

SOMC – COMPARE COMMAND

Serve first:在CCC0和CCU1上进行并行比较,第一次匹配导致输出动作,禁用第二次匹配

Serve last:首先比较CCU0,然后比较CCU1。

CCU0匹配触发输出动作

CCU1匹配切换输出状态

Single compare:只比较CCU0或CCU1,匹配时触发输出动作

ARU data request:切换到ARU RDADDR1并请求新的匹配数据,没有输出动作

配置TBU通道使用(TBU12_SEL)

使用时,比较大于等于或小于等于TBU_TS1/2 (CMP_CTRL)

如果CCU0使用TBU_TS0进行比较,则只有Greater-equal

SR0/SR1中比较匹配时的时间戳

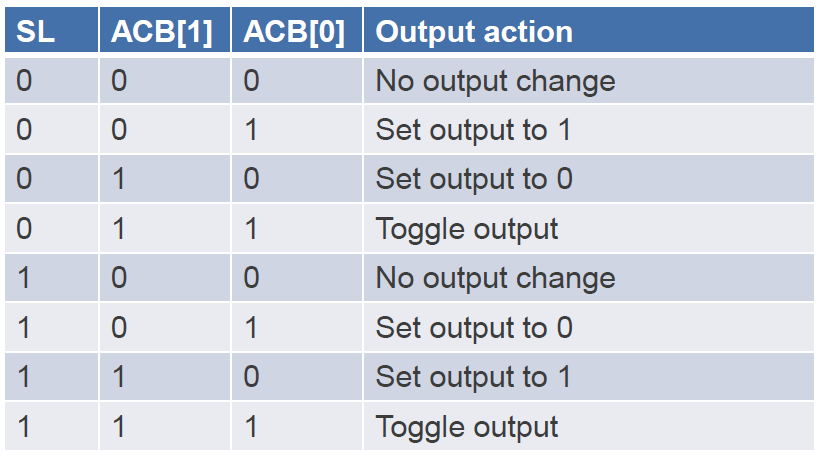

SOMC – OUTPUT ACTION

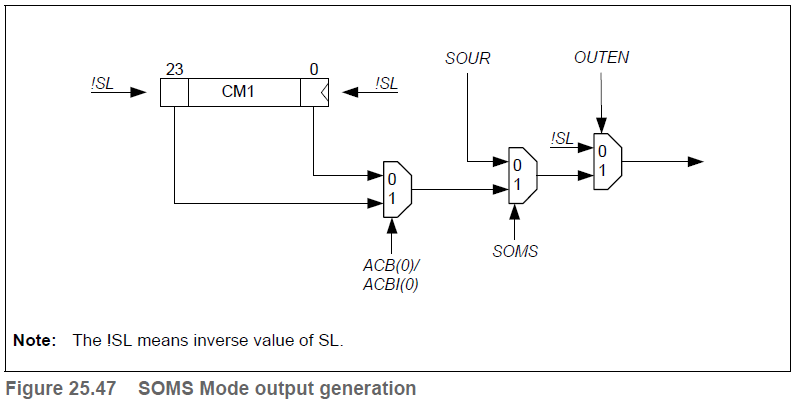

ATOM Signal Output Mode Serial (SOMS)

CM1寄存器的位在通道输出上移出

在CM0中移位的位数

在ATOM_CH[x]_CTRL位ACB0中确定移动方向(左/右)- 右:CM1数据对齐到0位

- 左:CM1数据对齐到第23位

CCU0以计数器/比较模式运行,计数移位的位数

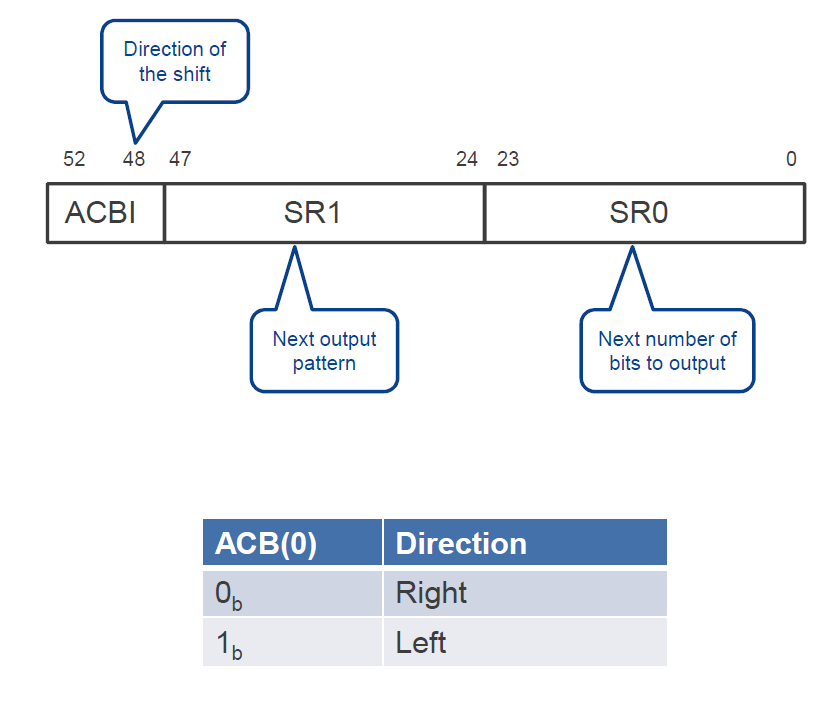

SERIAL OUTPUT - ARU

SR0和SR1以及移位方向

移动方向ACBI(0)

下一个ARU请求发出后,影子寄存器加载到CM0, CM1- 如果通道更新被禁用(UPEN=0),则没有连续的ARU请求

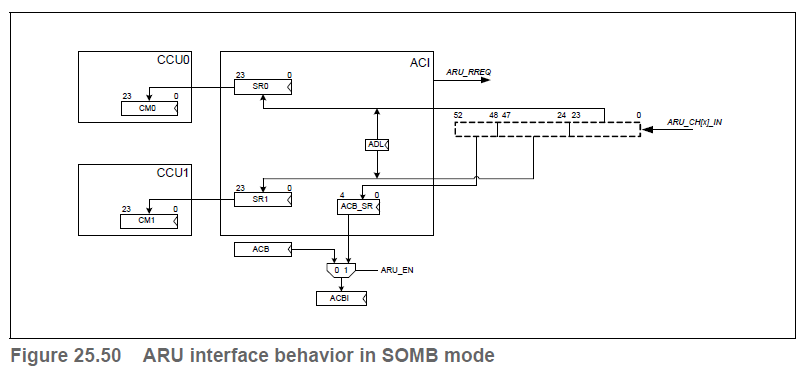

ATOM Signal Output Mode Buffered Compare(SOMB)

类似于SOMC(定义比较的输出操作)

- 新值存储在影子寄存器(ARU或AEI)中

- 匹配后从阴影寄存器加载新值(SR0, SR1, ACB_SR)

- 当没有新的阴影值CCU0/CCU1时,等待空闲

SOMB - COMPARE COMMAND

SOMB – OUTPUT ACTION

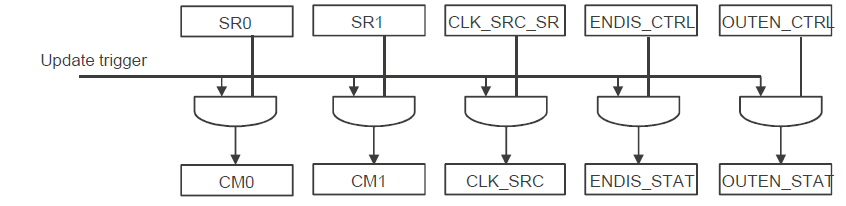

ATOM SYNCHRONOUS UPDATE

几个ATOM寄存器有影子寄存器

CM0/1, CLK_SRC, ENDIS, OUTEN

影子寄存器(CPU, DMA)的更新不影响通道操作

在触发状态下更新工作寄存器(当启用时)

更新多个影子寄存器时应禁用更新

通过AEI或ARU写入影子寄存器

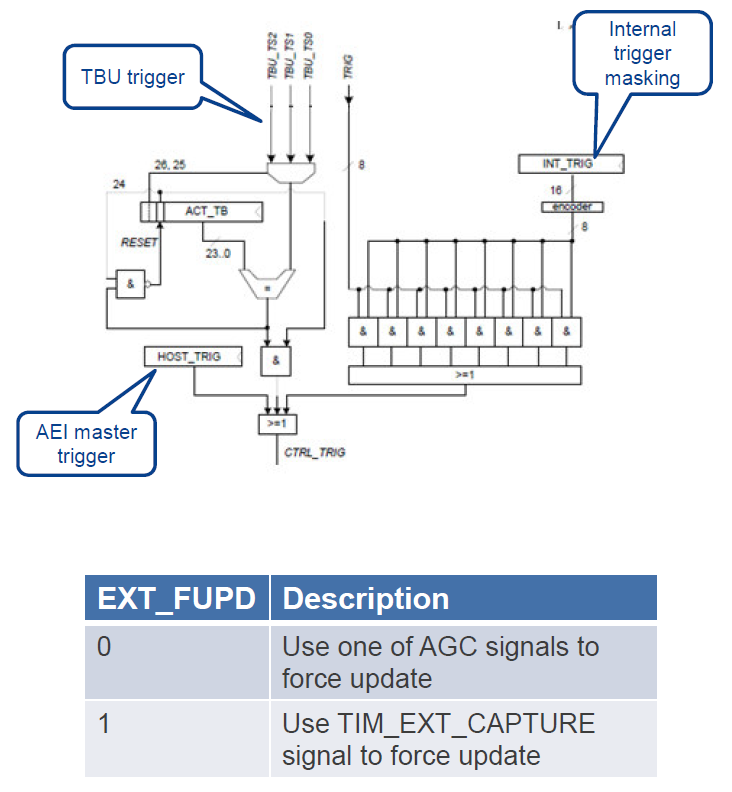

触发方式:

Host CPU (HOST_TRIG)

TBU时间戳匹配(ACT_TB)

内部触发- From CCU0 on CN0 reset (CN0 >= CM0, end of a period)

- From ATOM[x-1] (INT_TRIG)

- From TIM_EXT_CAPTURE of TIM channel (EXT_FUPD)

SYNCHRONOUS UPDATE BY ARU

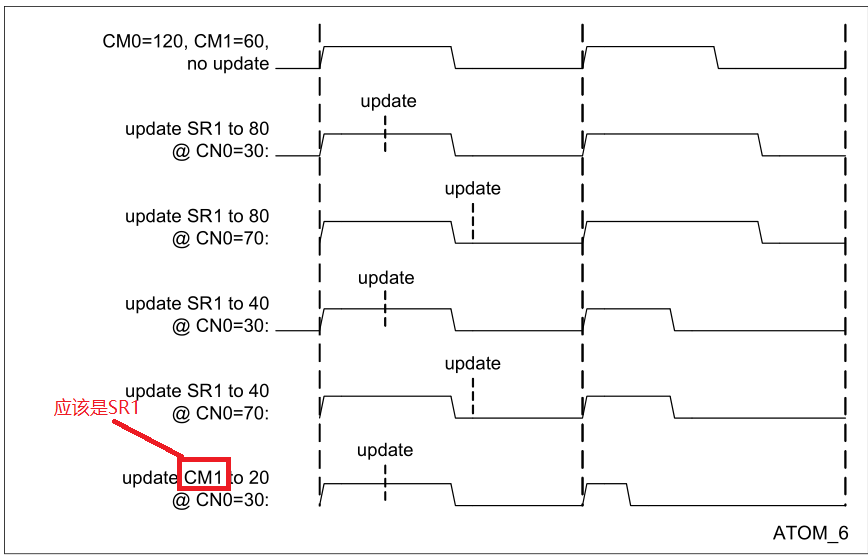

同步更新示例

同步更新:如下图所示,通过对SR1寄存器值更新,使得ATOM输出在下一个周期才同步一起更新CM1ASYNCHRONOUS UPDATE

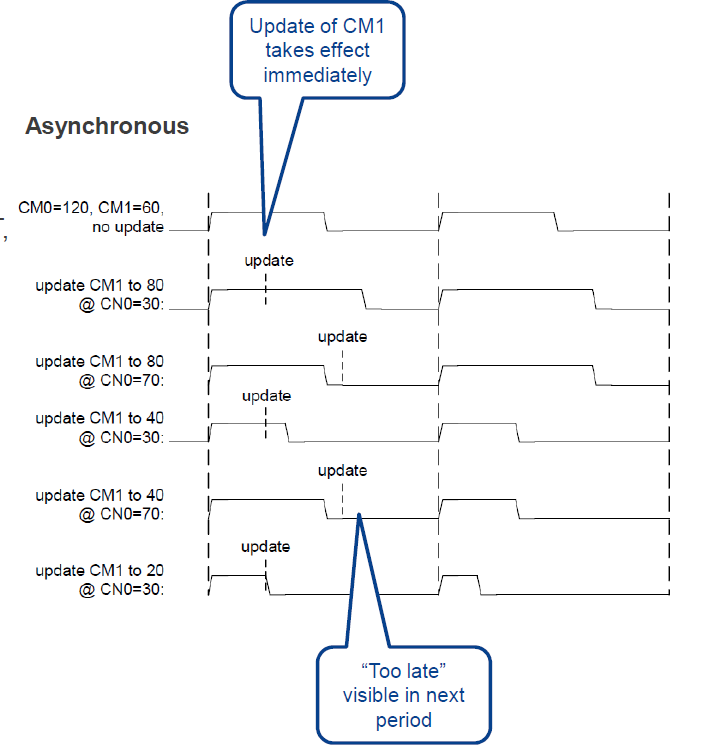

只能通过AEI外围总线主机(CPU, DMA)实现

直接写入工作寄存器CM0, CM1, ENDIS_STAT, OUTEN_STAT

新设置立即生效(无一致性)

通过直接对CM1寄存器值更新,使得ATOM输出可能在本次周期内输出就发生改变。ATOM Interrupt signals

ATOM Register overview

ATOM Register description

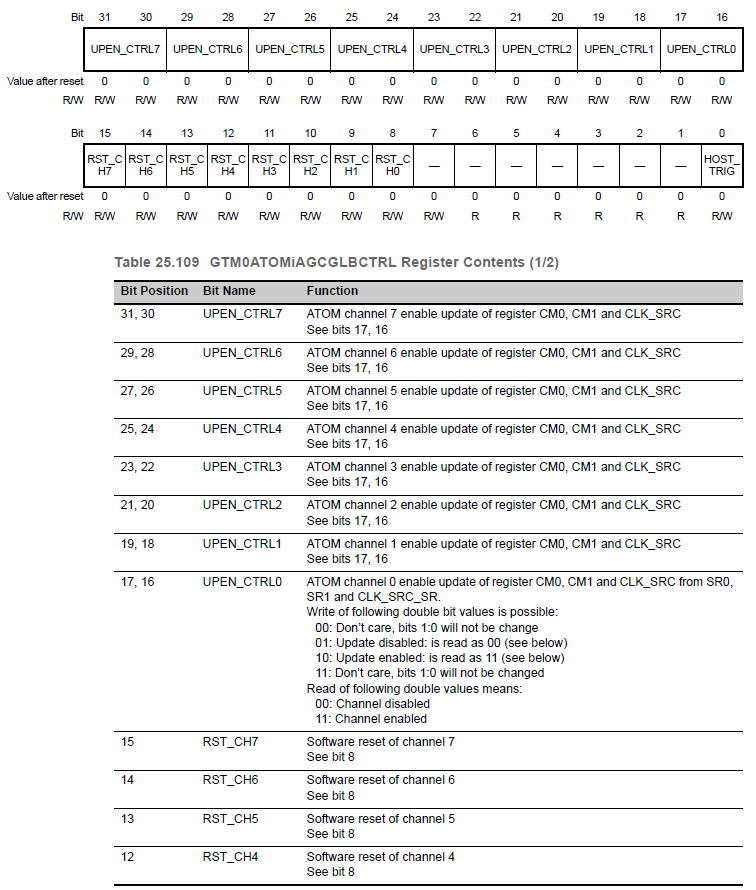

GTM0ATOMiAGCGLBCTRL (i = 0 to 2)

使能通道更新CM0, CM1 and CLK_SRC

UPEN_CTRL:

RST_CH:写1后会复位对应的通道

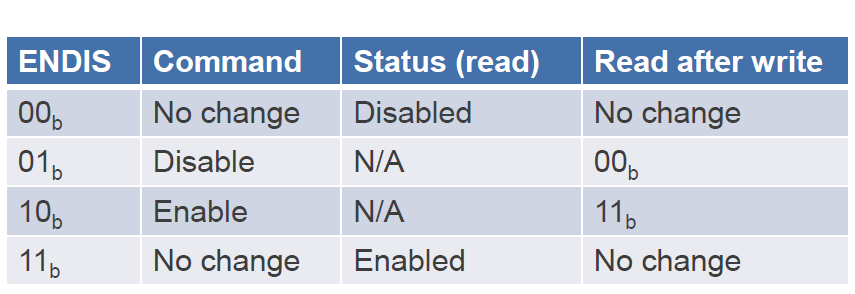

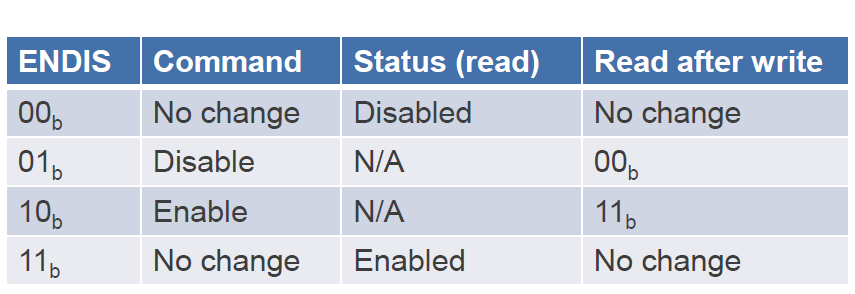

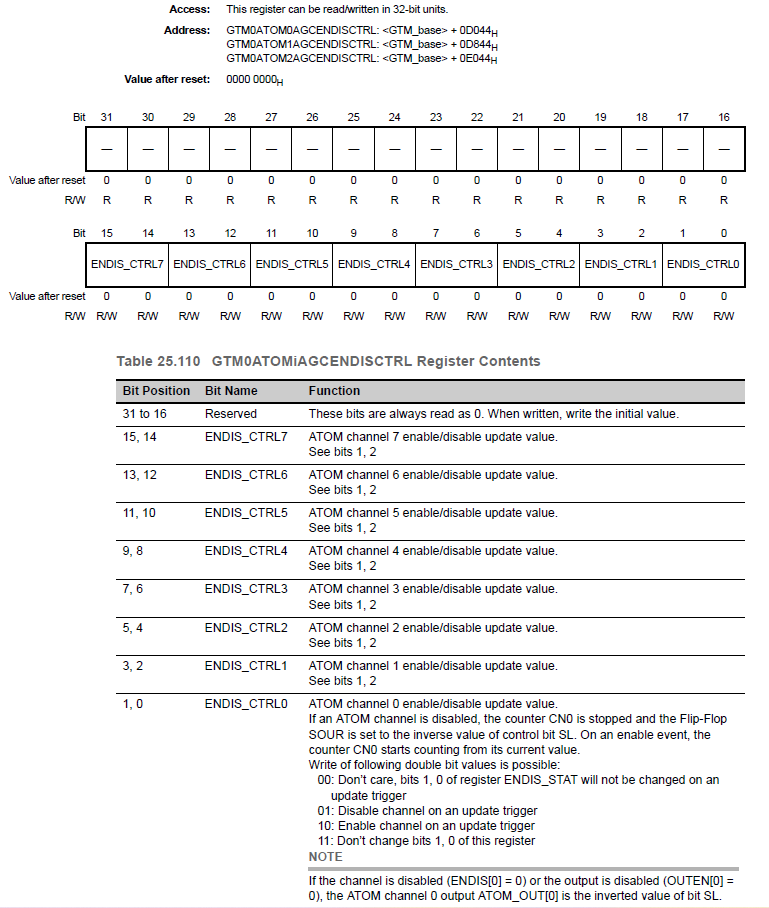

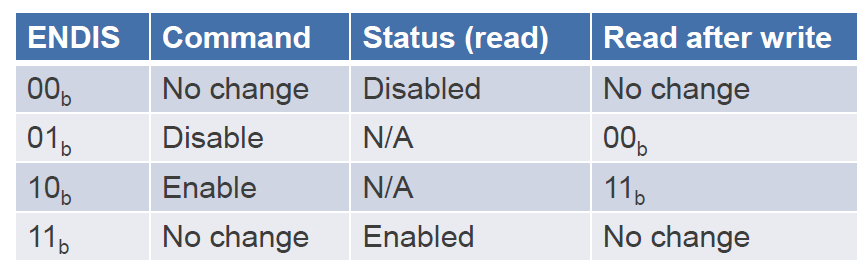

HOST_TRIG:触发请求信号(参见AGC)来更新寄存器ENDIS_STAT和OUTEN_STATGTM0ATOMiAGCENDISCTRL (i = 0 to 2)

ENDIS_CTRL:使能通道通过trigger更新值

GTM0ATOMiAGCENDISSTAT (i = 0 to 2)

ENDIS_STAT:使能通道

GTM0ATOMiAGCACTTB (i = 0 to 2)

TBU_SEL:选择对应的TBU_TS

TB_TRIG:trigger触发位,触发后会自动clear

ACT_TB:设置与TBU_TS[x]的比较值,TBU_TS[x]大于该值时产生触发信号GTM0ATOMiAGCOUTENCTRL (i = 0 to 2)

OUTEN_CTRL:使能通道输出由update trigger触发GTM0ATOMiAGCOUTENSTAT (i = 0 to 2)

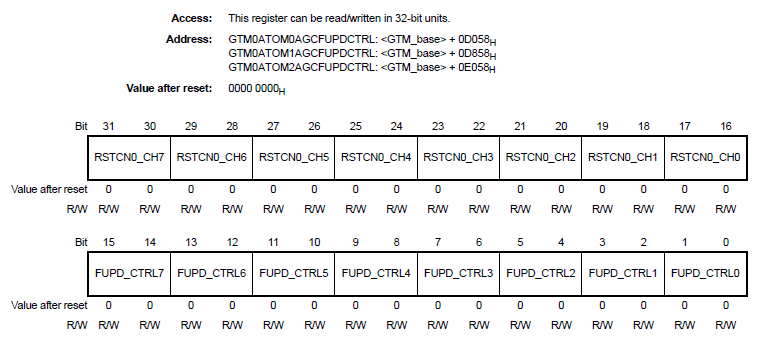

使能通道输出GTM0ATOMiAGCFUPDCTRL (i = 0 to 2)

RSTCN0_CHx:强制更新事件时重置通道x的CN0

FUPD_CTRL0:是否使能强制更新ATOM通道0操作寄存器

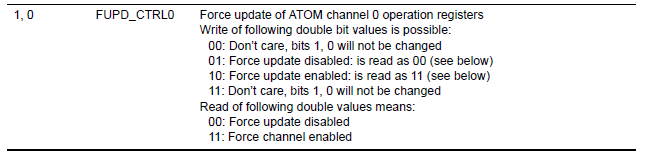

GTM0ATOMiAGCINTTRIG (i = 0 to 2)

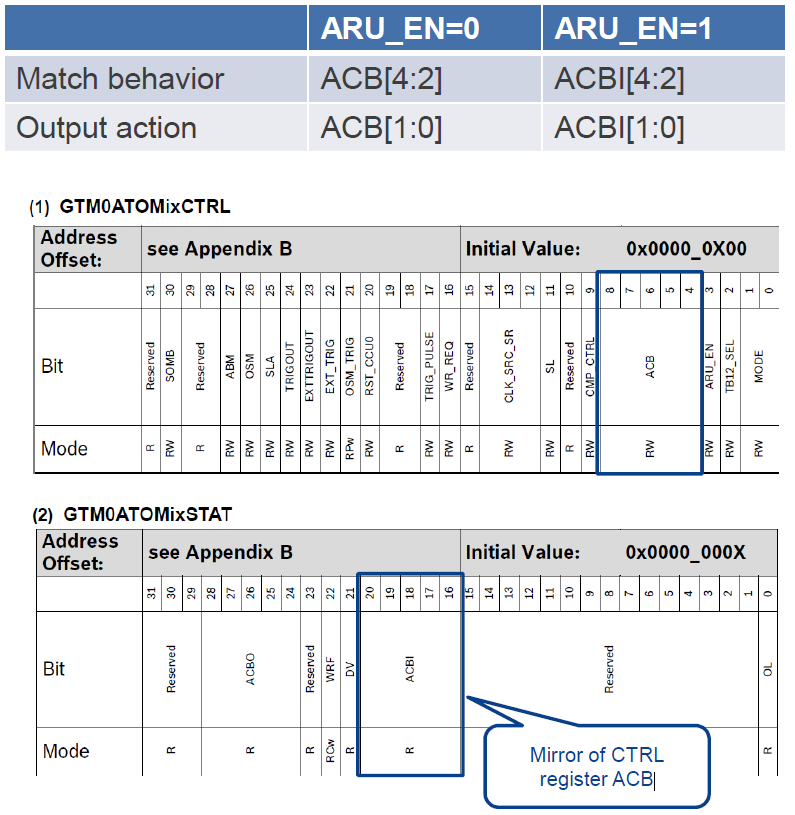

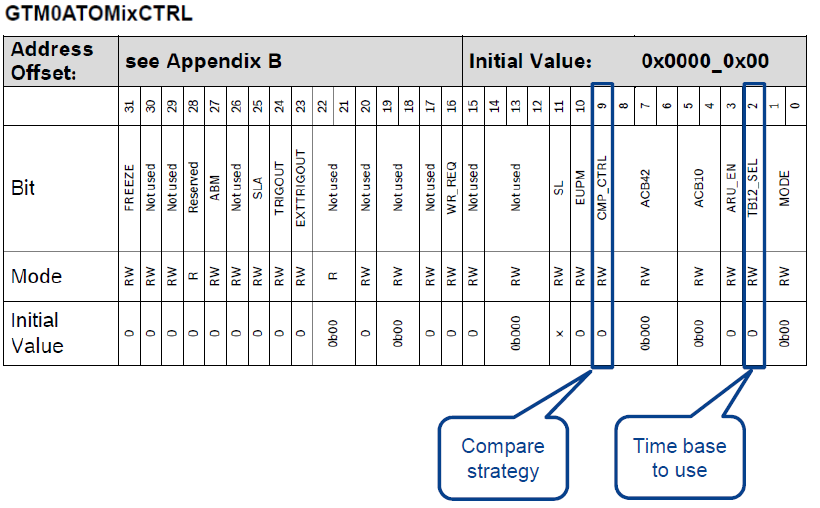

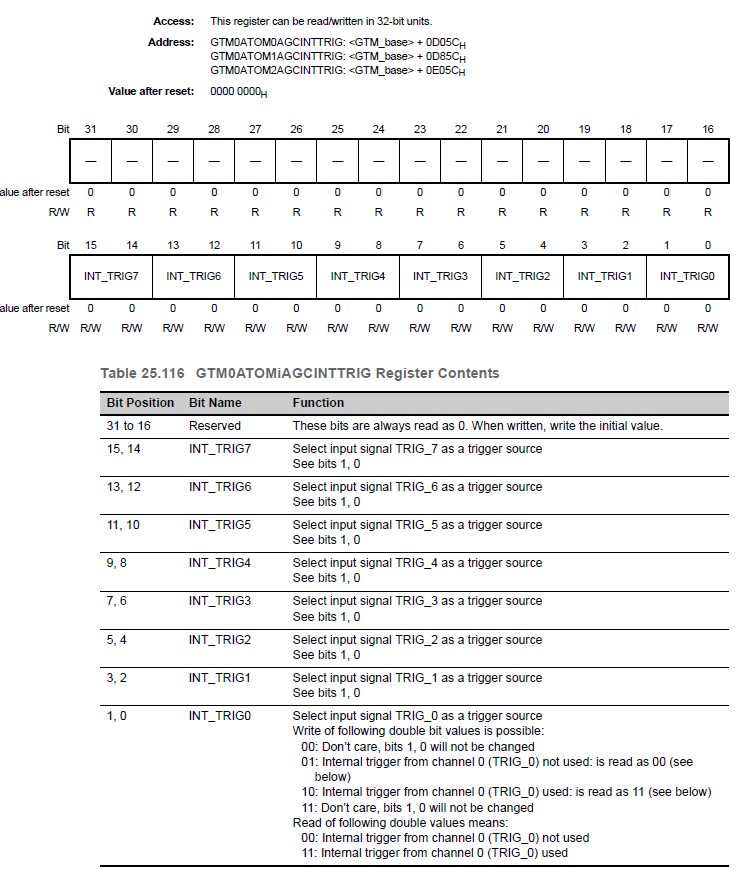

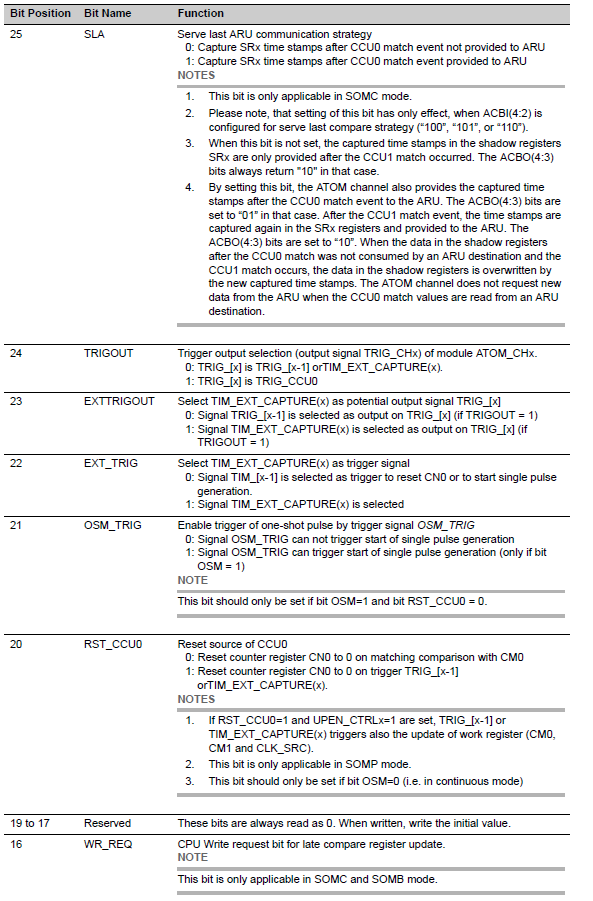

INT_TRIGx:选择输入信号TRIG_x作为触发源GTM0ATOMixCTRL (i = 0, x = 0 to 7,i = 1, x = 0 to 7,i = 2, x = 0 to 4)

SOMB:使能SOMB功能

ABM:ARU阻塞方式

0:禁用ARU阻塞模式:ATOM连续地从ARU读取并更新CM0, CM1,独立于挂起的比较匹配事件

1:使能ARU阻塞模式:通过ARU更新CM0、CM1后,不从ARU读取新的数据,直到发生比较匹配事件

OSM:单次还是连续

SLA:执行Serve last ARU通信策略

0:捕获未提供给ARU的CCU0匹配事件后的SRx时间戳

1:捕获提供给ARU的CCU0匹配事件后的SRx时间戳

此位仅适用于SOMC模式。

TRIGOUT:选择输出trigger的方式,0-选择前一个通道的trigger,1-由CN0到达CM0触发

EXTTRIGOUT:选择TIM_EXT_CAPTURE(x)作为备用输出信号TRIG_[x]

0:信号TRIG_[x-1]被选择作为TRIG_[x]的输出(如果TRIGOUT = 1)

1:选择信号TIM_EXT_CAPTURE(x)作为TRIG_[x]的输出(如果Trigout = 1)

EXT_TRIG:选择TIM_EXT_CAPTURE(x)作为触发信号

0:选择信号TIM_[x-1]作为触发器,复位CN0或开始单脉冲产生。

1:选择“信号TIM_EXT_CAPTURE(x)”

OSM_TRIG:启用触发信号OSM_TRIG触发单次脉冲

0:信号OSM_TRIG不能触发单脉冲产生启动

1:信号OSM_TRIG可以触发单脉冲生成启动(仅当位Osm = 1)

RST_CCU0:选择CN0的复位方式,0-CN0达到CM0复位,1-通过前一个通道的trigger复位

WR_REQ:CPU写请求位用于后期比较寄存器更新。(此位仅适用于SOMC和SOMB模式。)

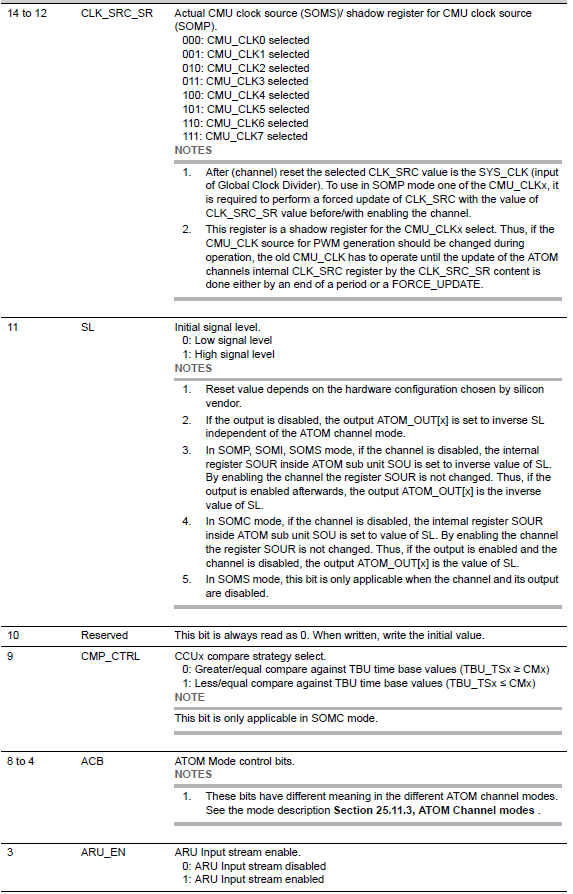

CLK_SRC_SR:选择通道时钟,该时钟作为CN0计数用。

SL:选择输出的占空比的有效电平为高还是低

CMP_CTRL:CCUx比较策略选择。

0:与TBU时间基准值比较大于等于(TBU_TSx≥CMx)

1:与TBU时间基准值比较小于/等于(TBU_TSx≤CMx)

ACB:ATOM模式控制位。

ARU_EN:ARU输入流使能。

0:关闭ARU输入流

1:表示ARU输入流使能

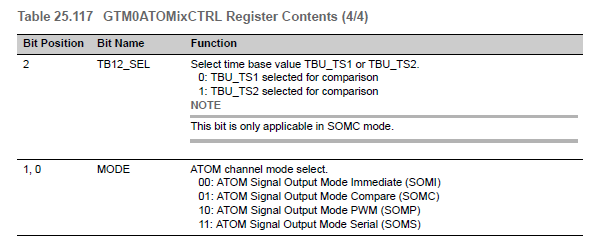

TB12_SEL:选择时间基准值TBU_TS1或TBU_TS2。

0:选择TBU_TS1进行比较

1:选择TBU_TS2进行比较

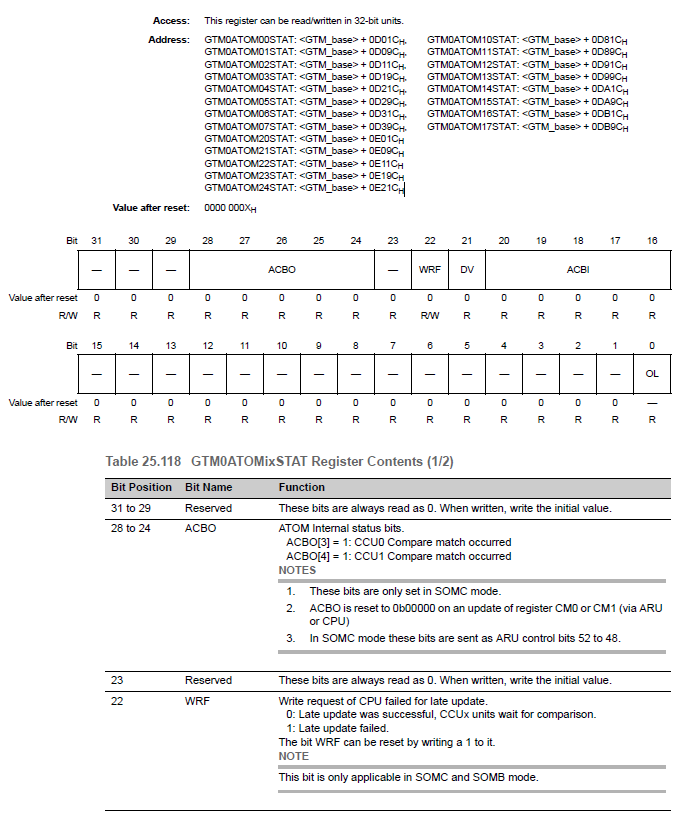

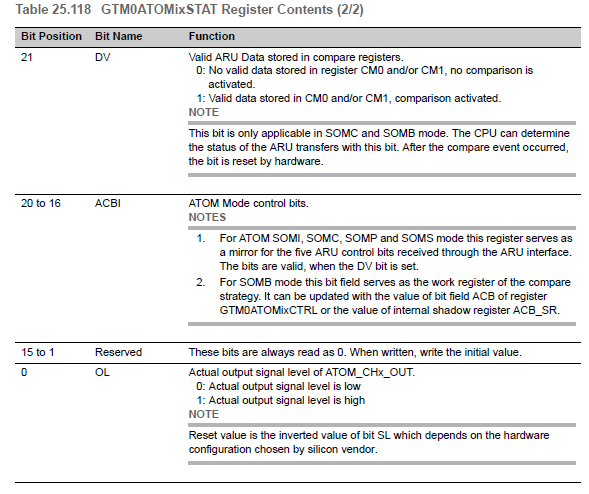

MODE:选择ATOM通道模式。GTM0ATOMixSTAT (i = 0, x = 0 to 7,i = 1, x = 0 to 7,i = 2, x = 0 to 4)

ACBO:ATOM内部状态位。

ACBO[3] = 1: CCU0比较匹配发生

ACBO[4] = 1: CCU1比较匹配发生

WRF:CPU写请求失败,延迟更新。

0:后期更新成功,CCUx单元等待比较。

1:后期更新失败。

DV:存储在比较寄存器中的有效ARU数据。

0:寄存器CM0和/或CM1中没有存储有效数据,没有激活比较。

1:有效数据存储在CM0和/或CM1中,启动比较

ACBI:ATOM模式控制位。

OL:ATOM_CHx_OUT的实际输出信号电平。

0:实际输出信号电平低

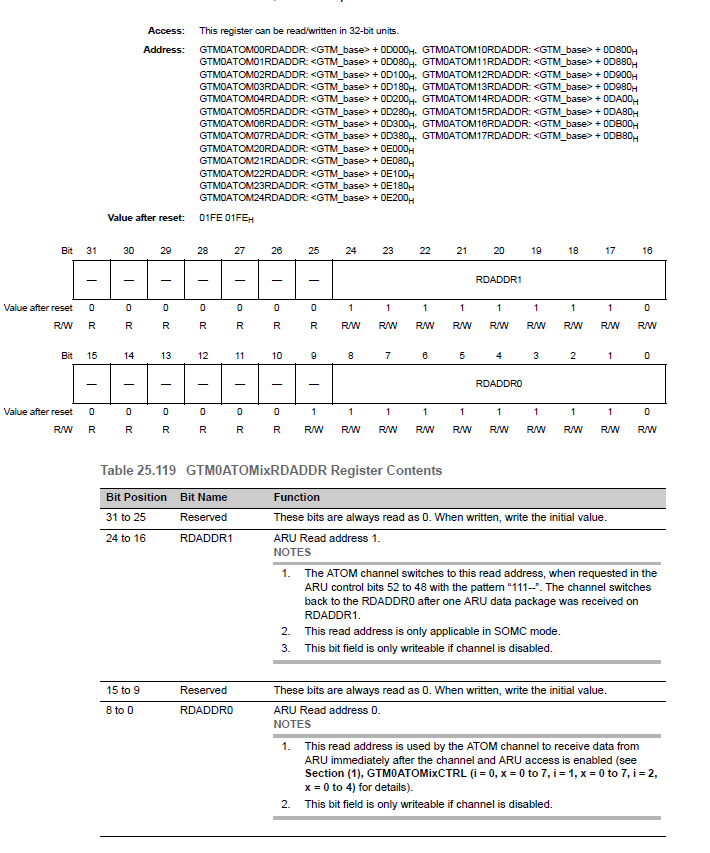

1:实际输出信号电平高GTM0ATOMixRDADDR

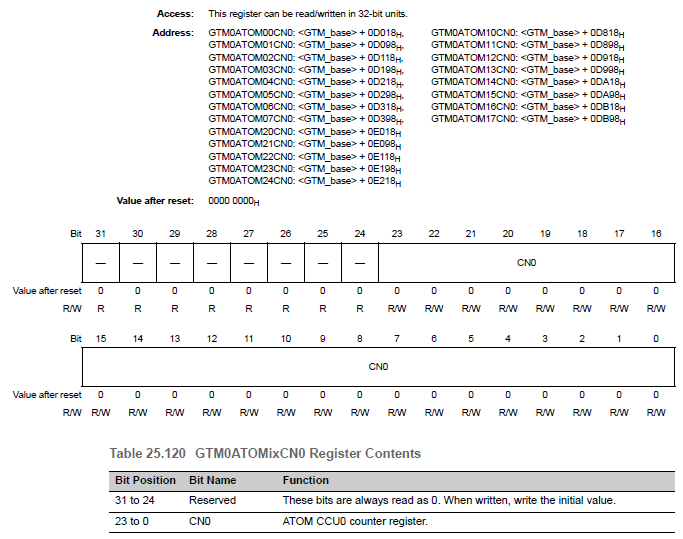

RDADDR1/0:ARU读地址1/0。GTM0ATOMixCN0

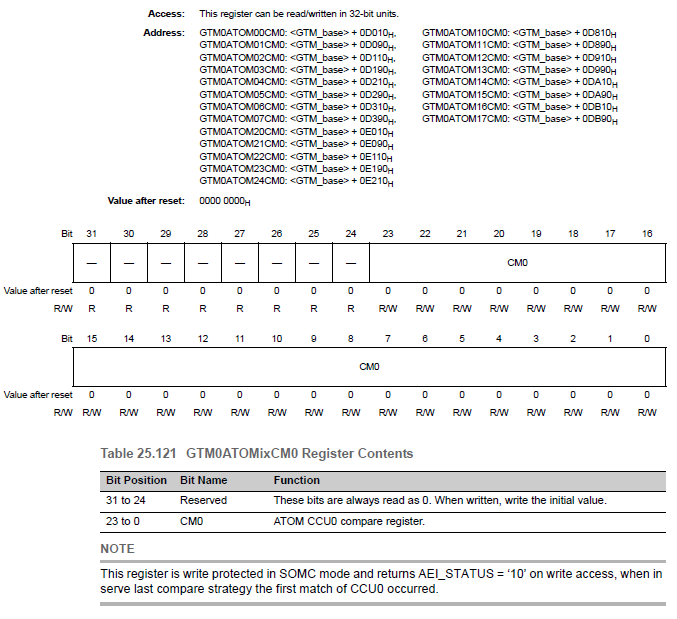

CN0:ATOM计数寄存器GTM0ATOMixCM0

CM0:ATOM CCU0比较寄存器,用来设置周期。GTM0ATOMixSR0

SR0:CM0的影子寄存器,ATOM同步更新时使用GTM0ATOMixCM1

CM1:ATOM CCU1比较寄存器,设置为0时表示占空比0%。GTM0ATOMixSR1

SR1:CM1的影子寄存器,TOM通道同步更新时使用GTM0ATOMixIRQNOTIFY (x = 0 to 7)

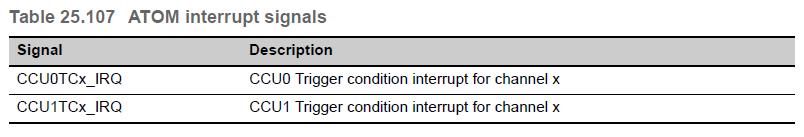

CCU1/0TC:CCU1/0通道x触发条件中断。

0:没有中断。

1: CCU1/0触发条件中断被ATOM通道x触发,CCU0在周期触发,CCU1在占空比到达时触发GTM0ATOMixIRQEN (x = 0 to 7)

CCU1/0TC_IRQ_EN:ATOM_CCU1/0TC_IRQ中断使能。

0:关闭中断,中断在GTM-IP之外不可见。

1:使能中断,中断在GTM-IP外可见。GTM0ATOMixIRQFORCINT (x = 0 to 7)

TRG_CCU1/0TC:通过软件触发ATOM_CCU1/0TC_IRQ中断。GTM0ATOM00IRQMOD (x = 0 to 7)

IRQ_MODE:IRQ模式选择

00:电平模式

01:脉冲模式

10:脉冲通知模式

11:单脉冲模式 -

相关阅读:

图像处理与计算机视觉--第四章-图像滤波与增强-第一部分

HDLbits exercises 7(Arithmetic Circuits节选题)

【关于Linux中----进程控制和进程替换】

VR全景如何助力乡村振兴,乡村发展在哪些方面用到VR全景技术

【墨染】找特有姿态!基于【灵茶山艾府】题解的补充图解

十大排序算法汇总

五年数据库专家,深入剖析高性能MySQL架构系统,不来后悔一辈子

python3彻底卸载与安装教程

@Accessors 注解作用

数据增强:Simple Questions Generate Named Entity Recognition Datasets

- 原文地址:https://blog.csdn.net/weixin_49000276/article/details/136435452