-

SystemVerilog学习 (5)——接口

一、概述

验证一个设计需要经过几个步骤:

- 生成输入激励

- 捕获输出响应

- 决定对错和衡量进度

但是,我们首先需要一个合适的测试平台,并将它连接到设计上。

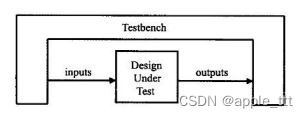

测试平台包裹着设计,发送激励并且捕获设计的输出。测试平台组成了设计周围的“真实世界”,模仿设计的整个运行环境。例如,一个处理器模型需要连接到不同的总线和器件,这些总线和器件在测试平台中就被建模成总线功能模型。一个网络设备连接到多个输人和输出数据流,这些数据流根据标准的协议建模。一个视频芯片连接到送入指令的总线,然后根据写入内存模型的数据重建图像。这里的核心概念是除了待测设计(DUT,Design Under Test)的行为之外,测试平台仿真了其他的所有行为。

由于Verilog的端口描述繁琐,代码常会长达数页,并且容易产生连接错误,所以测试平台需要一种更高层次的方法来跟设计建立通信。你需要一种可靠的描述时序的方法,这样就可以在正确的时间点驱动和采样同步信号,避免Verilog模型中常见的竞争状态。在进行验证的时候,我们尽量希望能够把设计部分和验证的部分分成,这里就会涉及到两个部分的连接问题,使用verilog的大家应该都知道,在verilog中对于端口的连接来说是一件非常枯燥和繁琐的事情,对于一个大的设计来说,端口的连接是非常耗时和易错的。SystemVerilog在这方面引入了接口来简化这一步骤。

二、接口interface

在介绍接口之前,首先说明一个细节,我们知道在verilog中数据类型可以分成wire和reg两种,但是在SystemVerilog中,我们通过logic来取代了reg,唯一不能使用logic的地方是具有多个驱动的连线,只有在这种情况下,我们需要使用wire类型,其他时候,我们在SystemVerilog中都可以使用logic来实现。

1、接口的优势

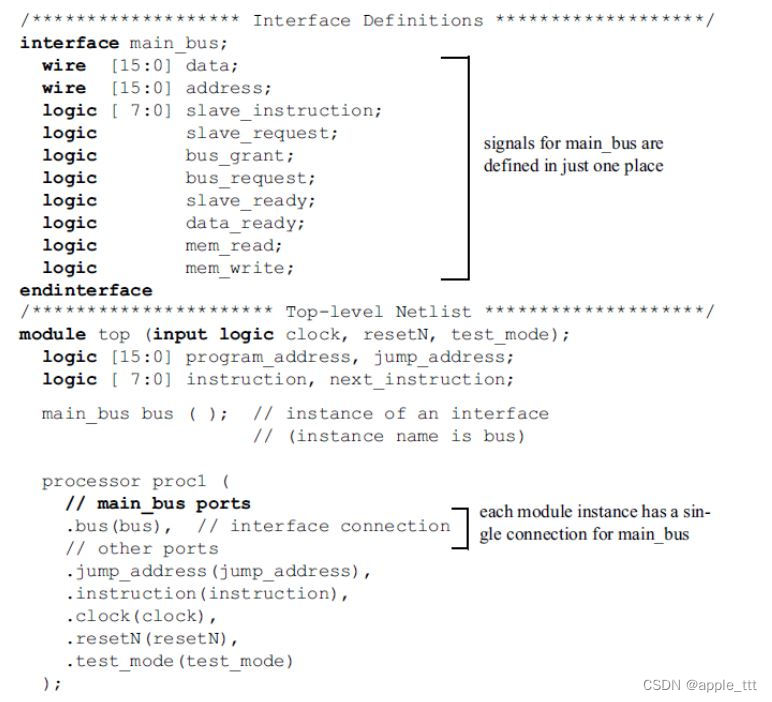

· 对于接口来说,信号只需要在接口中定义一次,在之后的模块调用的过程中,就可以直接通过接口的方式进行连接了。

2、接口的内容

- 接口不单单包含变量和线网,它还可以封装模块之间通信的协议

- 此外接口中还可以嵌入与协议有关的断言检查、功能覆盖率收集等模块

- 接口不同于模块(module)的地方在于,接口不允许包含设计层次,即接口无法例化module,但是接口可以例化接口

- 接口中可以进一步声明modport来约束不同模块连接时的信号方向

3、接口的声明

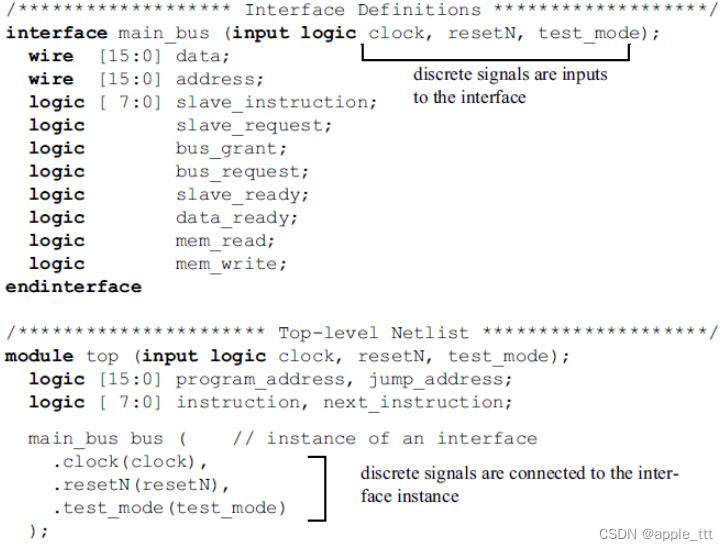

接口的定义和模块的定义是相似的,接口有时候也会有端口,经常是外部输入的时候或者复位信号等,接口内部也可以定义所有的变量或者线网类型。

4、接口的例化

接口的例化方式和模块的例化是一致的, 需要注意的是:模块的端口如果声明为input、output或者inout,那么在例化时可以不连接。 模块的端口如果声明为interface,那么在例化时则必须连接到一个接口实例,或者另外一个接口端口。

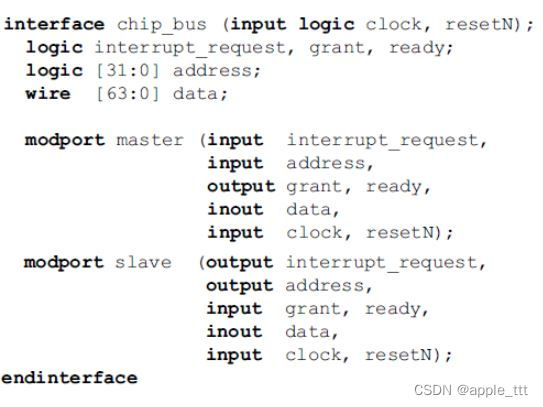

5、modport

接口中的变量或者线网信号,对于连接到该接口的不同模块则可能具备不同的连接方向。 接口引入了modport来作为module port的缩写,表示不同的模块看到同一组信号时的视角(连接方向)。在接口中声明modport,需要指明modport中各个信号的方向。

当一个模块在例化时,可以选择连接到interface端口中具体的某一个modport。 这种方式可以降低方向连接错误的可能,进而避免信号多驱动的情况。

三、 总结

在接口中不能例化模块,但是可以例化其他接口。带有modport的接口跟传统的连接到信号的端口相比各有千秋。

1.、接口的优势

使用接口的优势如下:

(1)接口便于设计重用。当两个块之间有两个以上的信号连接,并且使用特定的协议通信的时候,应当考虑使用接口。

(2)接口可以用来替代原来需要在模块或者程序中反复声明并且位于代码内部的一系列信号,减少了连接错误的可能性。

(3)要增加一个新的信号时,在接口中只需要声明一次,不需要在更高层的模块层声明。这进一步减少了错误。

(4)modport 允许一个模块很方便地将接口中的一系列信号捆绑到一起,也可以为信号指定方向以方便工具自动检查。

2、接口的劣势

使用接口的劣势如下:

(1)对于点对点的连接,使用modport的接口描述跟使用信号列表的端口一样的冗长。接口带来的好处是所有的声明集中在一个地方,减少了出错的几率。

(2)必须同时使用信号名和接口名,可能会使模块变得更加冗长。

(3〉如果要连接的两个模块使用的是一个不会被重用的专用协议﹐使用接口需要做比端口连线更多的工作。

(4〉连接两个不同的接口很困难。一个新的接口(bus_if)可能包含了现有接口(arb.if)的所有信号并新增了信号(地址.数据等等)。你需要拆分出独立的信号并正确地驱动它们。

-

相关阅读:

自制操作系统日记(6):静态桌面初步

期货怎么克服频繁止损(期货交易怎么止损)

JS解构赋值

【Python】【Torch】神经网络中各层输出的特征图可视化详解和示例

this是什么?为什么要改变this?怎么改变 this 指向?

Servlet---上传文件

KMP模式匹配算法

FITC标记Avidin亲和素;荧光素标记亲和素(FITC-Avidin);荧光素修饰亲和素;FITC-Avidin

LeetCode 3---Longest Substring Without Repeating Characters

进阶笔录-深入理解Java线程之Synchronized

- 原文地址:https://blog.csdn.net/apple_53311083/article/details/134417729