-

hdlbits系列verilog解答(7458芯片)-10

wire线网类型介绍

wire线网类型是verilog的一种数据类型,它是一种单向的物理连线。它可以是输入也可以是输出,它与reg寄存器数据类型不同,它不能存储数据,只能用于组合逻辑建模。常用于assign连续赋值语句。

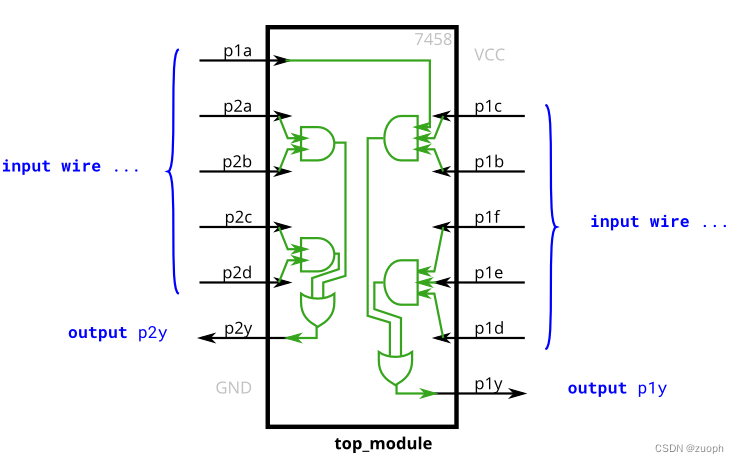

一、问题描述

创建与 7458 芯片具有相同功能的模块。它有 10 个输入和 2 个输出。可以选择使用 assign 语句来驱动每根输出导线,也可以选择声明 4 根线网数据用作中间信号,其中每根内部线网数据由其中一个 AND 门的输出驱动。

二、verilog源码

方法一:

// 直接输出

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );assign p1y = (p1a & p1b & p1c) | (p1d & p1e & p1f); assign p2y = (p2a & p2b) | (p2c & p2d);- 1

- 2

endmodule

方法二:

//使用内部线网数据wire

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );wire w1, w2, w3, w4; //assign p1y = (p1a & p1b & p1c) | (p1d & p1e & p1f); //assign p2y = (p2a & p2b) | (p2c & p2d); assign w1 = p1a & p1b & p1c; assign w2 = p1d & p1e & p1f; assign w3 = p2a & p2b; assign w4 = p2c & p2d; assign p1y = w1 | w2; assign p2y = w3 | w4;- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

endmodule

注:assign语句是连续赋值语句,它实现将右边的信号值驱动到左边信号上。同时多条语句之间没有先后之分,这就是verilog的并发性体现,不像C语言中语句是串行执行。另外 模块定义中的信号缺省是wire线网类型,除非后面另外申明。

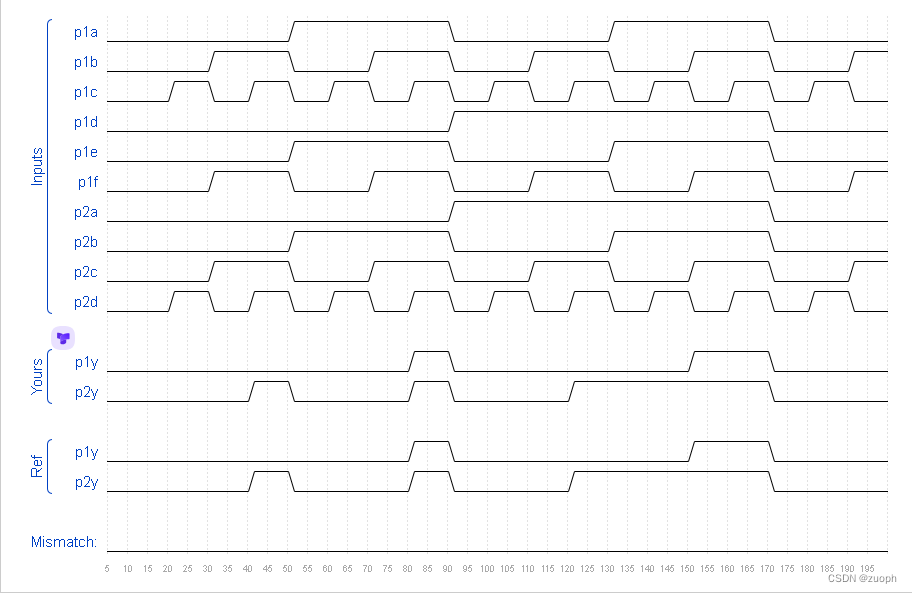

三、仿真结果

转载请注明出处!

-

相关阅读:

MATLAB图像批处理之图格式批量转换

数据链路层重点协议

01 【Vue简介 初识Vue 模板语法和数据绑定】

ElasticSearch ES 安装 常见错误 Kibana安装 设置 权限 密码

非零基础自学Java (老师:韩顺平) 第12章 异常 - Exception

Vue3使用dataV报错问题解决

SpringBoot/Spring扩展点系列之CommandLineRunner和ApplicationRunner实现缓存预热

Zookeeper-3.8.0单台、集群环境搭建

面试官:单核 CPU 支持 Java 多线程吗?为什么?被问懵了

【React】《React 学习手册 (第2版) 》笔记-Chapter3-JavaScript 函数式编程

- 原文地址:https://blog.csdn.net/zuoph/article/details/133966624