-

栅形状的影响及可靠性的优化

栅形状的影响

-

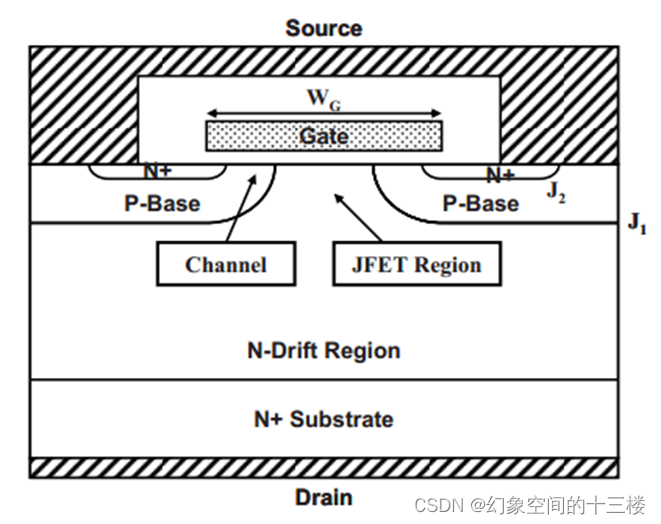

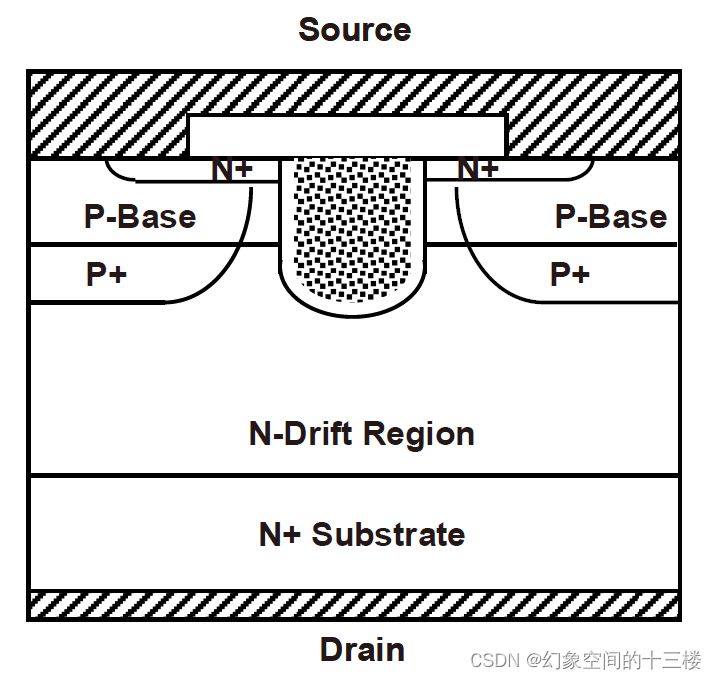

VD-MOSFET单元结构采用平面栅极拓扑结构,栅极电极位于半导体的平坦上表面。虽然在这种结构中,在平面结处会发生电场增强,但在栅极电极处不会发生电场增强,因为栅极电极的边缘与高度掺杂的N+源区重叠。栅极电极的边缘被N+源区的存在屏蔽了来自施加的漏极电位。此外,当栅极宽度减小时,栅极区域下方P-N结的存在会将其屏蔽在漏极偏压之外。在这些设计中,P-N结就像JFET结构的栅极区域,在栅极结构下方产生一个势垒。

-

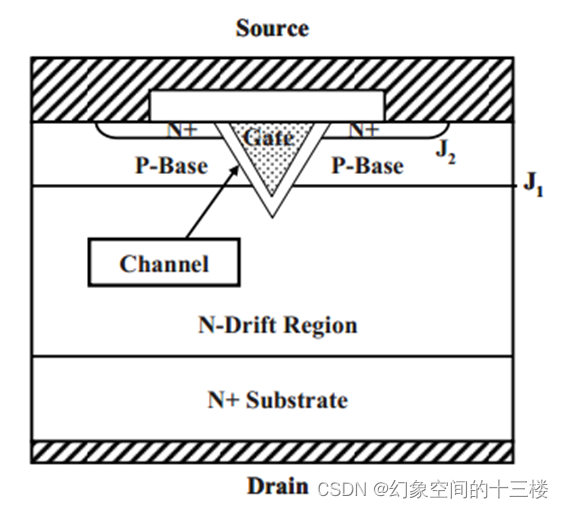

在V型沟功率MOSFET结构中,在栅极电极下方沟槽的底部形成一个尖锐的角落。为了使沟槽的尖端穿透结J1进入漂移区,从N+源到N漂移区的沟道必须延伸。在阻挡模式下工作时,最高的电场出现在结J1处。因此,V形沟的尖端位于结构内电场最高的地方。耗尽区内尖锐点的存在增强了电场,导致击穿电压降低。由于这个高电场位于沟道的边缘,因此从电场获得能量的电子会被发射到沟道附近的栅极氧化物中。被发射到氧化物中的电子被氧化物捕获,导致MOSFET的阈值电压发生偏移。因此,V型沟功率MOSFET结构容易出现热电子不稳定性问题。由于这些原因,V型沟功率MOSFET架构不再用于制造商用器件。

-

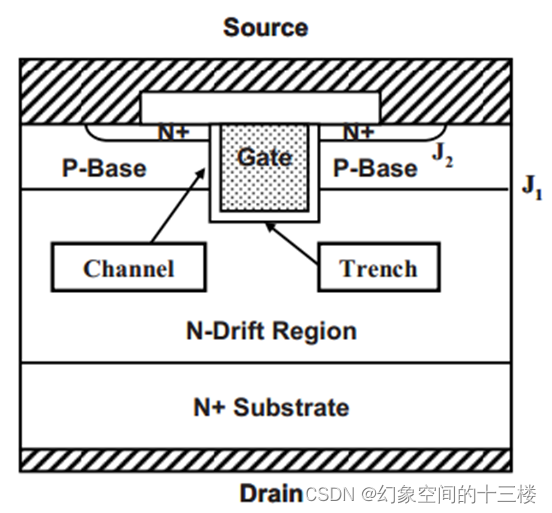

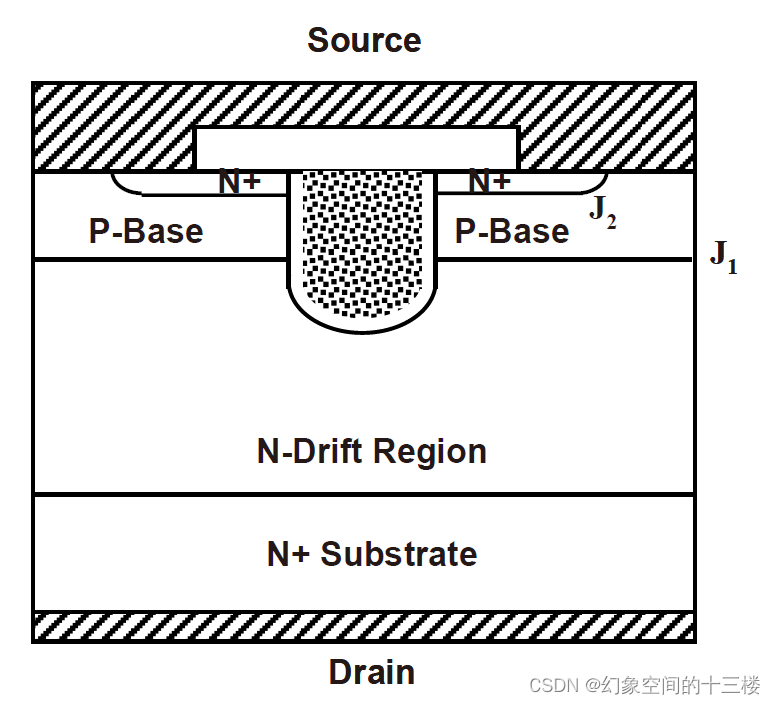

在U型MOSFET结构中,也可以在沟槽的拐角处产生高电场。在这种结构中,栅极必须从上表面穿过结J1,以形成从N+源区延伸到N漂移区的沟道。与V型沟结构一样,沟槽的底角位于支撑电压的结J1的附近。沟槽拐角处电场的增强会导致击穿电压降低和热电子不稳定性问题。这些问题可以通过将沟槽底部圆滑并添加深P+区来屏蔽沟槽拐角来克服。6虽然对提高击穿电压有效,但深P+区的存在会在U型MOSFET结构中引入一个JFET区,这会降低其导通电阻。

可靠性的优化

功率U-MOSFET结构的坚固性不如平面VD-MOSFET结构。在电感负载开关操作下,功率U-MOSFET器件失效的主要原因是沟槽尖角处产生的增强电场。这个问题可以通过圆滑沟槽底部来克服。

通过在功率U-MOSFET结构中添加深P+区,可以进一步提高其坚固性。P+区的存在降低了沟槽拐角处的电场。但是,重要的是将P+区限制在远离沟槽侧壁的地方,以防止阈值电压急剧上升。由于这些P+区必须在台面区内通过额外的掩模步骤形成,并且它们的深度必须超过P基区深度才能降低沟槽拐角处的电场,因此该结构的台面宽度会变得显著更大。对于P+区的1μm宽离子注入窗口,台面宽度必须扩大到5μm才能容纳2μm的扩散深度,这与沟槽深度相匹配。这使得单元间距变大,增加了沟道对导通电阻的贡献。此外,据报道,当这些深度区域与沟槽深度相当时,它们会在U-MOSFET结构中产生JFET效应。

-

-

相关阅读:

【硬件+软件】示波器的自动化控制

【小程序】首屏渲染优化

【c++刷题Day2】专题2线性DP

NFT的发展会止步于此吗?

RDD缓存机制及持久化技术

为什么说企业需要MES系统? MES系统的作用和意义是什么?

[HeMIM]Cl,[AeMIM]Br,[CeEIM]Cl,([HO-PECH-MIM]Cl,[HOOC-PECH-MIM]Cl改性酚醛树脂

【YOLO】物体识别算法的核心思想

CV&NLP基础9之卷积神经网络CNN入门

数理统计笔记6:假设检验

- 原文地址:https://blog.csdn.net/weixin_45293089/article/details/133712941