-

计算机考研 | 2020年 | 计算机组成原理真题

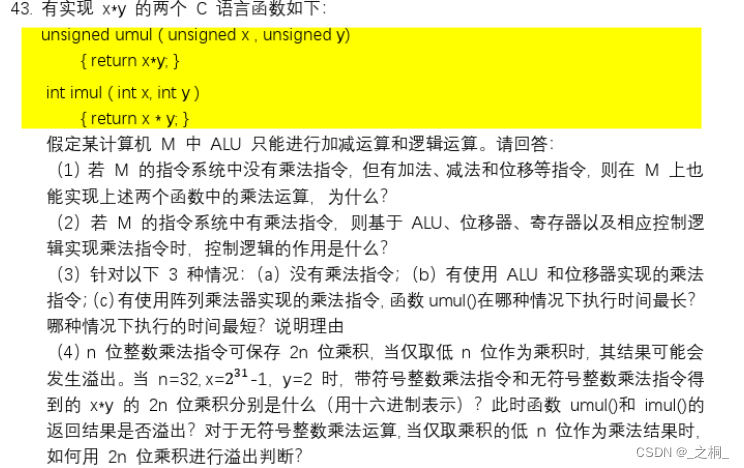

【计算机组成原理2020年真题43题-13分】

【第一步:信息提取】

【第二步:具体解答】

第一小题:

(1)若M的指令系统中没有乘法指令.但有加法、减法和位移等指令,则在M上也能实现上述两个函数中的乘法运算.为什么?

乘法运算也可以通过加法操作和移位操作实现x*y可视为y个×或×个y相加的结果

第二小题:

(1)若M的指令系统中有乘法指令,则基于ALU、位移器、寄存器以及相应控制逻辑实现乘法指令时,控制逻辑的作用是什么?

实现相加和移位的控制

第三小题:

(1)针对以下3种情况:

- (a)没有乘法指令;

- (b)有使用ALU和位移器实现的乘法指令;

- (c)有使用阵列乘法器实现的乘法指令

函数umul()在哪种情况下执行时间最长?哪种情况下执行的时间最短?说明理由

最长: a;最短: c

a)情况下执行时间最长,需要利用其他指令来实现乘法功能

b)情况下使用了ALU与位移器,由多次相加及位移操作串行实现乘法操作

c)情况使用阵列乘法器做并行乘法运算,时间显然最快

第四小题:

(1)n位整数乘法指令可保存2n位乘积,当仅取低n位作为乘积时,其结果可能会发生溢出。当n=32,x= 2 31 − 1 2^{31}-1 231−1,y=2时,带符号整数乘法指令和无符号整数乘法指令得到的x*y的2n位乘积分别是什么(用十六进制表示)?

带符号整数指令乘法:

7FFF FFFFH * 2 = 0000 0000 FFFF FFFEH

无符号整数指令乘法:

7FFF FFFFH *2 = 0000 0000 FFFF FFFEH

(2)此时函数 umul() 和 imul() 的返回结果是否溢出?对于无符号整数乘法运算,当仅取乘积的低n位作为乘法结果时,如何用2n位乘积进行溢出判断?

umul(返回)FFFF FFFEH未溢出

imul(返回) FFFF FFFEH有溢出(结果成了负数)

高n位全0则未产生溢出,否则产生溢出

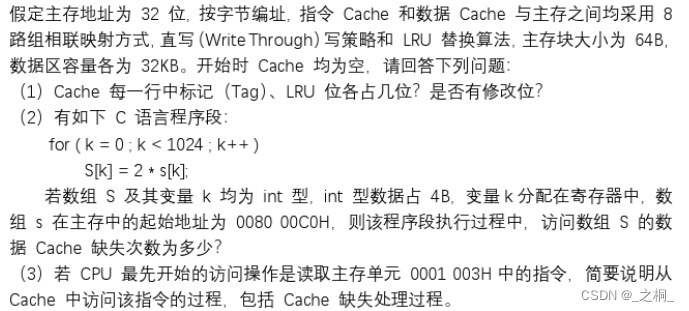

【计算机组成原理2020年真题44题-10分】

【第一步:信息提取】

1、主存地址为32位,按字节编址: 地址线有32条,单位是字节

2、指令Cache 和数据Cache 与主存之间均采用8路组相联映射方式: 一般来说,看到8路组相联应该想到组编号有3位。但是后面又提到了数据区容量和主存储块容量。所以编号应该为:32KB/(64B*8)=64= 2 6 2^6 26;一共64组,每组8个主存块。所以编号为6位。

3、直写(Write Through)写策略和LRU替换算法: ①当 CPU 要将数据写入内存时,除了更新缓冲内存上的数据外,还要数据写在 DRAM 中,以维持主存与缓冲内存的一致性;②最近最少使用,是一种常用的页面置换算法,因为每组有8个主存块,所以占3位

4、主存块大小为64B,数据区容量各为32KB: 块内地址6位;数据区容量15位

5、开始时Cache均为空。

【第二步:具体解答】

第一小题:

(1)Cache 每一行中标记(Tag)、LRU位各占几位?是否有修改位?

主存块大小为64B = 2 6 2^6 26字节,所以主存地址低6位为块内地址,

Cache 组数为 32 K B / ( 64 B × 8 ) = 64 = 2 6 32KB/(64B×8)=64= 2^6 32KB/(64B×8)=64=26,故主存地址中间6位为Cache组号

主存地址中高32-6-6=20位为标记,采用8路组相联映射,故每行中的LRU位占3位,采用直写方式,故没有修改位。

第二小题:

(1)有如下C语言程序段:

for ( k = 0 ; k <1024 ; k++ ) S[k]= 2* s[K];- 1

- 2

若数组S及其变量k 均为int 型, int型数据占4B,变量k分配在寄存器中,数组s 在主存中的起始地址为0080 00C0H,则该程序段执行过程中,访问数组S 的数据Cache缺失次数为多少?

0080 00C0H =0000 0000 1000 0000 0000 0000 1100 0000B,主存地址的低6位,为块内地址,为全0,故s位于一个主存块的开始处,占1024×4B/64B=64个主存块

在执行程序段的过程中,每个主存块中的64B/4B= 16个数组元素依次读、写1次,因而对每个主存块,总是第一次访问缺失,此时会将整个主存块调入 Cache,之后每次都命中。综.上,数组s 的数据Cache 访问缺失次数为64次。

第三小题:

(1)若 CPU最先开始的访问操作是读取主存单元 0001 003H中的指令,简要说明从Cache 中访问该指令的过程,包括Cache缺失处理过程。

0001 0003H = 0000 0000 0000 0001 0000 000000 000011B,根据主存地址划分可知,组索引为0,故该地址所在主存块被映射到指令Cache的第0组

因为Cache初始为空,所有Cache行的有效位均为0,所以Cache访问缺失。

此时,将该主存块取出后存入指令Cache的第0组的任意一行,并将主存地址高20位

(00010H)填入该行标记字段,设置有效位,修改LRU位,最后根据块内地址 000011B从该行中取出相应的内容。

-

相关阅读:

【微信小程序】前端+后端 :第一篇(基于javaweb 案例)

stm32f103r8t6单片机烧录问题“Flash Time out.”

SpringBoot使用自定义注解+AOP+Redis实现接口限流

【4.2 集中趋势&离散趋势】(描述性统计分析)——CDA

【1】MongoDB的安装以及连接

养生产品如何进行线上推广?产品线上推广的渠道有哪些?

七夕节赚徽章拉

android 离线语言合成(文字转语音)

SpringMVC异常处理

栩栩如生,音色克隆,Bert-vits2文字转语音打造鬼畜视频实践(Python3.10)

- 原文地址:https://blog.csdn.net/xt199711/article/details/133561715