-

去耦电路设计应用指南(四)电源 PDN 配置

(四)电源 PDN 配置

电源走线与去耦电路的以及 MCU 终端的连接作为一个整体就叫做 PDN,PDN 的性能指 标之一就是 MCU 电源终端 PDN 上的阻抗。MCU 电源终端的 PDN 阻抗(电源阻抗)越 小,MCU 电流供应性能,电源完整性 PI 以及信号完整性 SI 就越高。电源阻抗越小,MCU 电源电流波动时的电压波动越小。

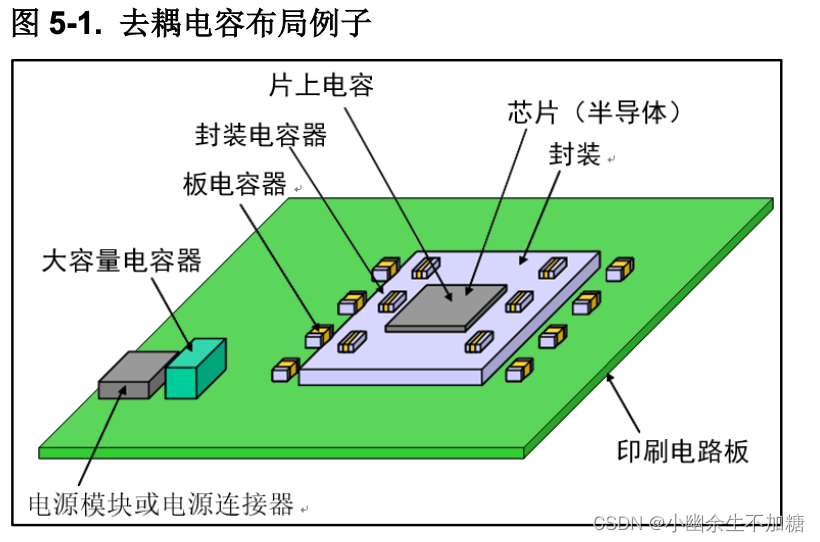

在高性能 MCU中,电源电流剧烈变化并且其频率 较高;电源阻抗在很宽的频率范围内必须变小。在这种情况下,如图 去耦电容布局例 子由于一个电容不能达到所需的阻抗,多层次的安装电容以达到目标源的阻抗。电容器的 分层定位以完成目标阻抗。

当电容器分层定位时,如图 去耦电容布局例子所示,每个电容器都是根据其所在位 置进行命名并且连接起来,如图 电容分层电流供应模式所示。片上电容(形成硅电 容)不是 PCB 上面的器件,但是被添加了,因为它有相同的功能。

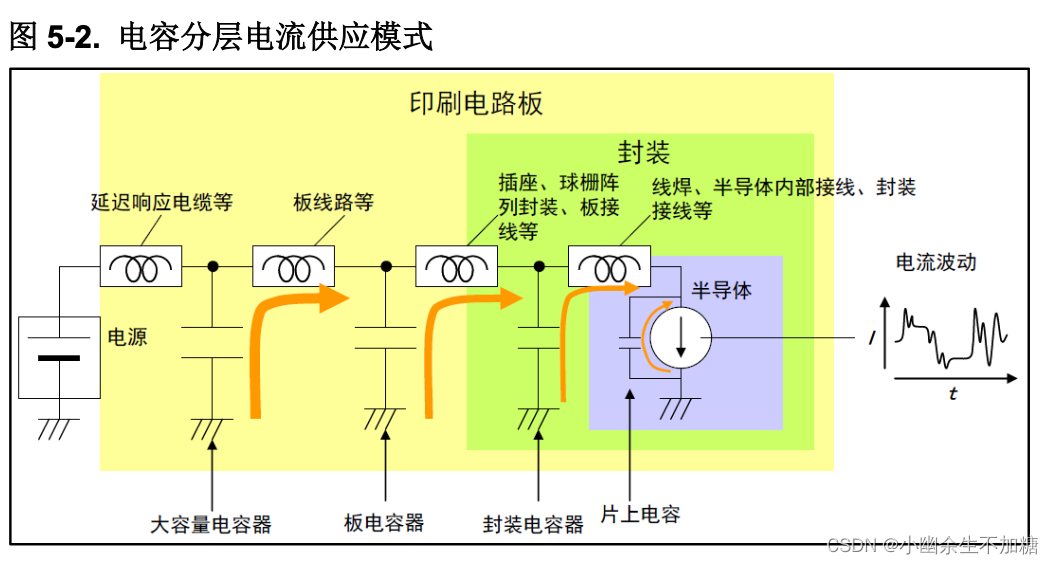

从 PDN 电源功能的观点上看,那些电容的功能就好比是“电荷的蓄水池”。换句话说,要 瞬间处理半导体附近的本地电流请求,电容可以维持电源模块的时间-至-响应以及电压。 另外,从电源阻抗的频率特性的观点上看,随着频率的增加,电源模块的阻抗在没有任何 帮助的情况下也增加,电容器放置在 IC 附近以减少高频率区域的阻抗。

除了有关 MCU 电源阻抗的电容器之外,我们需要考虑接线电感。

由于远端电容器的接线电感增大,高频下阻抗不能被减少。相反,我们可 以期望半导体旁的电容器在高频下处于有效状态。

从这个意义上讲,如果我们可以从片上电容上得到足够的电容,这对于减少电源阻抗将是 很理想的。事实上,由于空间限制,这是很难的。因此,我们从半导体的近端至远端,分 层放置电容器,如图 5-2. 电容分层电流供应模式所示,以达到目标电源阻抗。

1. PDN

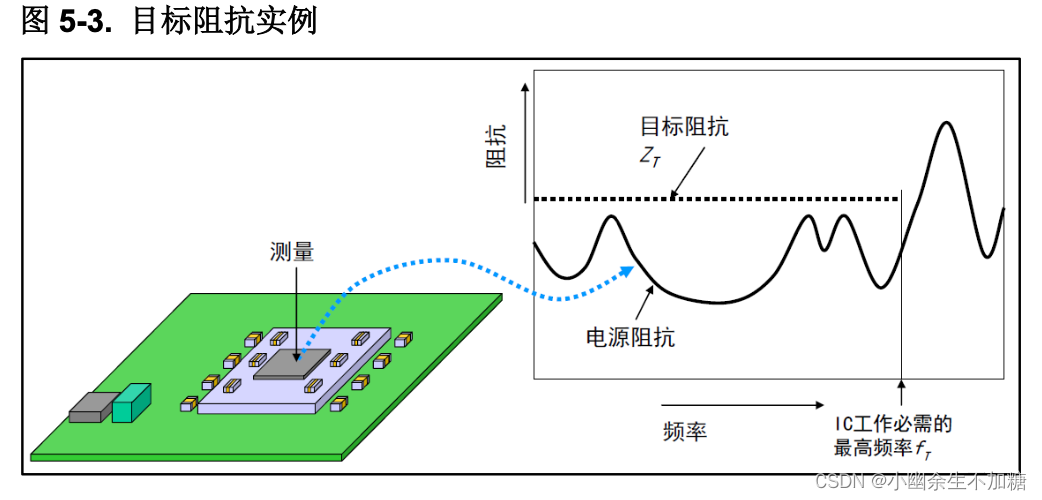

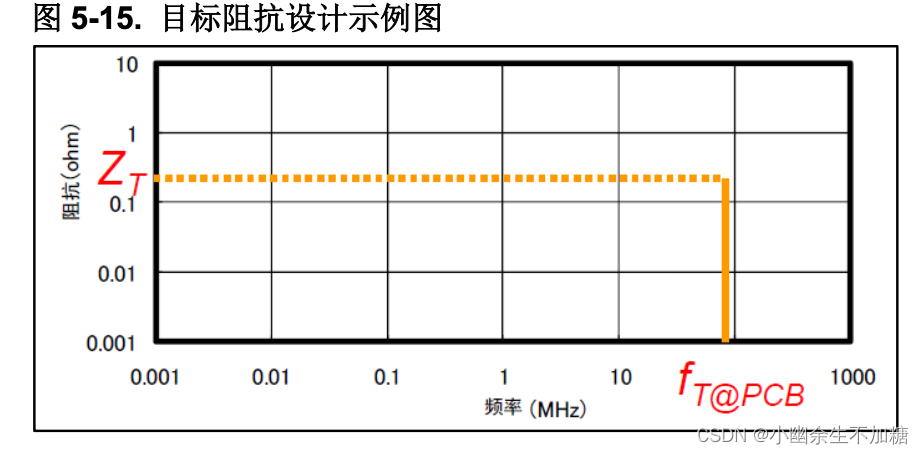

MCU 工作所必需的电源阻抗目标值称之为目标阻抗 ZT,对于必需的频率范围,如图 目标阻抗实例所示,保持低于目标值是有必要的(虽然目标值在图中是个常数,但是根据 频率它可能出现变化)。

PDN 包括电源、去耦电容以及连接它们的接线等。PDN 必需设计成满足目标总阻抗。(虽 然目标阻抗必须根据考虑的 IC 以及线路工作进行选择,但是在某些情况下也可能不太明 确。)

理想条件下,电源阻抗应表现在有关图模型硅晶片晶体管的阻抗方面。然而,对晶片进行 测量不切实际。事实上,电源阻抗需要通过建立一个测量点进行表达,例如,封装的 BGA 终端或 PCB 上的电源板(一般来说,测量值会根据测量位置产生变化)。根据下面的描 述,除非另有说明,这是有关半导体元件的阻抗(一个虚拟值,因为现实中不可测)。

2. 电容分层定位

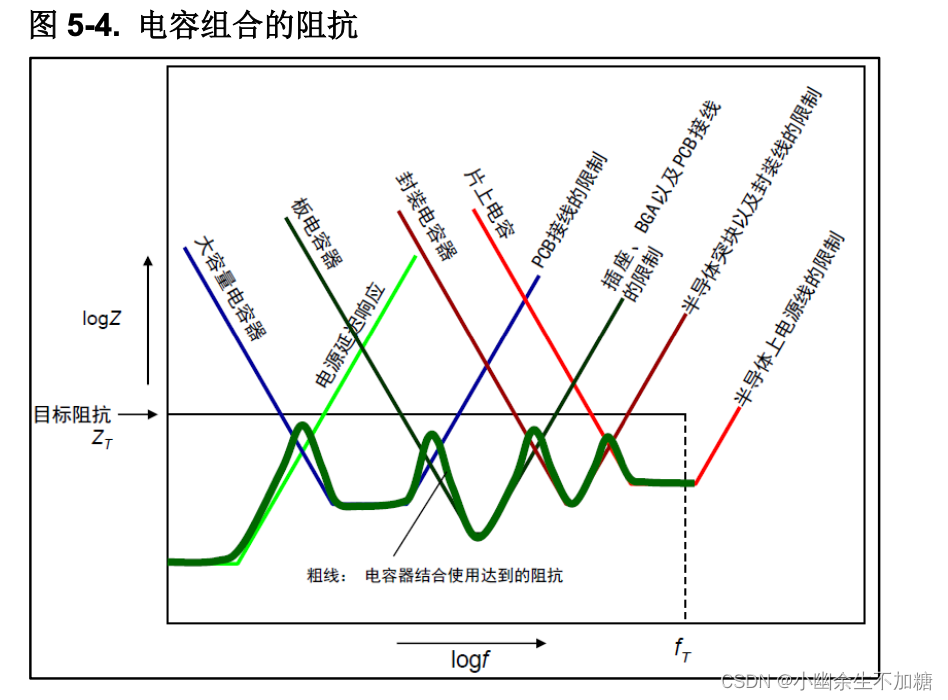

当分层定位电容器时,如图电容分层电流供应模式所示,整个 PDN 阻抗的频率特 性将变成图 电容组合的阻抗的所示。通过结合每个电容器所覆盖的频率区域以满足 总的目标阻抗。

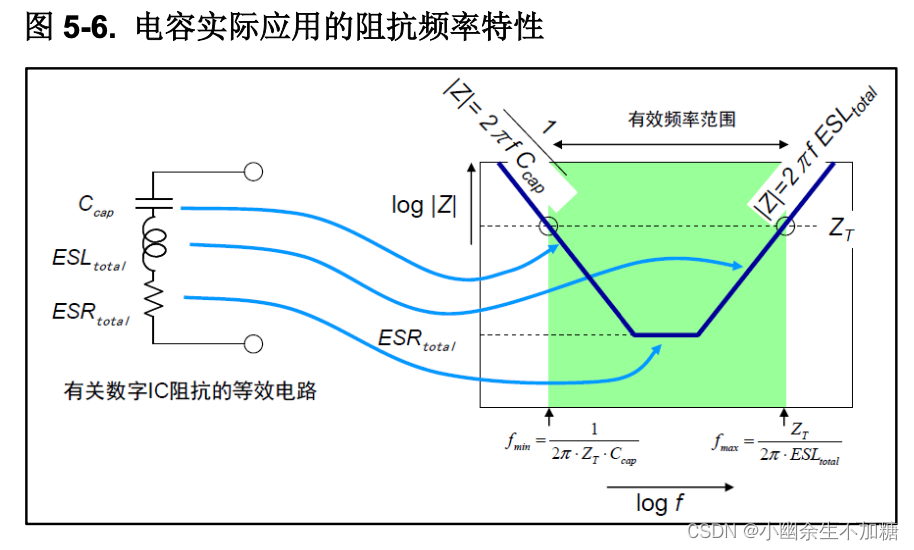

图电容组合的阻抗所示的每个电容器阻抗不是只来自元件,而是包括图 电 容实际应用等效电路所示的半导体元件与电容器之间配线产生的影响。在这个有关半 导体元件的电容器上的阻抗频率特性大约呈V形,如图 电容实际应用的阻抗频率 特性所示。

在这种情况下满足目标阻抗 ZT 的此曲线范围被称为电容器的有效频率范围。如图. 电容 实际应用的阻抗频率特性所示,有效频率范围的下限 fmin 受电容器 Ccap 电容的限制,上限 fmax 受电容器 ESLtotal 电感的限制。此 ESLtotal 包括电容器 Ccap 电感以及接线 Lline 电感。另外,反 过来说,此ESLtotal 包括电容器自身的ESL以及电容器安装垫片和过孔的电感。

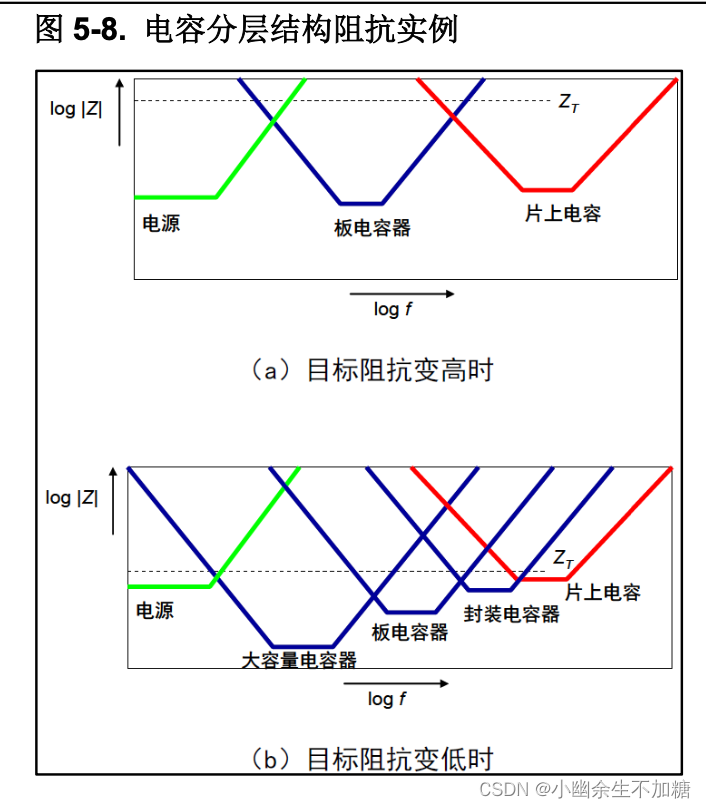

我们可以从图中看出,ZT 大时,电容器的有效频率范围就变宽;ZT 小时就变窄。

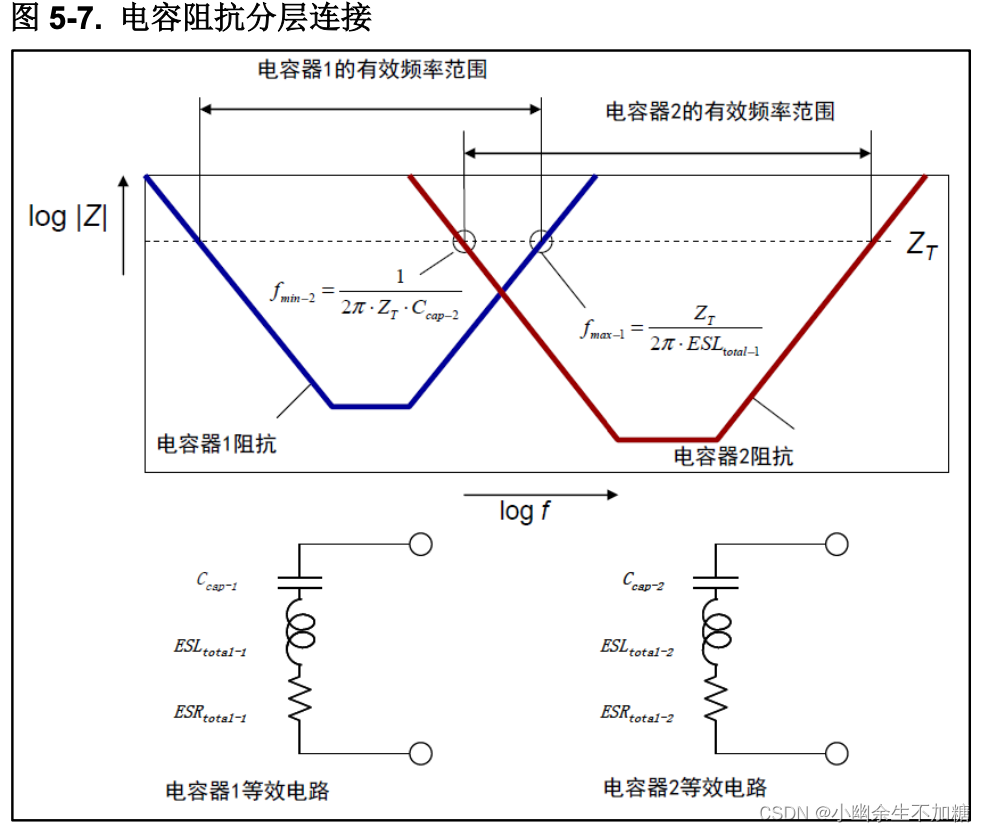

电容器阻抗下限受 ESRtotal 的限制。我们需要使用的电容器为:其 ESR 小于带有小 ZT 电源的 ZT。在电容器分层的连接区域,低频端的电容器(电容器1)与高频段的电容器(电 容器 2)必须用这种方式合并,那就是图 电容阻抗分层连接所示的覆盖有效频率范围 (没有任何差距)。因此,低频端电容器的 ESLtotal 变化时,高频端电容器必要的电容也出 现变化。

另外,如图 电容阻抗分层连接所示,阻抗在频率连接区域可能会增加。这是因为在 电容器间可能发生反谐振。因此有效频率范围内的连接必须有足够余地才可以建立。

同时,电容器的有效频率范围会根据前面讲述的目标阻抗等级而产生变化,允许忽略层次。 当 IC 电流波动变小时,有效频率范围以相对较高的阻抗进行扩大。另外,板电容器电容 变大并且带有小 ESL 的电容器正在使用时,有效频率范围扩大,使其有可能消除大容量 电容器或封装电容器的前面和背面并且减少使用的电容器数量。

如图 . 电容分层结构阻抗实例所示的简化分层的例子。

3. PCB上面的目标阻抗

如图5-2. 电容分层电流供应模式所示的电容器分层,片上电容与封装电容器在IC上提供, 这样,它们不能在 PCB 设计阶段受控制。因此,在 PCB 设计阶段,通常片上电容与封装 电容器覆盖的频率下限被认为是上限频率,fT@PCB,并且,被指定为目标阻抗的上限频率 是为电源终端外部的 IC 封装所服务。这个频率普遍认为是 10MHz 至 100MHz。

当设计 PCB 上的去耦电容器时,我们的目标是满足目标阻抗,直到这个 fT@PCB(没必要 以 IC 工作的最高频率为目标)。此阻抗测量点是 IC 封装的电源终端。

4. 大容量电容

大电容电容器就是在低频区域覆盖阻抗的大型电容的电容器。它被定位在电源区域的一个

地方,并且在某些情况下,还要作为电源模块平滑电容器的替代品。如图 电容实际应用的阻抗频率特性所示,电容器阻抗下限受 ESR 的限制,有效频率 范围上限受 ESL 与接线电感的限制。因此,使用带有小 ESR 和 ESL 的电容器时,处理较 高频率的板电容器电容可以减少,这样电容器布局可能变得更加灵活。

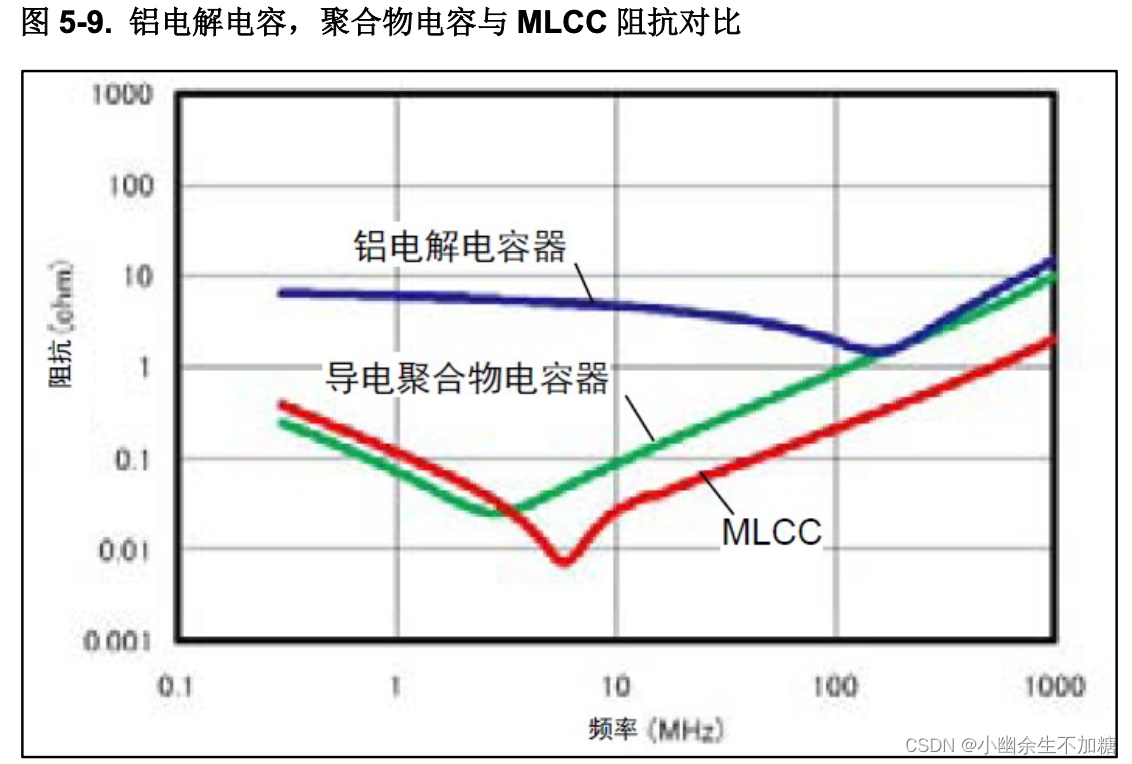

如图 铝电解电容,聚合物电容与 MLCC 阻抗对比所示的是对比电解电容器与 MLCC 的阻抗例子。在这种情况下两个电容器都是2.2μF。即使带有使用导电高分子的低ESR电 容器,在超过 10MHz 的频率范围内,与 MLCC 相比,其阻抗是较大的。这表明 MLCC 的 ESL 很小并且其有效频率范围上限很高。

5. PCB电容定位

在大容量电容器不起作用的更高频率区域的阻抗是由位于 MCU 旁的 PCB 上的板电容器 进行处理。通常 MLCC 用于这个电容器。对于一个相对小型且低速的 IC,一个电容器足 矣;但对于具有低目标阻抗的高性能 MCU,可能就需要使用图. PCB 电容平行布局 实例所示的多个并联电容器。

图 . PCB 电容平行布局实例(a)显示的是不同电容的电容器组合。通过组合不同自 谐振频率的电容器,利用电容器在自谐振频率旁变为低阻抗的特点优势,以宽频率范围内 的低阻抗作为目标。

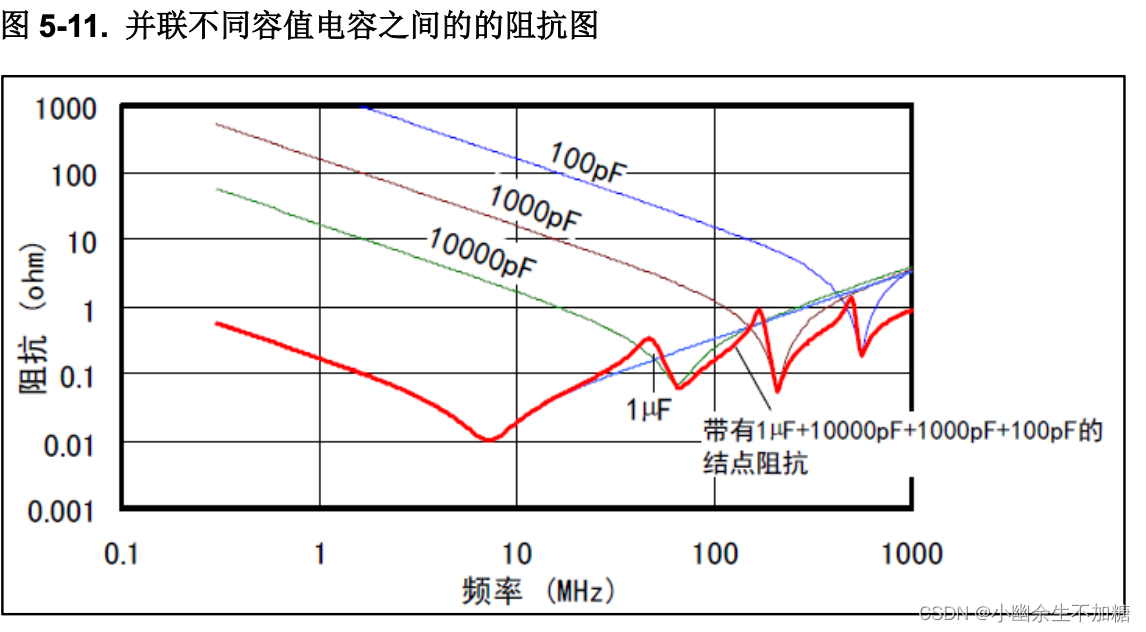

在阻抗不会变得更小的情况下必须谨慎行事,因为反谐振会发生在电容器自谐振频率间的差距上,已讲述。如图 5-11. 并联不同容值电容之间的的阻抗图所示的并联使用 1μF、 10000pF、1000pF 与 100pF 的四个电容器时结点阻抗的例子。阻抗频率特性出现波纹, 并且在有些情况下它们的阻抗在反谐振频率上会超过 1μF 的电容器。

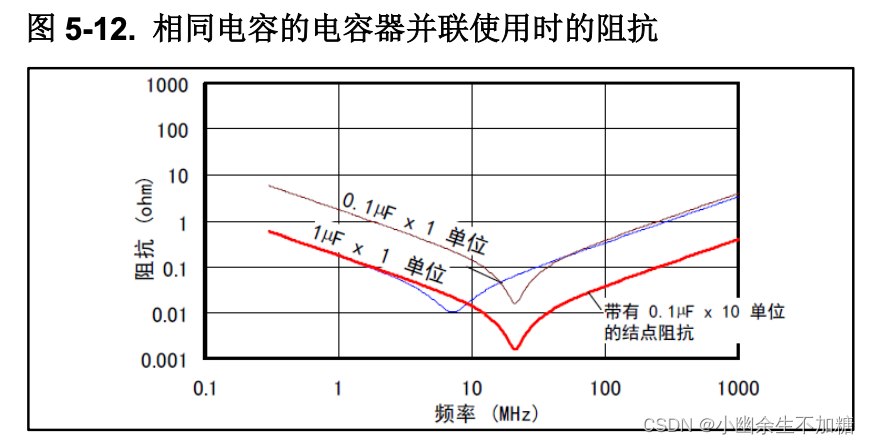

图 PCB 电容平行布局实例(b)显示的是相同电容的电容器并联情形。在这种情况 下,根据图 5-12. 相同电容的电容器并联使用时的阻抗指出的计算结果,反谐振问题不会 如此频繁地发生(假定可以忽略电容器间的接线)。该方法有电容器阻抗并联的效果,除了 垫片阻抗以及并联过孔(在其中一个过孔用于各个电容器的情况下)。也有它的优点就是 增加电容相对比较容易,因为电容器增加的数量。

另一方面,越来越多的电容器有增加空间与成本的缺点。另外,随着面积增大,电容器的 安装位置相对较远,这使接线阻抗的电容器不是那么有效,逐渐降低电容器增加数量的效 果。

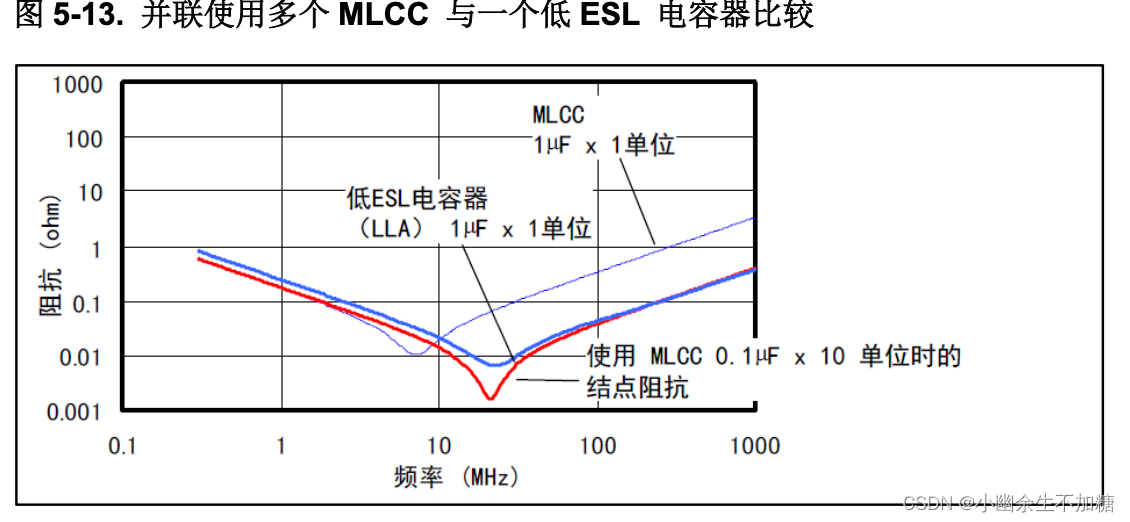

如果图 5-10. PCB 电容平行布局实例所示的方法出现问题,使用低 ESL 电容器将产生与 多个电容器同样的效果。这更有利于节省空间与成本。图 5-13. 并联使用多个 MLCC 与 一个低 ESL 电容器比较显示的是多个 MLCC 与一个低 ESL 电容器的比较。一个低 ESL 电容器可以实现相当于使用 10 个并联 MLCC 产生的阻抗。

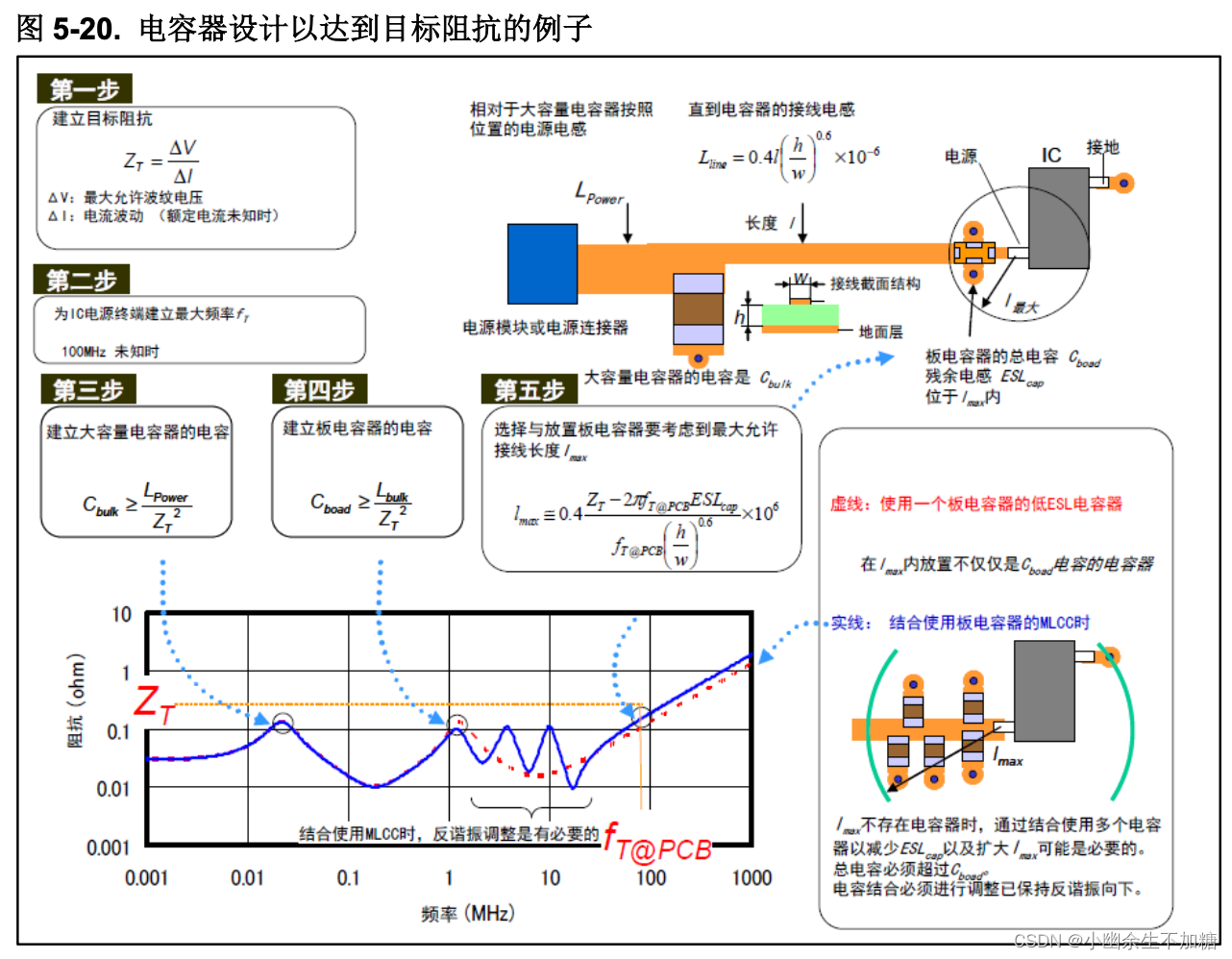

6. 电容设计步骤

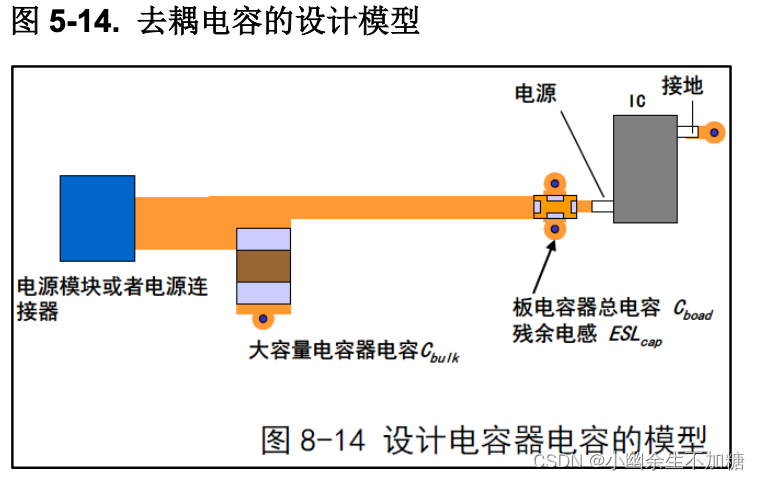

从目标阻抗中建立大容量电容器与板电容器的例子如图 5-14. 去耦电容的设计模型所示, 我们考虑到大容量电容器与板电容器定位于电源模块与 IC 之间什么位置的情形。用 MSL 形成接线并且可以大约预先确定电容器的安装位置。

6.1 设置目标阻抗

首先:目标阻抗 ZT 由图 5-15. 目标阻抗设计示例图所示的所决定。如果已经知道目标值 与 IC 工作所必需的电源阻抗最大频率,这些值可以使用。如果未知,他们用下面的公式 建立:ZT = ΔV /ΔI。

在这种情况下,ΔV 代表最大允许波纹电压,ΔI 代表最大静态波动瞬间电流(如果未知, 我们要让其变成 IC 最大电流值的大约一半)。ZT 最大频率 fT@PCB 根据 IC 运行速度而 变化。如果未知,将其设置为大约 100MHz。

6.2 大容量电容设计

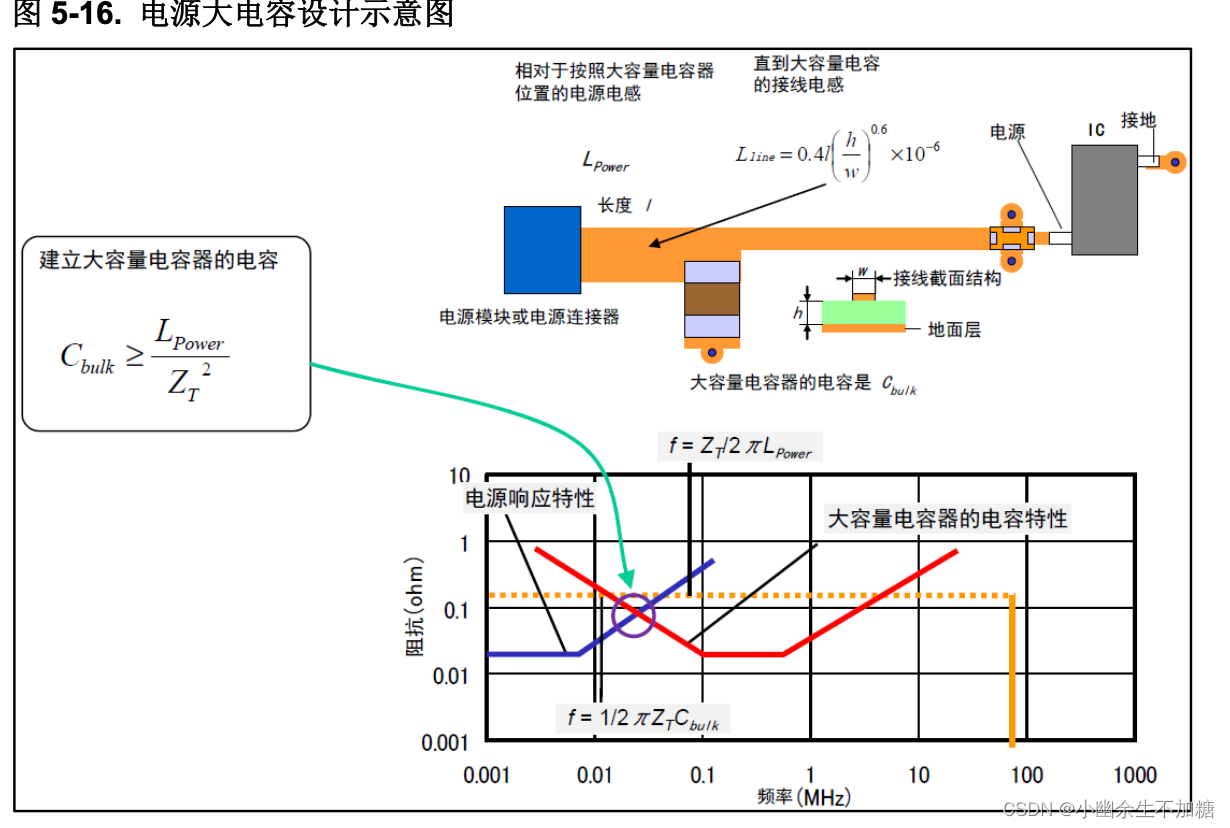

下一步,我们将建立低频端电容器的电容。第一个电容器将是大容量电容器。其模型如图

5-16. 电源大电容设计示意图所示。当我们可以假定电源模块与电路或印制电路间的电缆阻抗是阻止我们在大容量电容器位 置达到目标阻抗的主要因素时,当电源模块理想工作时,我们将让这个电感变成 LPower 并 且建立大容量电容器电容 Cbulk。

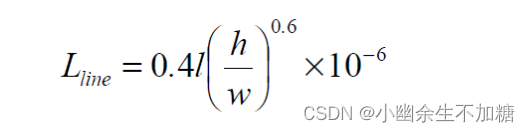

当电路仅包括印刷电路,我们可以使用下面公式,从下面公式以估计 LPower。

在这个公式里,h 是 MSL 中的绝缘材料厚度,w 是接线宽度,l 是接线长度。 在电源模块自身的响应特性不可以忽略的情况下,此电感 LPowerResponce 必须要算入公式中的

LPower 按照以下电感时间常数,可以建立粗略的估计。

在这个公式里,tPowerResponce 是电源模块的响应速度。

6.3 PCB 电容设计计算

下一步,我们将建立板电容器电容,Cboad,如图 5-17. PCB 电容设计示意图所示。如果我 们让大容量电容器与板电容器间的接线电感作为 Lbulk,板电容器安装区域的必需电容器与 公式一样。

严格来说,尽管这个 Lbulk 包括大容量电容器的 ESL 以及 IC 与大容量电容器间的所有

接线电感,图中,仅大容量电容器与板电容器间的接线可代表整体的电感。

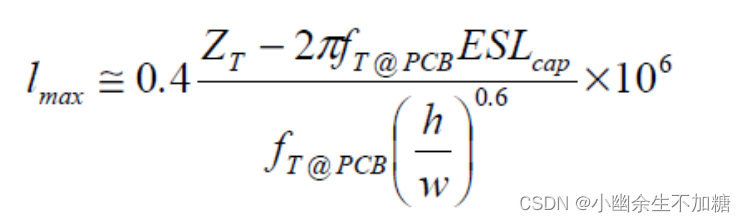

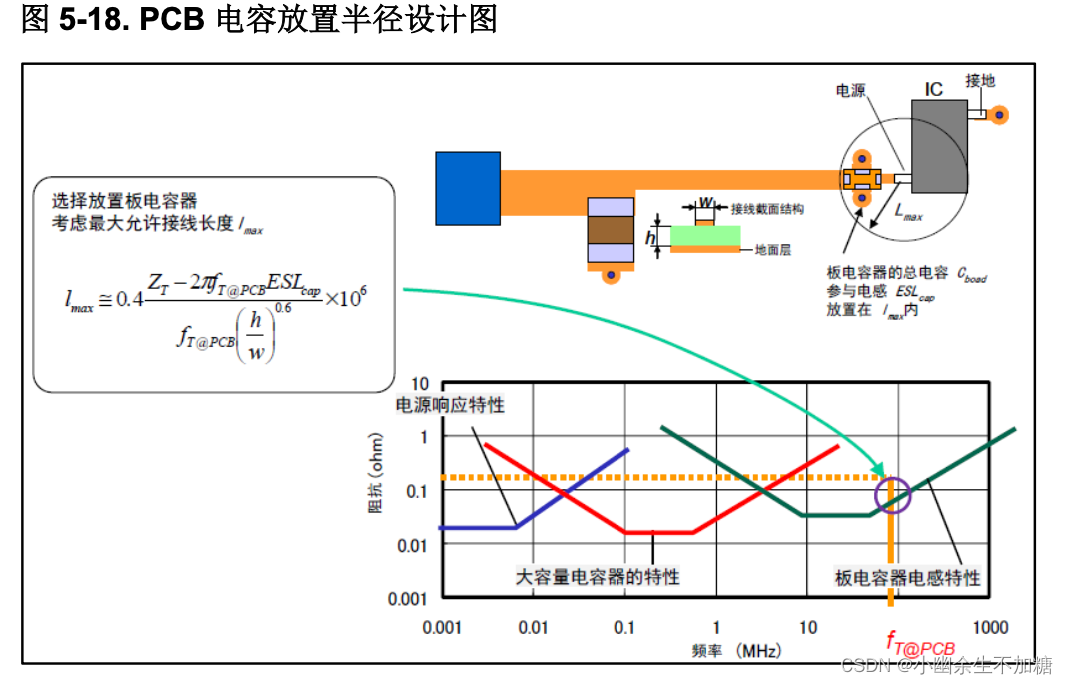

6.4 PCB 电容放置半径

下一步,要定位板电容器。通过定位板电容器以便于 IC 与电源终端间的间距在最大 允许接线长路 lmax 之内,可以在相当于 fT@PCB 频率时满足 ZT,如图 5-18. PCB 电 容放置半径设计图所示。

在这个公式中,ESLcap 代表板电容器的 ESL,并且它包括来自电容器安装垫片与过孔的 电感(ESLPCB),排除电容器自身的 ESL。

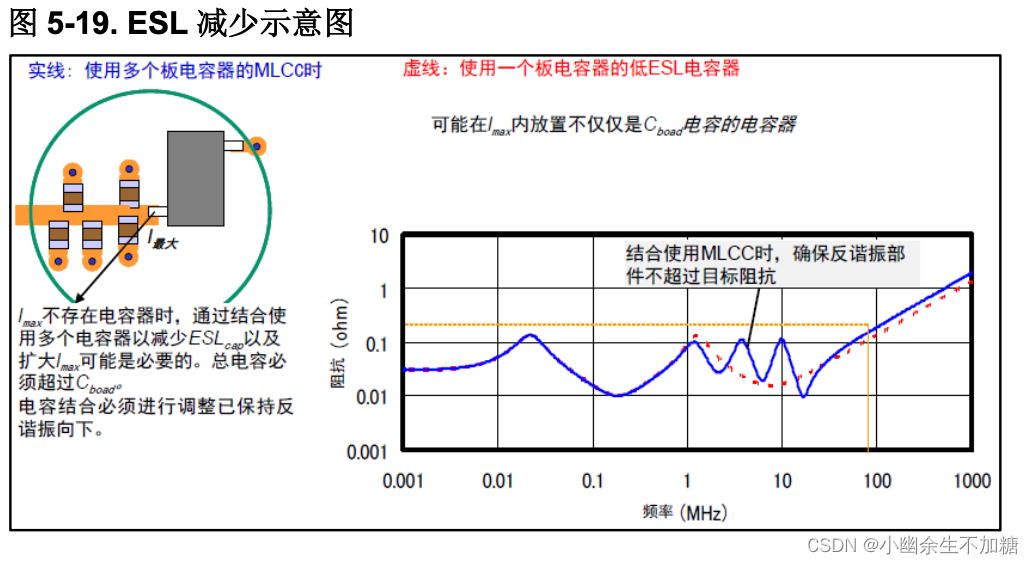

6.5 降低去耦电路的 ESL

根据目标阻抗,一个电容器不能达到 lmax 适当长度,也就不能达到目标阻抗。在这种情况 下,我们需要用并联方式定位多个电容器,如图 5-19. ESL 减少示意图中的左所示,以减 少等效 ESLcap,以及扩大 lmax。第章所述的低 ESL 电容器的使用也同样有效。

应用实例

7. 总结

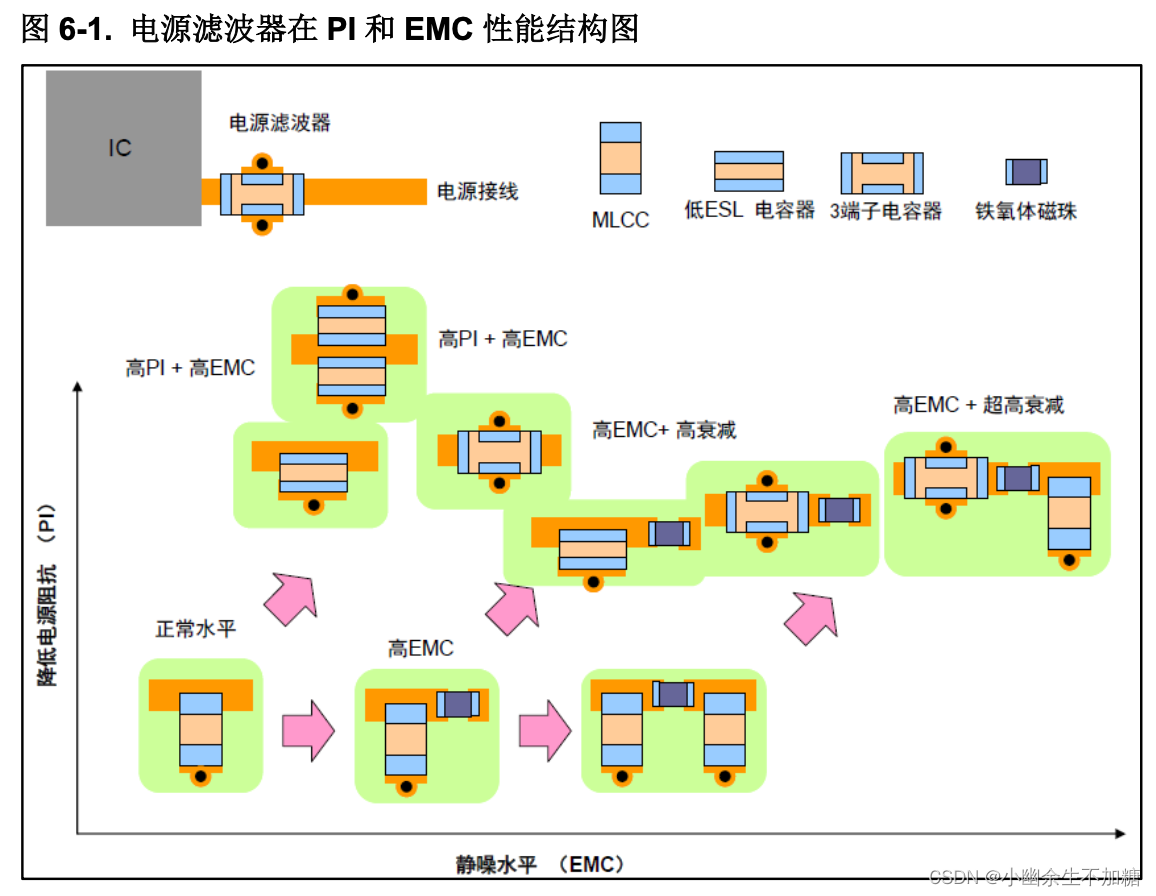

MCU 电源的去耦电路适用于抑制噪声以及为 MCU 提供足够的电流以达到电源完整性 PI,基于噪声抑制观点的插入损耗以及电源完整性观点的阻抗。

图 5-20. 电容器设计以达到目标阻抗的例子显示出从噪声抑制与电源完整性的观点上作出 比较的各种去耦电路。对于 MCU 电源,MLCC 被用作为实现这些功能的简单方式。用三端子电容 器或低 ESL 电容器替换时,可以预测到噪声抑制与电源完整性的性能改进。此外,增加电感 器例如铁氧体磁珠时,从噪声抑制观点上可以改进性能;但是,在某些情况下可能出现电源 阻抗增加。在这种情况下,必须补充电容。电容器与电感组合阶段增加数量可以进一步削弱 噪声。这些滤波器应适用于与之相对应的电路所要求的等级。

从噪声对策观点上看,电源电路特性包括与信号电路相比很复杂的接线配置,使其设计特 性阻抗很困难;特别是某些情况下的低阻抗;噪声对策应用的广泛频率范围从语音到 GHz; 并且由于许多电路的共享,具有广泛的影响范围。为了使旁路电容器在这些电路中有效发 挥作用,安装结构以及产生小电感的接线设计对于高频下的低阻抗很有必要。为此,本手 册尽可能地描述安装电容器的接线配置。

-

相关阅读:

彻底玩转Java注解和反射

[力扣 Hot100]Day38 翻转二叉树

基于OpenCV与Keras的停车场车位自动识别系统

shell脚本的运行机制

rust学习

传奇服务器配置如何搭建

dockerfile,shell脚本,yaml文件如何配合

RabbitMQ 消息的可靠性

centos7 探测某个tcp端口是否在监听

LeetCode(32)串联所有单词的子串【滑动窗口】【困难】(含图解)

- 原文地址:https://blog.csdn.net/qq_41600018/article/details/132921378