-

数字集成电路设计(六、Verilog HDL高级程序设计举例)

1. 数字电路系统设计的层次化描述方式

- 在我们的数电,集成电路设计里面,一定是层次化设计的

- 在一个手机芯片的一个部分,写的硬件描述语言的层次都能达到20几层,对于这样的设计,我i们就能想到采用底层的设计,中间层的设计和顶层的设计。对于小规模电路,极小规模电路,通常想的是先有模块然后去搭一个电路,这样的就叫Bottom-Up的设计

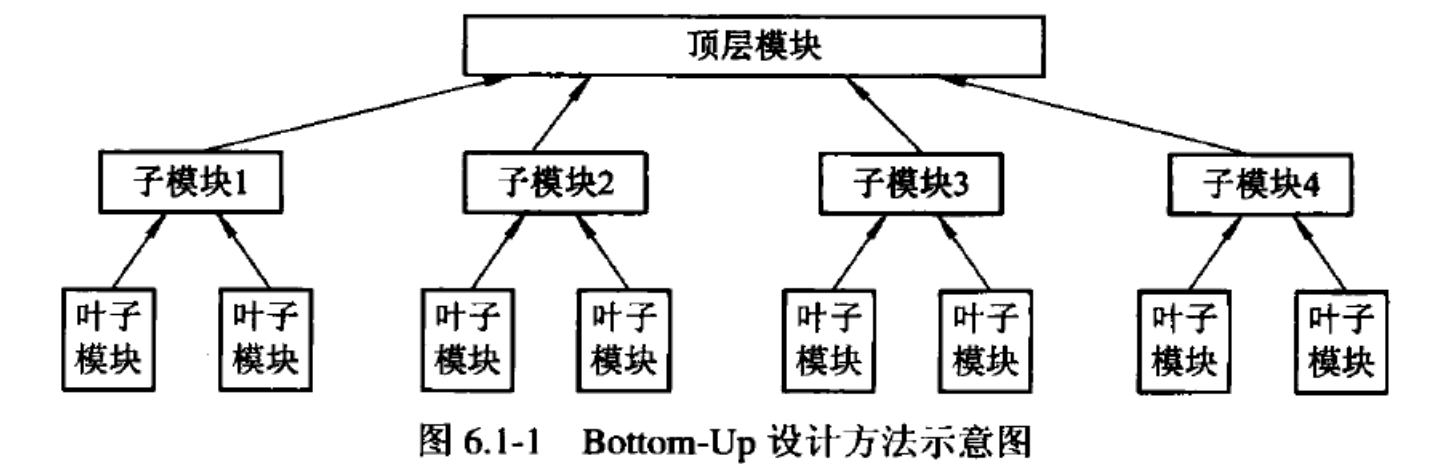

1.1 Bottom-Up 设计方法

- Bottom-Up 设计方法是一种传统的设计方法,它要求电路设计者将系统进行模块划分,从底层模块设计开始,运用各底层模块搭建一个完整的系统。在这种设计方法中,首先根据系统设计的要求,定义并建立所需要的叶子模块,通过模块连接方式建成较大的模块,然后把这些比较大的模块组合成具有一定功能的模块,最后将这些功能模块组合,直到完成整个系统

- !!这种设计方式存在一些问题:规模做不大。当你做完最简单的模块往上堆,当堆得越来越高的时候你会发现这个时序差一点,那个差一点。这时候要怎么改呢?要从地下往上改,这个工作量非常大, 所 以 这 是 不 推 荐 的 一 种 设 计 方 式 所以这是不推荐的一种设计方式 所以这是不推荐的一种设计方式

- 举例:串行加法器

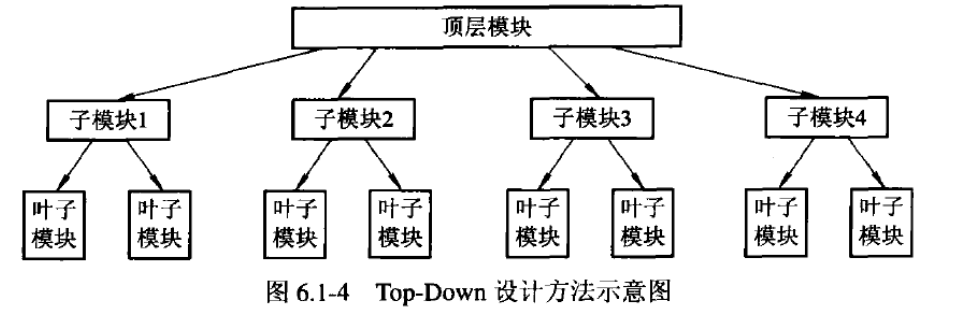

1.2 Top-Down 设计方法

- !!现在的大规模,超大规模集成电路设计,一定是从顶层开始设计的,包括功能,面积,时序,功耗等

- 对于下面,会写出空的模块给下面,会告诉每一个模块自己的约束,然后再往下分,一直分到Engineer。

- 能做到最上面得都是行业顶尖

- !!!!从代码的角度,真正难得是在下面,说的行为级描述啥都是在底层的模块,越往上面越是结构性的描述,都是模块搭,但是这个模块搭建就要求非常严格。所以在我们的设计中一定要做好这方面的准备工作,然后才会有时序,总线一大堆的概念,所以是一个不断学习的过程

- 举例:

2. 典型电路设计

2.1 加法器树乘法器

- 加法器树乘法器的设计思想是“移位后加”,并且加法运算采用加法器树的形式。乘法运算的过程是,被乘数与乘数的每一位相乘并且乘以相应的权值,最后将所得的结果相加,便得到了最终的乘法结果。也就是第一位不用移,第二位乘2相当于左移一位,以此类推。

- Verilog代码实现上图的4位加法器树乘法器:

- 这个电路的速度会非常慢,他的速度决定于加法,这个电路就是二选一的数据选择器拼接在一起,主要的延迟就是来自于加法的延迟

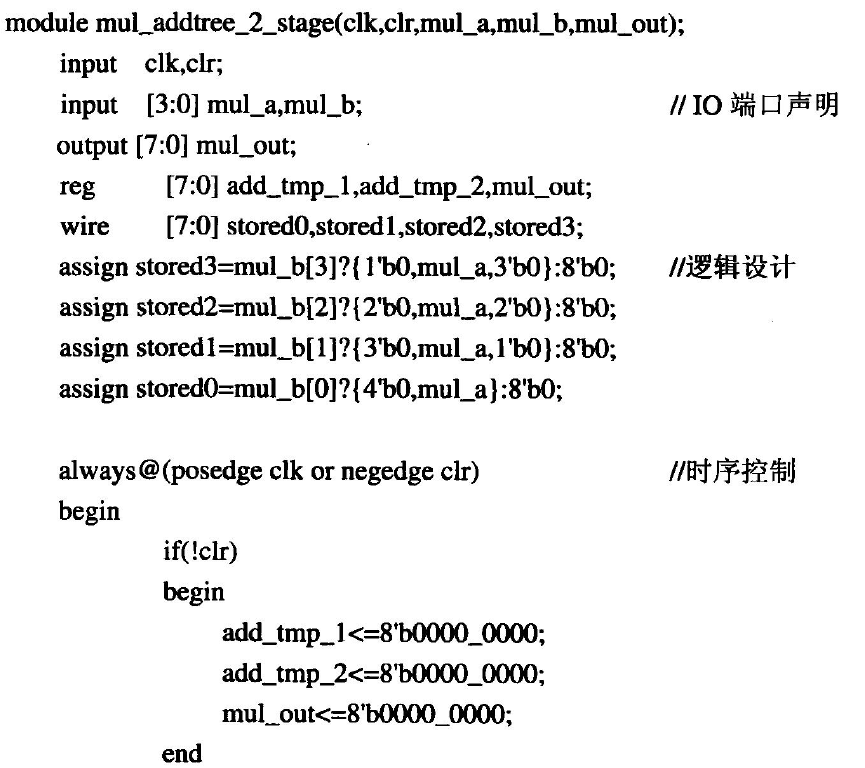

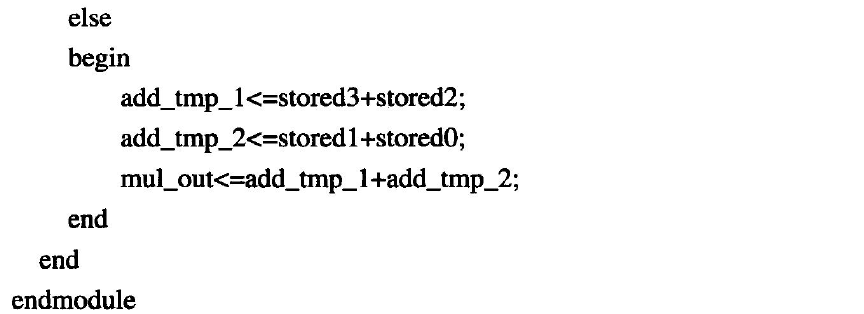

2.1.1 改进为两级流水线4位加法器树乘法器

- 为了提高乘法器的速度,可以穿插流水线的方式,这样就可以把两步的加法变成一步的加法的速度(其实改变的是吞吐率,关于流水线可以看我的数电博客 https://blog.csdn.net/y_u_yu_yu_/article/details/127641915)

- !!在计算机中,我们现在的普通高精度乘法是64位乘64位,可想而知,我们在它的运算指令单元中加多少级流水线才能达到3.几个G的运算速度。cpu的运算结构,虽然占很大面积,但是并不是很麻烦的一件事情,所有的计算单元基本都是以这种方法来提高它的计算速度

- 通过在第一级与第二级、第二级与第三级加法器之间插入 D触发器组,可以实现两级流水线设计,其VerilogHDL代码如下:

- !!在时钟上升沿用了一个非阻塞型赋值,就可以得到流水线的操作(当我们讲阻塞赋值和非阻塞赋值在时序电路中就是流水线的事情)

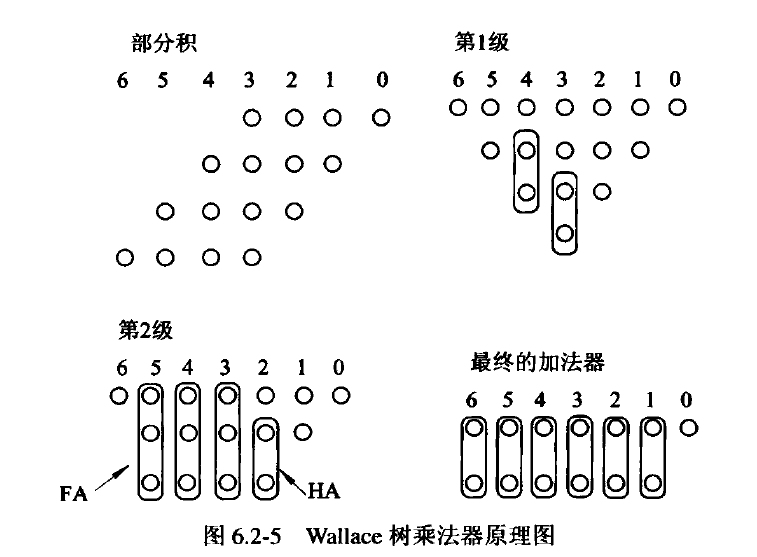

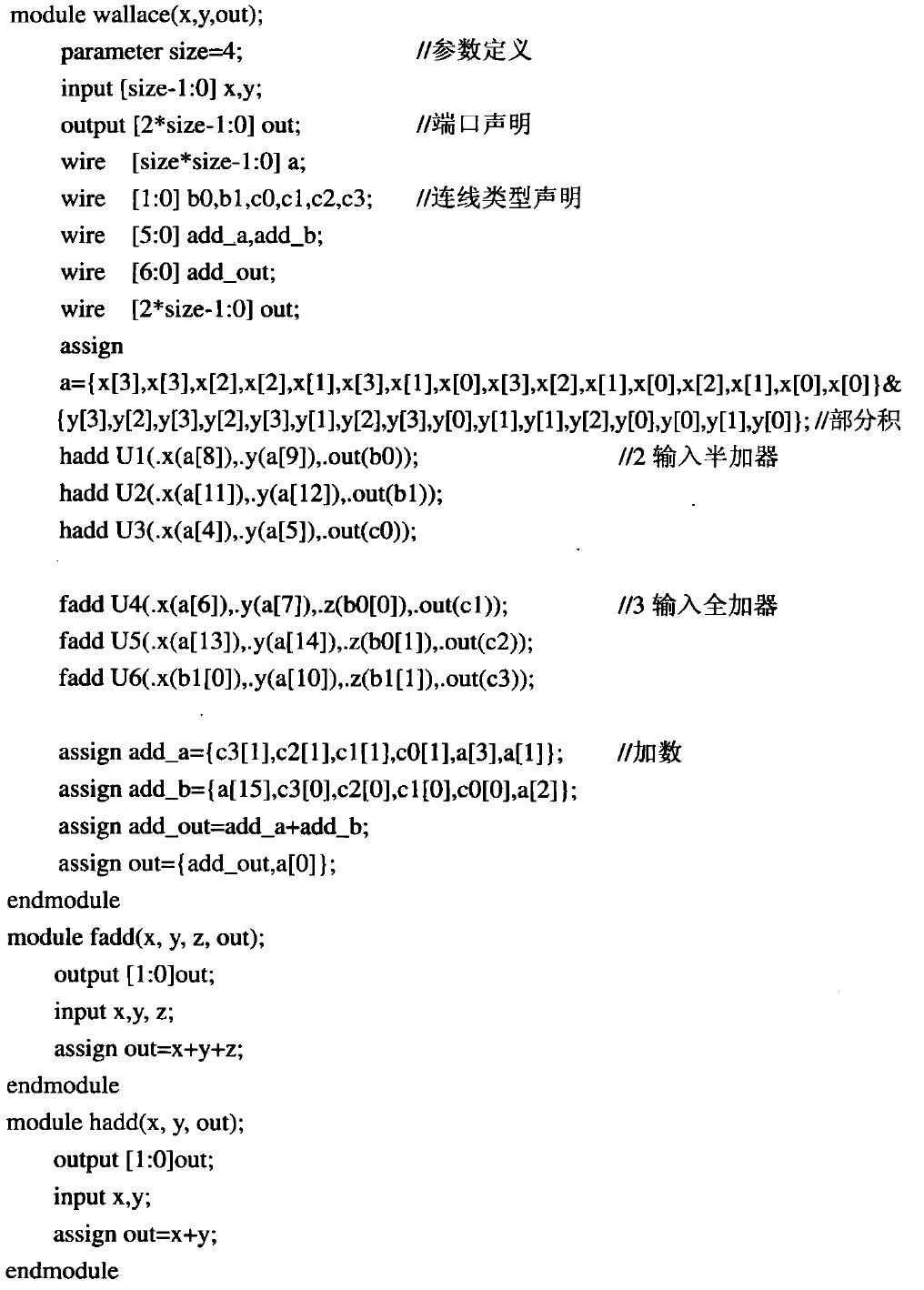

2.2 Wallace 树乘法器

- !!在电路设计中,最可怕的不是之前的单元,而是加法。在4位乘法,我们对于一个传统的加乘的观念,要进行六级以上,使得延迟会变得非常大。Wallace通过3级就能实现4x4这样结构的乘法

- 其基本原理是加法从数据最密集的地方开始,不断地反复使用全加器、半加器来覆盖“树”。这一级全加器是一个3输入2输出的器件,因此全加器又称为3-2压缩器。通过全加器将树的深度不断缩减,最终缩减为一个深度为 2 的树。最后一级则采用一个简单的 2 输入加法器组成。

- 形成的电路结构如下图,运用了全加器和半加器(FA 为全加器,HA 为半加器)

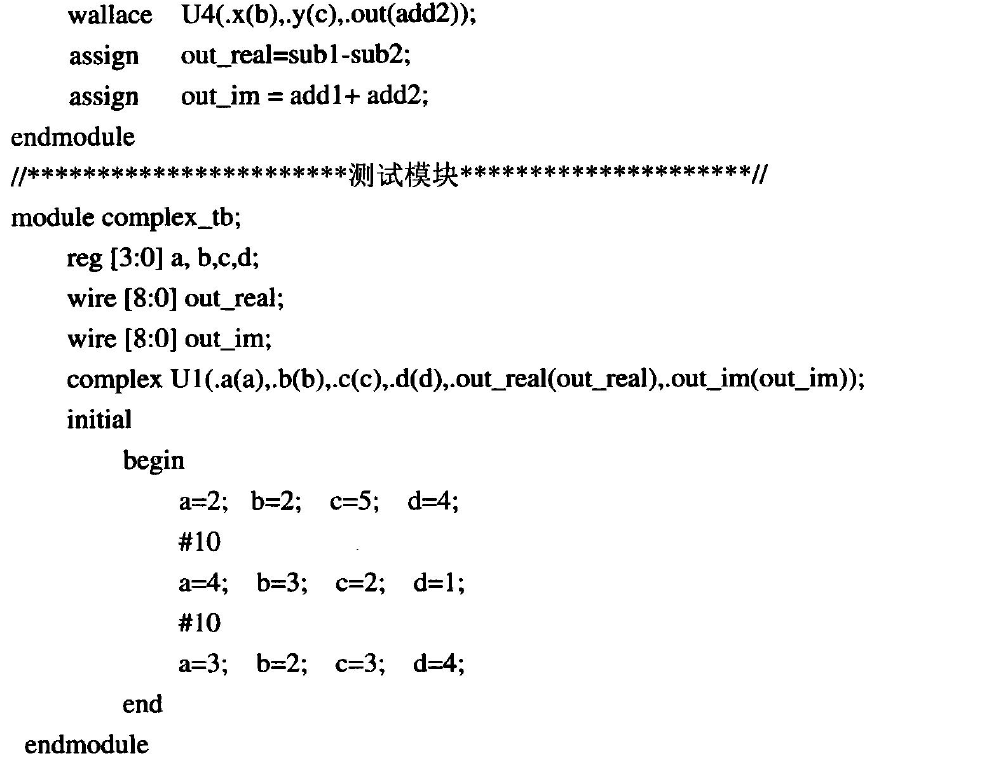

- Verilog代码:

- 测试代码:

- 测试结果:

- !!一开始设计可能是有了基本的知识就可以,但是越到后面越考验数学的能力,数学建模和建模后化简成电路的能力

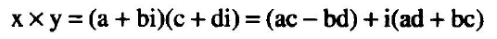

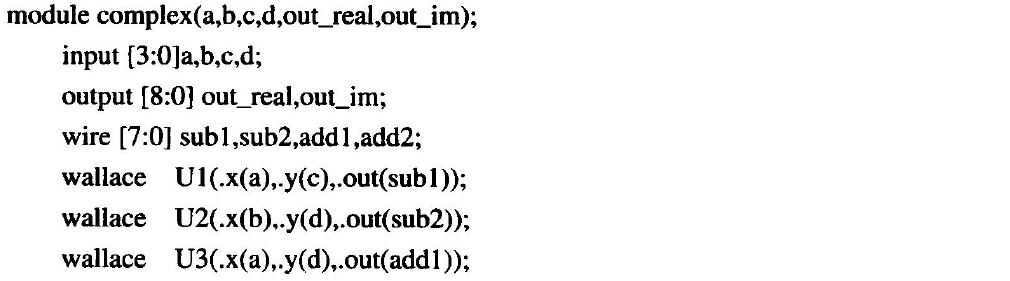

2.3 复数乘法器

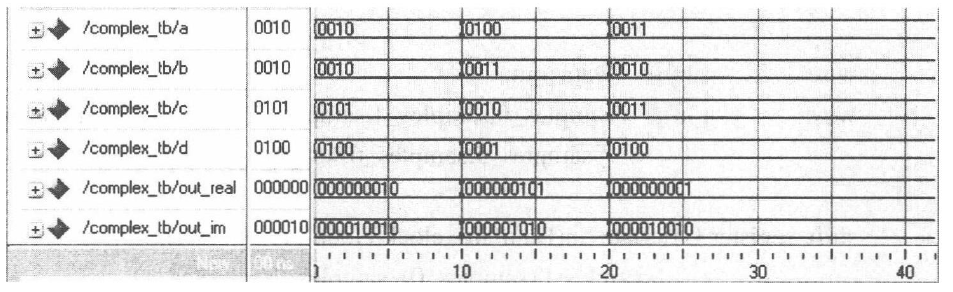

- 复数乘法的算法是:设复数 x=a +bi , yc +di ,则复数乘法结果为

- 用了四个乘法和两个加法

- !!!!根据具体的电路要求,我们可以进行优化:如果是高速电路,我们需要在所有的乘法器和加法器打上流水线才算做完;对于低速电路,整个芯片工作能力比如是500Mhz,但是我需要50Mhz,这时候简化成一个乘法器一个加法器就够了,在想让面积减小的时候也可以这么做

- Verilog实现:

- 测试结果

2.4 FIR滤波器的设计

- 滤波器就是对特定的频率或者特定频率以外的频率进行消除的电路,被广泛用于通信系统和信号处理系统中。从功能角度而言,数字滤波器对输入离散信号的数字代码进行运算处理,以达到滤除频带外信号的目的。

- !!这个电路非常重要,所有的信号处理,所以的移动终端上,都有大量的FIR。这个东西的特点是面积特别大,电路特别简单

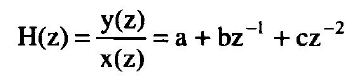

- 有限冲激响应(FIR)滤波器就是一种常用的数字滤波器,采用对已输入样值的加权和来形成它的输出。其系统函数为

- 其中z-1表示延迟一个时钟周期,z-2表示延迟两个时钟周期

- 对于输入序列X[n]的FIR 滤波器,可用图6.2-10 所示的结构示意图来表示,其中X[n]是输入数据流。各级的输入连接和输出连接被称为抽头,系数(b0,b1,……,bn)被称为抽头系数。一个M 阶的FIR 滤波器将会有 M+1个抽头。通过移位寄存器用每个时钟边沿 n(时间下标)处的数据流采样值乘以抽头系数,并将它们加起来形成输出 Y[n]。

- !!在Altera,Xilinx等的所有工具中间都有滤波器工具,可以通过给定的长度和要求,可以自动生成滤波器的系数。在设计滤波器的时候,首先应该大概画一个曲线的样子,然后用这些工具生成系数,然后在仿真看系统有没有影响,然后定点化,然后再看有没有影响,然后放到电路设计里面

- !!!!IIR滤波器在信号中会产生振荡,产生自激的现象。FIR在信号中只有零点没有极点,而IIR滤波器由于反馈会有极点产生,极点对于电路代表的是不稳定,IIR滤波器很吸引人,因为几阶就能达到FIR几十阶的效果,但是我们牺牲了反馈型滤波器而用横向滤波器

- MATLAB也嵌入了设计工具,给抽头长度,给要求,就会生成浮点的和定点的抽头系数,还可以直接生成Verilog代码

- !!在这个电路中,对电路产生延迟最大的是加法器,乘法器只是两个数相乘然后输出就行了,不会引起太多延迟。当抽头变多的时候,我们会增加加法器的数量

2.5 存储器的设计

- 存储器发生了巨大的变革,全世界最好的工艺都在做存储器,得存储器,得数字电路天下,存储器做的越好,数字集成电路越好。从工艺角度上,存储器单元都是一样的,这时候对高精度的线是非常有利的,检查良品率,只要一致性好,没有问题;打开cpu来看,存储器的面积占了一大半

2.6 FIFO的设计

- 实操可以看我FPGA的博客 https://blog.csdn.net/y_u_yu_yu_/article/details/127157227

-

相关阅读:

如何发现新的潜力项目?工具推荐

重新认识下JVM级别的本地缓存框架Guava Cache——优秀从何而来

IP地址 0.0.0.0 和 127.0.0.1之间的区别

python note

Eclipse自定义注释

YOLOv6: A Single-Stage Object Detection Framework for IndustrialApplications

ubuntu给终端加代理服务器

详解卡尔曼滤波原理

前端 -- 单选框内容影响复选框的隐藏与显示 附代码

【Java基础】TreeSet集合、自然排序、比较器排序、成绩排序及不重复随机数案例

- 原文地址:https://blog.csdn.net/y_u_yu_yu_/article/details/127990514