-

数字集成电路设计(五、仿真验证与 Testbench 编写)(二)

4. 信号时间赋值语句

- !!信号赋值语句是硬件描述语言非常重要的一条语句,是对于任意信号形式和实际变量的仿真的一种格式

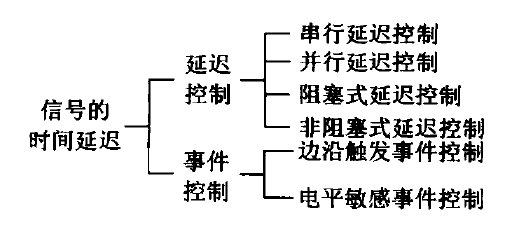

- 延迟信号的产生再硬件描述语言有俩个大的类型:延迟控制(可以分为串行延迟控制、并行延迟控制、阻塞式延迟控制和非阻塞式延迟控制)和事件控制(可以分为边沿触发事件控制和申平敏感事件控制)。

4.1 时间延迟的语法说明

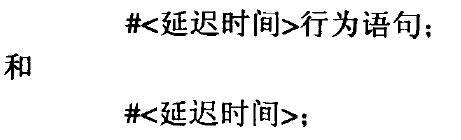

- 延时控制可以写成两种形式

- 第一种假如没有行为语句,加一条库语句也是可以的

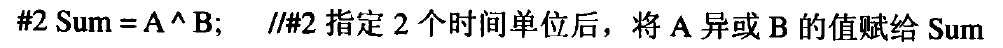

- 其中,符号“#”是延迟控制的关键字符,“延迟时间”可以是直接指定的延迟时间量,或者以参数的形式给出。在仿真过程中,所有延迟时间都根据时间单位定义。例如:

- !!控制方式可以分为很多类,但是只要能理解这种意思,选用其中一种都可以写出测试向量,而测试向量的写法在硬件描述语言中是不做硬性规定的,信号波形产生了就可以

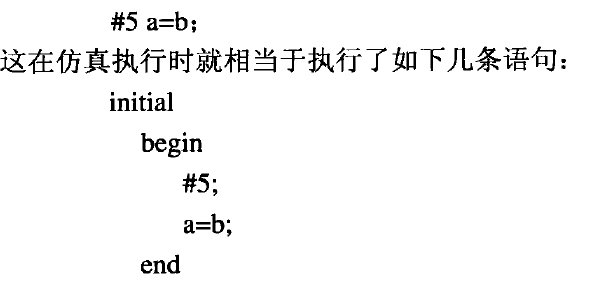

(1)外部延迟控制:时间控制出现在整个过程赋值语句的最左端,也就是出现赋值目标变量的左边的时间控制方式。语法结构和等效如下:

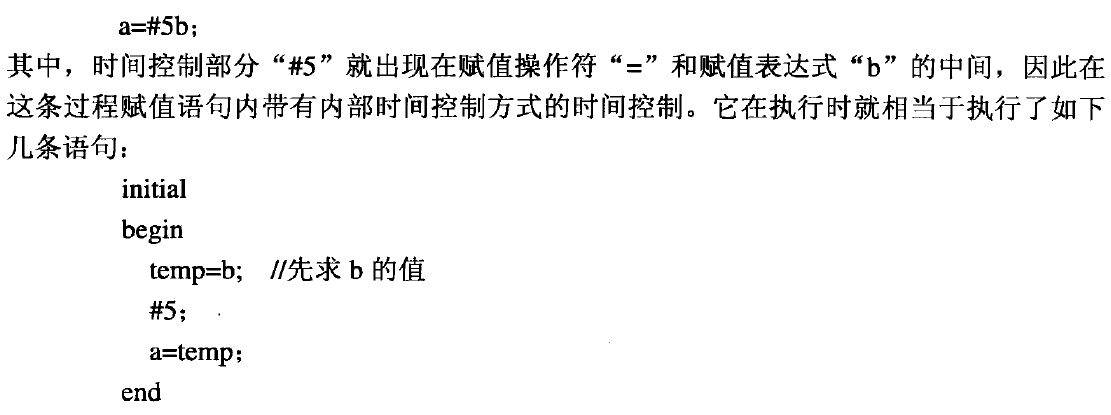

(2)内部延迟控制:过程语中的时间制部还可以出现在“值操作符和“赋值表达式”之间的时间控制方式。语结构和举例:

4.2 时间延迟的描述形式

- 时间延迟的描述形式是指延迟控制的描述形式,分为串行延迟控制、并行延迟控制、阻塞式延迟控制和非阻塞式延迟控制四种形式。

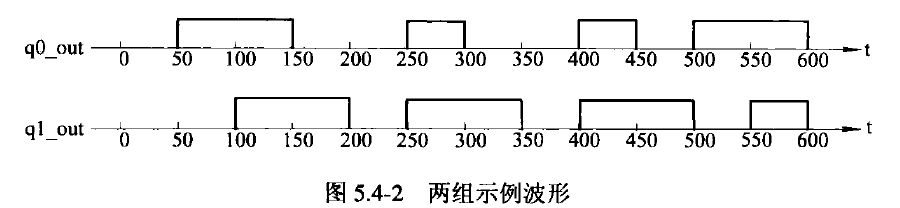

- 下面以实现两组不同波形的信号为例(图5.4-2中的q0_out 和q1_out)来说明四种不同时间延迟的描述形式。

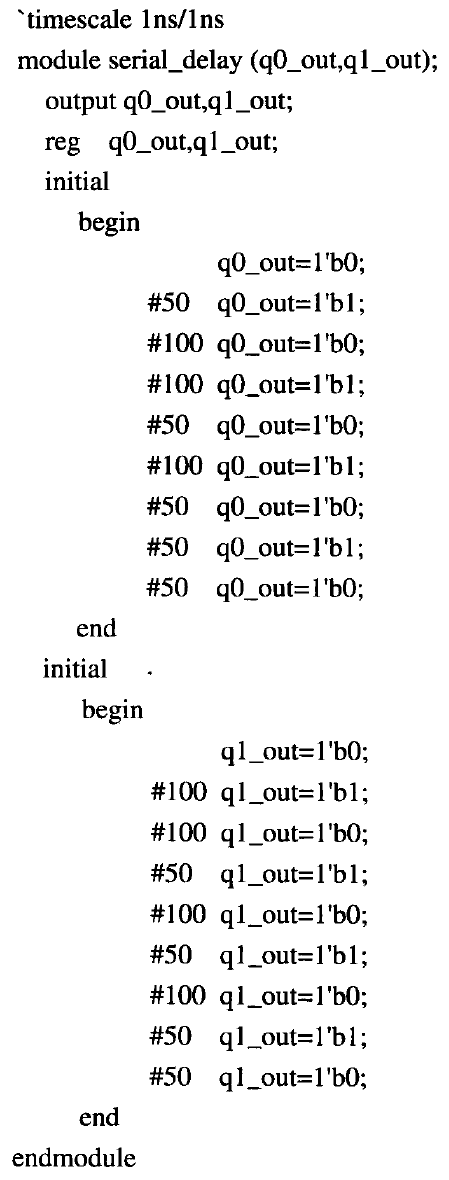

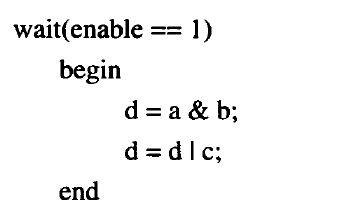

1.串行延迟控制

(1)串行延迟控制是最为常见的信号延迟控制,它是由 begin-end 过程块加上延迟赋值语句构成

(2)对上图进行描述

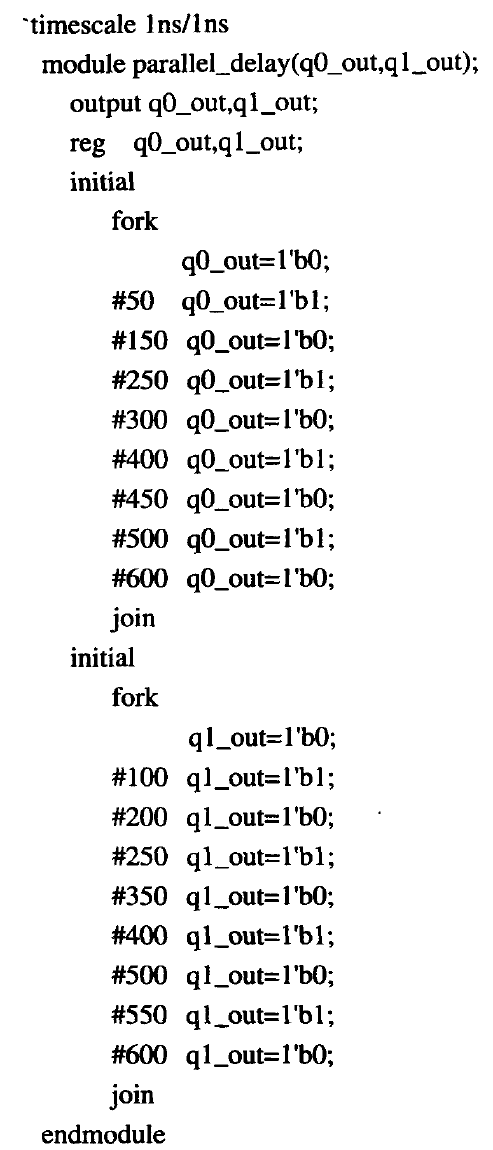

2. 并行延迟控制

(1)并行延迟控制方式是通过 fork-join 过程块加上延迟赋值语句构成的(对于 fork-join ,不管采用阻塞还是非阻塞赋值,所有语句都是并行的)

(2)对上图进行描述

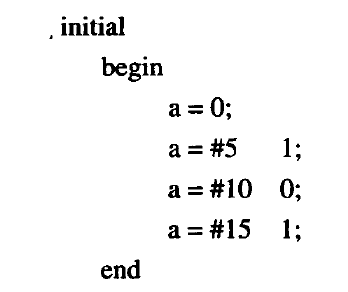

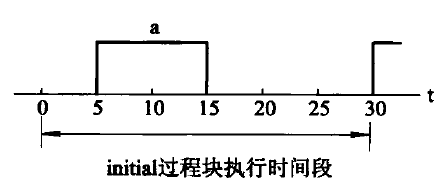

3.阻塞式延迟控制

(1)阻塞式延迟控制是在阻寨式过程赋值基础上带有延迟控制的情况

(2)控制结果

(3)解释:相当于把值给了temp,然后延迟结束temp给a,一开始a=0,然后temp=1,5s后,a=temp=1,temp=0。!!如果用阻塞,延迟就是相对延迟4.非阻塞式延迟控制

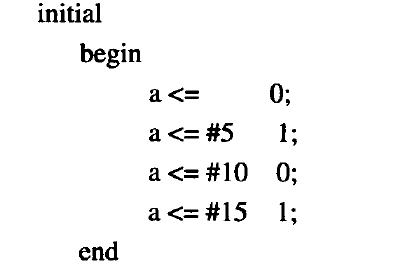

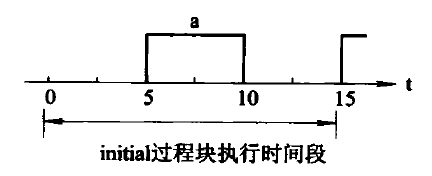

(1)非阻塞式延迟控制是在非阻塞式过程赋值基础上带有延迟控制的情况

(2)控制结果

(3)!!如果用非阻塞,前面的延迟就变成绝对的延迟- !!这四种形式选择哪一种看个人习惯,这时候就在硬件描述语言的测试和仿真中形成了你自己的风格。在这个阶段,你面对的就是计算机的cpu不是硬件电路,所以可以用你想到的各种方式去做,只要产生的激励信号是对的,观察方法是对的就可以。更加注意的是信号产生的形式,只要波形和想的是一样的,用什么方法都可以

4.3 边沿触发事件

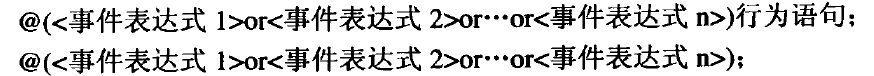

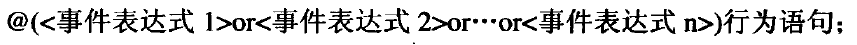

- 边沿触发事件控制的语法格式有以下四种形式:

- !!在硬件描述语言中,可以用or把事件隔开,也可以用“,”,这两个方式是统一的

- !!如果把这个变成一种不确定事件的标志,刚刚的#加一个时间是加一个固定延迟,可以用参数方式去写,但是一旦程序运行,这个延迟就固定了。而这个不确定延时可能是很多事件表达式集合在一起以后的作用,这个在仿真中是不可遇见的

4.3.1 事件表达式

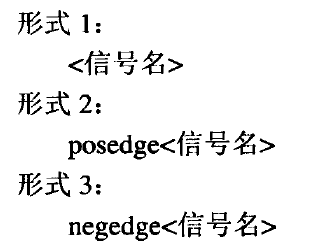

- 事件表达式可以出现以下三种形式

- 形式1是上升沿和下降沿;形式2是上升沿;形式3是下降沿

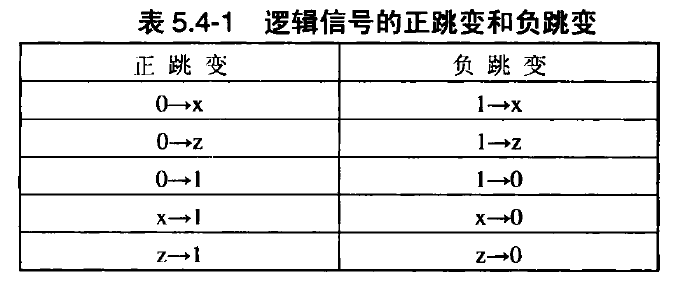

- !!在电路中,正跳负跳就是0-1和1-0,其他状态全都是不正确的状态。而在仿真中,信号有四个电平:0,1,X,Z,对于正跳负跳的规定如下表

- !!电路级的概念只有0-1,1-0成立,而仿真一级,所有概念都成立。所以,可综合语言的语法集要比硬件描述语言的所有语法集要小得多

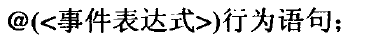

4.3.2 边沿触发语法格式

-

形式1:

-

举例:

-

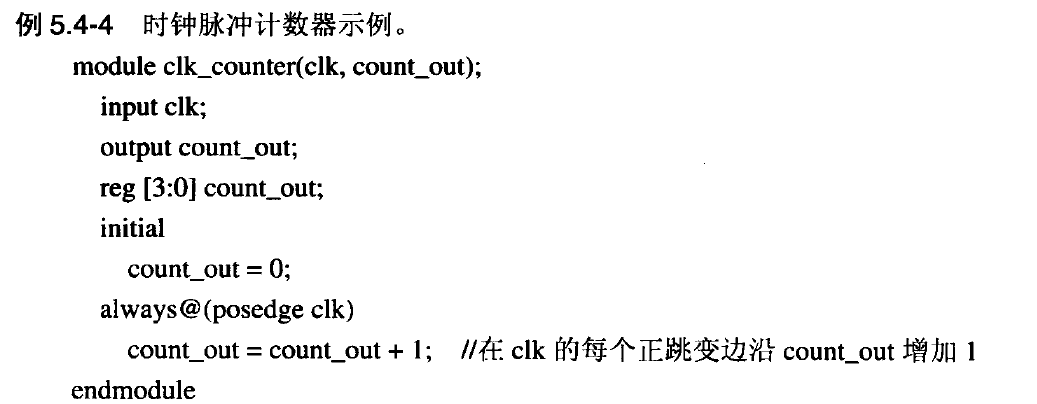

!!选了一个计数器的例子,是为了告诉大家,这种边沿触发的信号,更多的是用于电路,而之前的那些信号更多用于测试和仿真

-

!!所有的语句都可以用在仿真,但是不是所有语句都能用在可综合电路设计

-

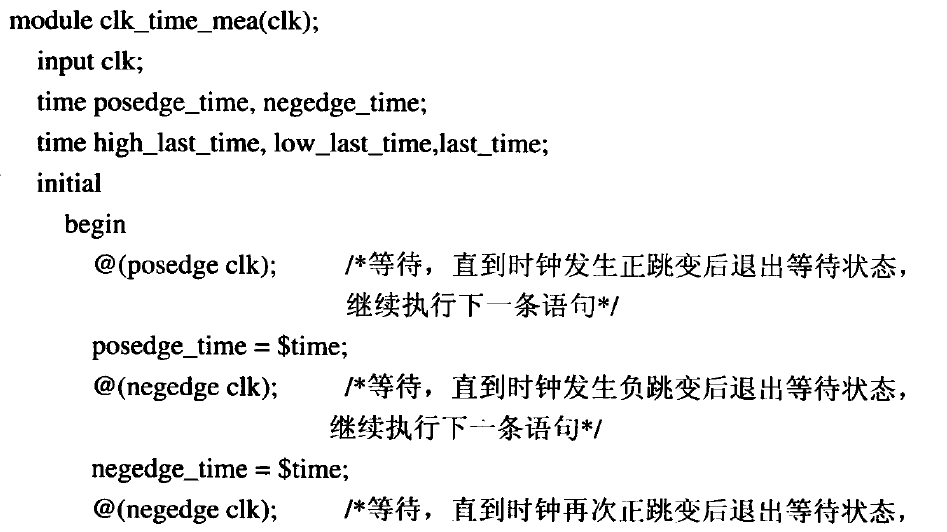

形式2:

-

比如组合电路,只有信号电平发生变化

-

举例

-

这个例子是测量信号仿真中时钟的周期或占空比

-

形式3:

-

形式4:

-

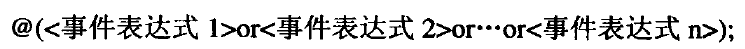

举例:

-

在a的上升沿和b的下降沿到达的时候打印,之前讲过,屏幕打印要找寻特定的时刻,实际上这个就是一种特定的时刻

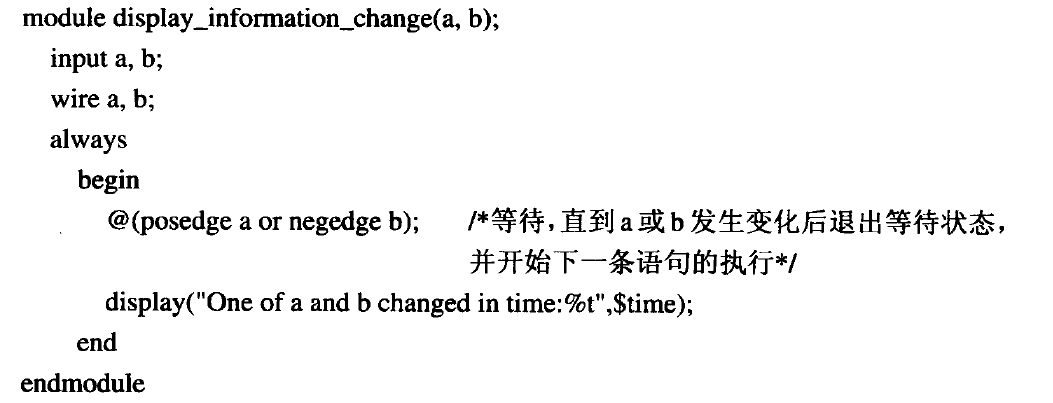

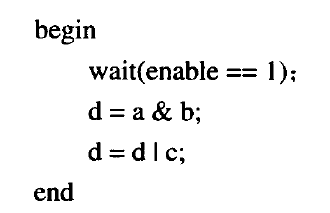

4.4 电平敏感事件

-

电平敏感事件语法格式有两种

-

在边沿敏感的时候@的信号列表,并没有做一个判定

-

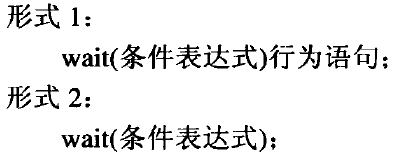

电平敏感的第一种形式:

-

!!这个例子在传统的数字电路中,把它归为时序电路,这个东西叫做latch

-

!!现在用的触发器叫Flip Flop,还有一种电路叫latch,它是靠电平进行锁定的。在latch中你工作在高电平或者低电平,这时输入信号发生变化,输出信号也要发生变化,它的延迟由latch整个的延迟决定,这时一个不可控延迟,latch是一个可控延迟,但是不一定工作过程中输入不变化,这时候的延迟是不可控的

-

这种latch电路在早期是存在的,但是随着技术发展,会发现latch信号非常不稳定。见到latch通常称为异步时序电路,而我们要求的是同步时序电路设计,正是因为异步时序的延迟没办法控制

-

!!一个是电路设计,一个是怎么让时钟在全局网络都变得一致,这两个东西都做的很好,所以同步时序电路在数字电路硬件设计中间占据了绝对的重要地位

-

!!但是异步时序电路也不是没有了,在DSP,单片机中都没有异步,在FPGA中也基本都是同步时序,只有在一个厂家Actel的一个系列的很小一部分有电平敏感

-

!!!我们现在做的东西都是工地的,但是做到航空,导弹上都是隔离的,没有一个共同的地,这时候如果用边沿触发就会带来很多问题,所以电平敏感主要面向于军工

-

电平敏感的第二种形式:

- !!信号赋值语句是硬件描述语言非常重要的一条语句,是对于任意信号形式和实际变量的仿真的一种格式

-

相关阅读:

Linux命令记载

1.4 计算机网络在我国的发展

Spring核心接口ObjectProvider

如何在 qmake(QtCreator)中指定 Mac 平台

【libcurl】7.8.4 MT v142 构建

物联网设备上云难?华为云IoT帮你一键完成模型定义,快速在线调试设备

Spring Cloud教程 第十二弹 Spring Cloud Config整合Spring Cloud Bus实现配置动态刷新

YOLOv6-Openvino和ONNXRuntime推理【CPU】

Odoo免费开源零售门店管理系统:如何设置收银终端的支付方式

当Unity实时3D引擎遇上AI虚实交互,Unity要成为元宇宙时代的新引擎

- 原文地址:https://blog.csdn.net/y_u_yu_yu_/article/details/127944164