-

多线程DPDK应用的内存优化

作者

Conor Walsh is a software engineering intern with the Architecture Team of Intel’s Network Platform Group (NPG), based in Intel Shannon (Ireland).

引言

高速包处理是一种资源密集型应用。一种解决方案是将包处理流水线(pipeline)分离到多线程以提高程序性能。

然而,这样做可能增加缓存(Cache)和内存(Memory)访问的压力。

因此,构建高性能应用程序的关键在于尽可能减少数据面流量(data plane traffic)相关的内存占用(memory footprint)。

本文介绍了一种多线程包处理应用程序的内存优化技术,提高访存密集型应用的性能。

即使应用程序没有内存受限的情况,也应该减少内存需求。参考程序

本文基于对源自Intel的vCMT系统的研究。

vCMTS是基于DOCSIS3.1标准和DPDK包处理框架实现的MAC层数据面流水线程序。

该程序是为了测试Intel至强平台vCMTS数据平面包处理性能及功耗开发的工具。

可以从0.1org的the Access Network Dataplanes下载vCMTS。

虽然本文测试的vCTMS基于DPDK 18.08版本,但是背后的原理可以应用到早期版本的DPDK或者其他包处理库,比如Cisco的VPP。

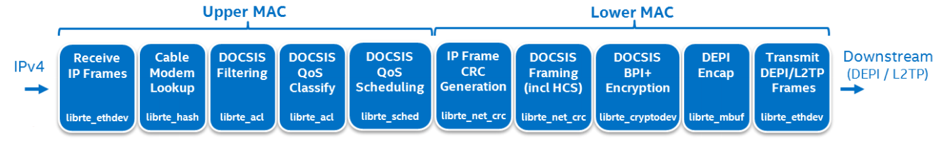

本文用到的一些功能在DPDK 16.07.2首次引入。vCMTS的下行(downstream)部分采用了多线程流水线设计。

流水线分为上/下MAC两部分,分别运行于两个不同的线程。而且这两个线程必须运行于同一个物理核心的2个超线程上,否则会浪费L2 Cache的效率。

参见图1 vCMTS下行包处理流水线

图1 vCMTS下行上 -

相关阅读:

Spring-依赖注入补充

【踩坑系列】发送微信模板消息返回40165 invalid weapp pagepath

SpringAMQP之队列和交换机

物 理 层

【React Router v6】编程式路由导航(useNavigate)

SAGAN

1.2 C++编译器对指针的解释方式(深度理解c++指针)

Freeswitch学习笔记(三):配置

React源码之Fiber架构

强化学习和torchrl

- 原文地址:https://blog.csdn.net/lingshengxiyou/article/details/127893110