-

ARM内核地址对齐访问如何理解

1. 怎么从专业角度理解ARM内核地址对齐访问?

(1)Byte访问都是满足字节对齐访问;

(2)word*n(n=1,2,3… … n)访问是满足字节对齐访问,word对于32位mcu,一个word是32bit;

(3)halfword访问是满足字节对齐访问,halfword对于32位mcu,halfword=16bit。

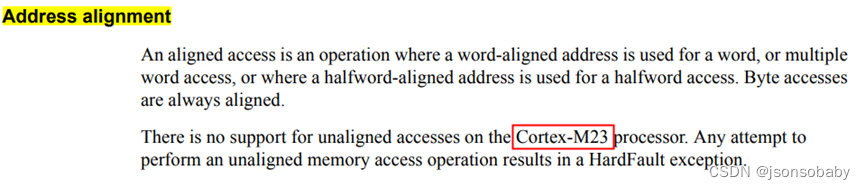

参考资料:《Arm® Cortex® -M23 Devices Revision: r1p0 Generic User Guide》 中3.4.4 Address alignment章节,截图如下:

图 1

2. 不同ARM内核地址对齐访问的要求是怎么样的?

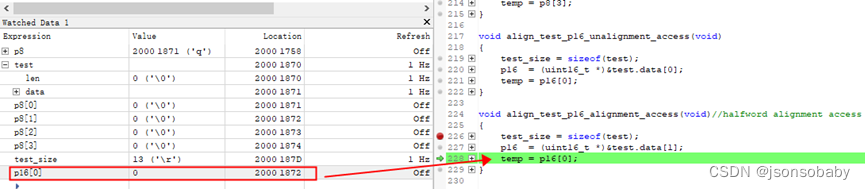

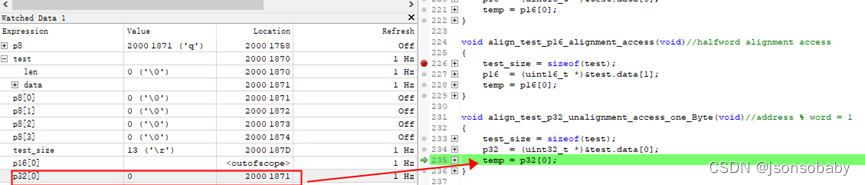

(1)对于M0+和M23内核,所有非地址对齐方式的访问是不允许的,会触发HardFault exception;

图 2

图 3

(2)对于M3、M33和M4内核,允许以下指令非地址对齐访问。

• LDR, LDRT

• LDRH, LDRHT

• LDRSH, LDRSHT

• STR, STRT

• STRH, STRHT

图 4

图 5

图 6

3. 地址非对齐访问会造成什么结果?

(1)地址非对齐访问比地址对齐访问效率更低;

(2)不同平台对地址非对齐访问要求不一样,代码跨平台移植性变差;

(3)可能会触发HardFault exception,即死机;

(4)此外,有些存储区域不支持地址非对齐访问。

综上所述,我们要求程序要保证地址对齐访问。

4. 举例说明,实际用用

用芯片GD23L233CCT6编写各种地址访问为例,GD23L233CCT6是Cortex-M23内核,所有非对齐地址访问都不允许。

定义全局变量:

4.1 Byte访问

按Byte访问如图7,对地址address 0x20001871 0x20001872 0x20001873 0x20001874访问都不会出现死机,对应第一章讲到的“(1)Byte访问都是满足字节对齐访问”。

图 7

4.2 Halfword访问

对于32位mcu,Halfword访问地址对齐是指访问地址满足”address%2 = 0”,以下是各种不同地址访问情况。

(1)如图8,对地址address 0x20001872访问,不会出现死机现象,对应第一章讲到的“(3)halfword访问是满足字节对齐访问,halfword对于32位mcu,halfword=16bit”。

图 8

(2)如图9,对地址address 0x20001871访问,出现死机现象,此地址不满足halfword对齐。如图10,是触发地址非对齐访问异常死机标志。

图 9

图 10

4.3 word访问

对于32位mcu,word访问地址对齐是指访问地址满足”address%4 = 0”,以下是各种不同地址访问情况。

(1)如图11,对地址0x20001871的访问不是word access,会出现如图10所示死机问题。

图 11

(2)如图12,对地址0x20001872的访问不是word access,会出现如图10所示死机问题。

图 12

(3)如图13,对地址0x20001873的访问不是word access,会出现如图10所示死机问题。

图 13

(4)如图14,对地址0x20001874的访问word access,不会出现死机问题,对应第一章讲到的“(3)halfword访问是满足字节对齐访问,halfword对于32位mcu,halfword=16bit”。

图 14

-

相关阅读:

常见6种易被忽略的软件隐藏缺陷

RPA案例|云扩助力保险行业开启超自动化运营新阶段

【TypeScript笔记】02 - TS高级类型

Acwing 3302. 表达式求值

node.js+uniapp(vue),阿里云短信验证码

基于微信小程序的电动车智能充电系统设计与实现(源码+lw+部署文档+讲解等)

【Golang】Golang学习day01:初识Golang

51、图论-岛屿数量

硕士论文章节划分

洛谷P5723 【深基4.例13】质数口袋

- 原文地址:https://blog.csdn.net/jsonsobaby/article/details/127792286