-

第三章-存储系统-Cache和页式存储、虚拟存储

第三章-存储系统-Cache和页式存储、虚拟存储

Cache的基本概念与原理

Cache的工作原理

-

前期存在的问题:CPU与内存的速度差异

-

添加Cache缓和速度矛盾

-

-

实际上,Cache被集成在CPU内部Cache用SRAM实现,速度快,成本高

程序的局部性原理

-

空间局部性,在最近未来要用的信息,很有可能与现在正在使用的信息咋存储空间上是邻近的

- 数组元素,顺序执行的指令代码

-

时间局部性:在最近的未来要用的信息,很可能现在正在使用的信息

- 循环结构指令代码

-

基于局部性原理,不难想到,可以把CPU目前访问的地址“周围”的部分数据放入Cache中;

性能分析

-

例题:

有待解决的问题:如何确定地址:”周围“的部分数据当道Cache中;

以块为单位进行数据交换

- Cache和主存的映射关系?

- Cache写策略

- Cache满了怎么办?

Cache和主存的映射方式

1 全相联映射

- 主存块可以放在Cache的任意位置

2 直接映射

- 每个主存块只能放在一个特定的位置

Cache块号=主存块号%Cache总块数

3 组相联映射

总结:

Cache的替换算法

替换算法解决Cache装满的问题

1、对于全相联映射:Cache完全满了才需要替换,且需要在全局选择替换哪一块;

2 直接映射:如果对应位置非空,则毫无选择的替换,无需算法选择;

3 组相联映射:分组内满了才需要替换,需要在分组内选择替换哪一块;随机算法(RAND):若Cache已满,则随机选择一块替换

-

-

未考虑到局部性原理

先进先出(FIFO)算法

- 未考虑到局部性原理

近期最少使用算法(LRU)

为每个Cache块设置一个“计数器”,用于记录每个Cache块已经有多久没有被访问,然后替换最大的

最不经常使用算法(LFU)

总结:

Cache的写策略

保证数据的一致性

写命中

-

全写法

-

写回法

写不命中

总结

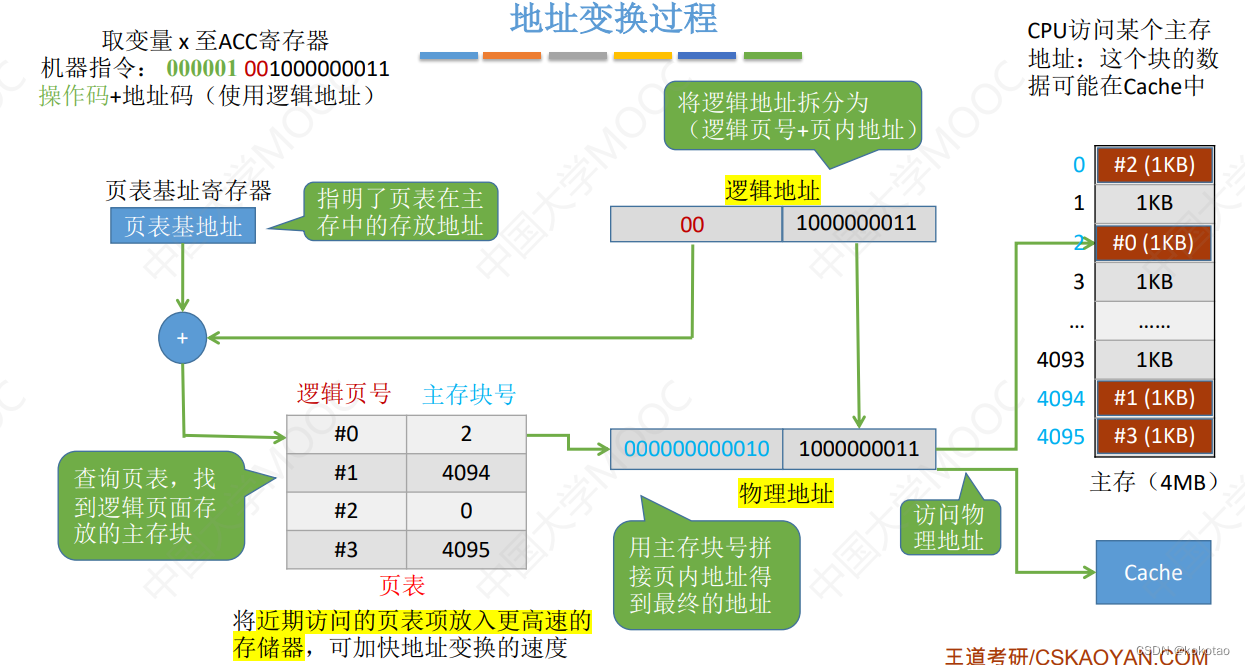

页式存储

页式储存系统:一个程序在逻辑上被分为若干个大小相等的“页面” “页面”大小与“块”的大小相同。每个页面可以离散地放入不同的主存块中。

虚地址与实地址

-

把逻辑页号映射到主存块号

-

页表:逻辑页→主存块号

-

CPU执行的机器指令中,使用的是“逻辑地址”,因此需要通过“页表”将逻辑地址转为物理地址。页表的作用;

记录了每个逻辑页面放在哪个主存块中; -

-

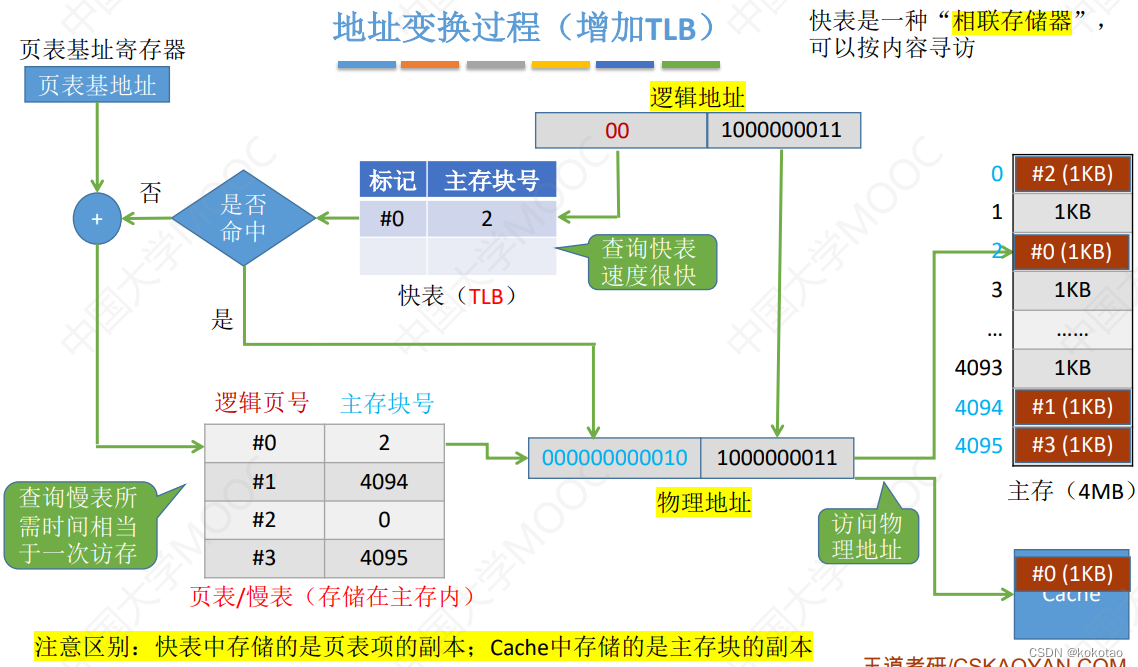

引入快表(TLB)

总结:

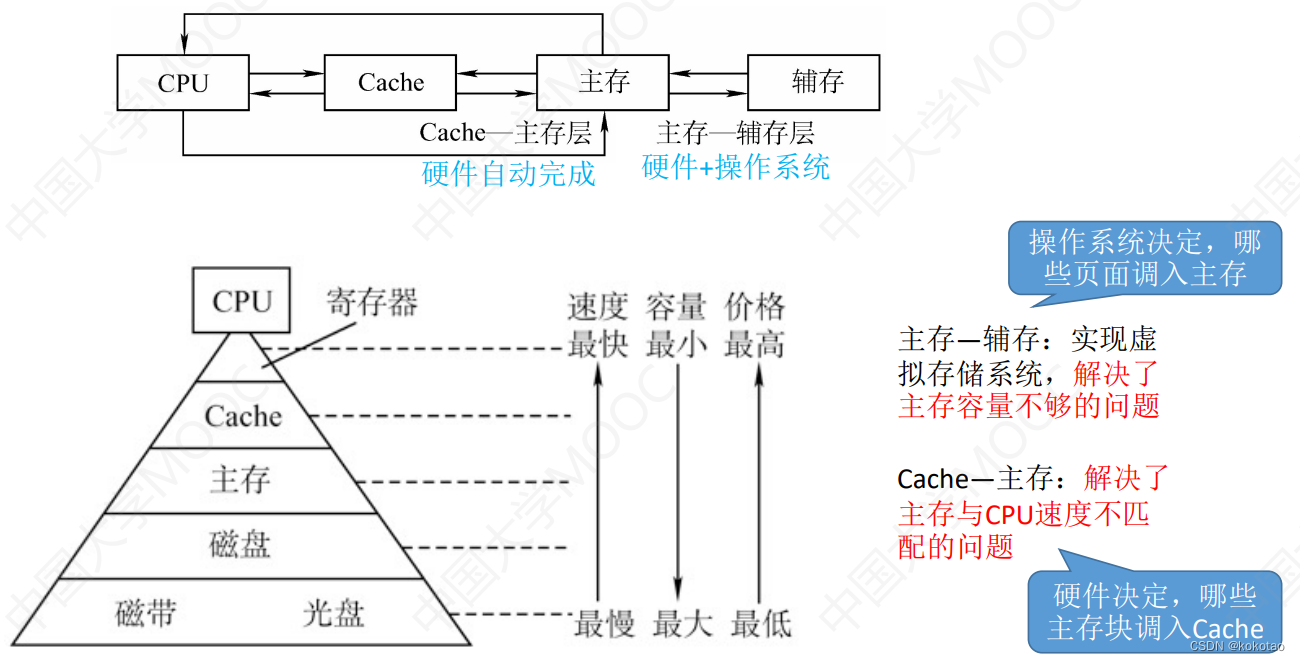

虚拟存储器

存储器层次结构

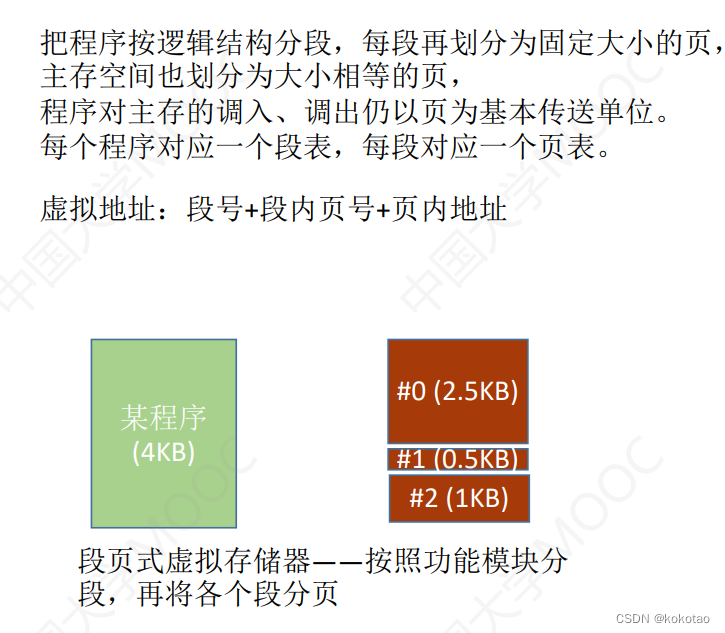

段页式虚拟存储器

-

-

相关阅读:

FastAPI学习-21.response 参数-设置响应Cookies

定时任务报警通知解决方案详解

Java面试题——进程和线程的关系

算法金 | 10 大必知的自动化机器学习库(Python)

Oracle LiveLabs实验:Load and Analyze Your Data with Autonomous Database

CAD新建文件快捷方式 开启显示文件选项卡

搞一个自己用的node-cli

融合定位在石油化工人员定位中应用

16_Vue列表渲染中key的工作原理和虚拟DOM对比算法

Command

- 原文地址:https://blog.csdn.net/weixin_44698624/article/details/127044669