-

1307_嵌入式设计中的晶振测试小结

全部学习汇总: https://github.com/GreyZhang/g_hardware_basic

前段时间工作之中遇到了一个控制器晶振不起振的问题,这个并不是我的专业方向,但是也让我遇到了一个比较新的问题。其实,从设计角度来说这个功能应该不是硬件的孤立问题,跟软件设计也是有一定的相关度的。在解决了晶振的起振问题之后,接着大家都陷入了晶振赋值合理范围的讨论。时至今日,还是没有看到一个完整的结论。

关于晶振幅值的讨论,第一次有一点认识其实还是在mega328p上。在这个MCU上其实是有一个满福震荡的概念的,可以在软件中做一个熔丝编程设置。从原理的角度讲,究竟这个合理范围是多少我还是不是很清楚,但是我觉得可以结合我手里的几个板子的测试情况先大概了解一下现在的一些经常打交道的板子的晶振现状。以后玩什么开发板的时候,或许这个也应该加入到我的测试条目中了。

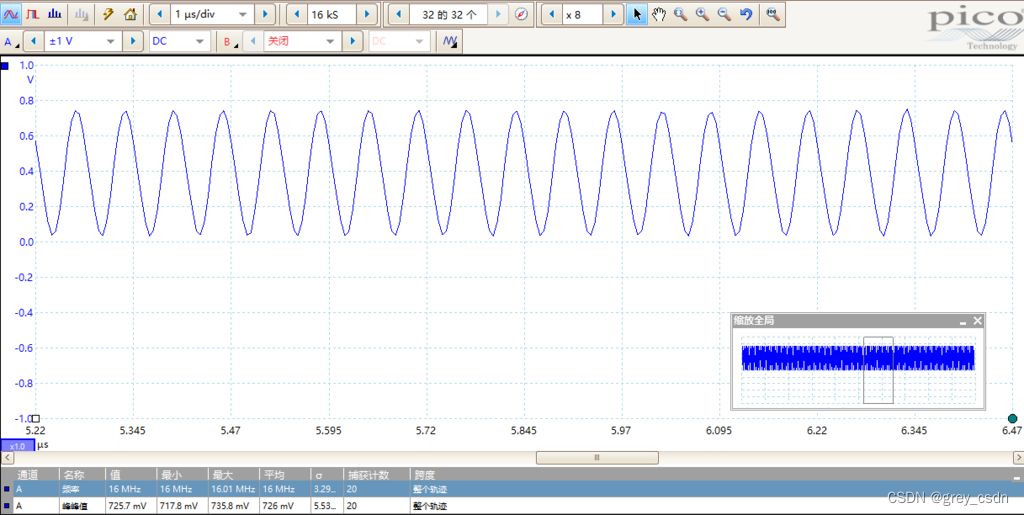

首先,还是先看看我的通勤兵Arduino UNO。

这个是Arduino的晶振波形,16MHz的数值跟实际的情况一致。同时,我在测量中增加了峰峰值的测量,这里测试出来的结果是725mv。

接下来,我尝试测试了一个全新的板子,上面的晶振是8M的,但是我没有测试到波形。咨询了我们的测试工程师,得到的信息是没有烧写程序就不会有震荡。这个的确是再次增加了我的知识系统中的条目,晶振的起振居然是软件可以控制的。

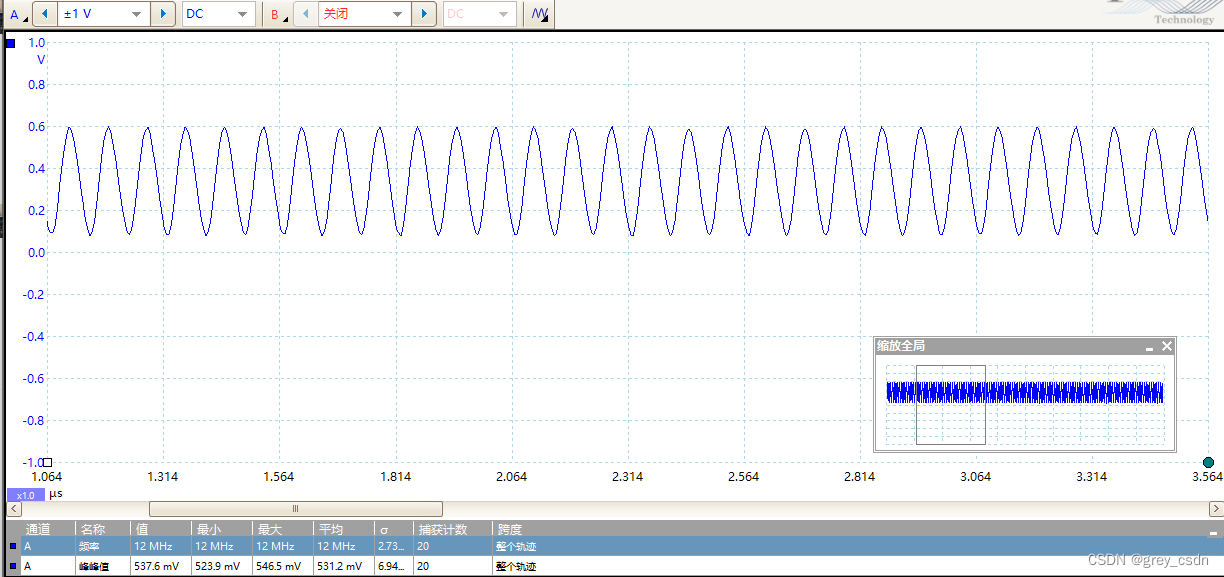

进一步,我测试了一款国产ARM MCU的晶振,这个板子是我一直在用的。之前更换过晶振,从原始的24M改成了12M,但是功能已经验证过了,从软件的侧面可以看出来修改后的是可以起振的。

这是测试出来的结果,12M的频率看起来是正确的。晶振振幅的峰峰值是537mv。

进一步,我尝试测试一个F103的板子。软件运行是没问题的,一直用来做一个小测试。但是,这个板子我一直测试不到波形。我怀疑过示波器,换了一个没用,也换过示波器的探头,也换了另一个差不多的板子。都是没有波形。我怀疑过晶振出问题,但是前面既然问了同事说这个可能跟软件有关那还是先去排查一下看看。我查看了软件设计,发现我烧录的测试程序采用的时钟源其实是内部时钟。会是这个原因吗?我先忽略了软件的基本功能调整,先去在软件中把最初的时钟源改成了晶振。这一次,果真测试到了波形。

上面是F103的板子上的波形,8M的数值是正确的。这里发现,这个晶振波形峰峰值达到了2.255V,是这几个板子中最高的一个。

这只是一个简单的开始,但是对我来说算是一个全新的知识点。虽然看结论简单,但是中间的过程的确是值得去品味一下,也值得记录回顾。

-

相关阅读:

玩转MyBatis-Plus分页插件一:分页基本使用+方法解释+解析Page对象

使用 OpenCV 通过 SIFT 算法进行对象跟踪

高数 |【23数一 李林六套卷】卷一 自用思路 及 知识点 整理

HLS学习1:点灯

【C++】C向C++的知识过度(上)

Hadoop生态系统—数据仓库Hive的安装

多线程JUC 第2季 多线程的原子性

linux之mail命令发邮件

2023.10.02 win7x64sp1下Navicat_Premium15_x86连接Oracle_10g(安装在win2003x86)

跑跑飞弹室外跑步AR游戏代码方案设计

- 原文地址:https://blog.csdn.net/grey_csdn/article/details/125904260