-

DDR存储器中的一些概念

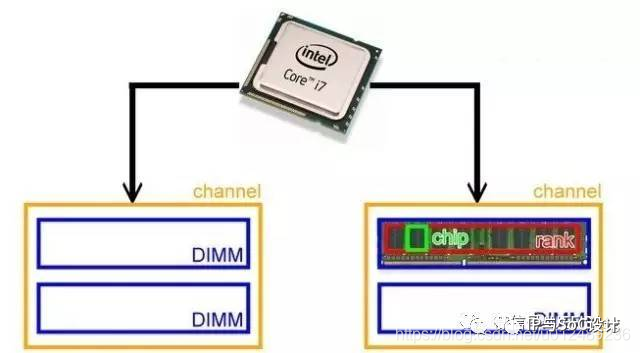

例子中,一个i7 CPU支持两个Channel(双通道),每个Channel上可以插俩个DIMM,而每个DIMM由两个rank构成,8个chip组成一个rank。由于现在多数内存颗粒的位宽是8bit,而CPU带宽是64bit,所以经常是8个颗粒可以组成一个rank。所以小张的内存条2R X 8的意思是由2个rank组成,每个rank八个内存颗粒(为啥我们以后讲)。由于整个内存是4GB,我们可以算出单个内存颗粒是256MB。

========================================================================

这是个DDR3一个Rank的示意图。我们把左边128MB Chip拆开来看,它是由8个Bank组成,每个Bank核心是个一个存储矩阵,就像一个大方格子阵。这个格子阵有很多列(Column)和很多行(Row),这样我们想存取某个格子,只需要告知是哪一行哪一列就行了,这也是为什么内存可以随机存取而硬盘等则是按块存取的原因,实际上每个格子的存储宽度是内存颗粒(Chip)的位宽,在这里由8个Chip组成一个Rank,而CPU寻址宽度是64bit,所以64/8=8bit,即每个格子是1个字节。

========================================================================

DDR4芯片有20根地址线(17根Address、2根BA、1根BG),16根数据线。在搞清楚这些信号线的作用以及地址信号为何还有复用功能之前,我们先抛出1个问题。假如我们用20根地址线,16根数据线,设计一款DDR,我们能设计出的DDR寻址容量有多大?

Size(max)=(2^20) * 16=1048576 *16=16777216bit=2097152B=2048KB=2MB。

但是事实上,该DDR最大容量可以做到1GB,比传统的单线编码寻址容量大了整整512倍,它是如何做到的呢?答案很简单,分时复用。我们把DDR存储空间可以设计成如下样式:

首先将存储空间分成两个大块,分别为BANK GROUP0和BANK GROUP1,再用1根地址线(还剩19根),命名为BG,进行编码。若BG拉高选择BANK GROUP0,拉低选择BANK GROUP1。(当然你也可以划分成4个大块,用2根线进行编码)

再将1个BANK GROUP区域分成4个BANK小区域,分别命名为BANK0、BANK1、BANK2、BANK3。然后我们挑出2根地址线(还剩余17根)命名为BA0和BA1,为4个小BANK进行地址编码。

此时,我们将DDR内存颗粒划分成了2个BANK GROUP,每个BANK GROUP又分成了4个BANK,共8个BANK区域,分配了3根地址线,分别命名为BG0,BA0,BA1。然后我们还剩余17根信号线,每个BANK又该怎么设计呢?这时候,就要用到分时复用的设计理念了。

剩下的17根线,第一次用来表示行地址,第二次用来表示列地址。现在修改为传输2次地址,在传输1次数据,寻址范围最多被扩展为2GB。虽然数据传输速度降低了一半,但是存储空间被扩展了很多倍。这就是改善空间。

所以,剩下的17根地址线,留1根用来表示传输地址是否为行地址。

·在第1次传输时,行地址选择使能,剩下16根地址线,可以表示行地址范围,可以轻松算出行地址范围为2^16=65536个=64K个。

·在第2次传输时,行地址选择禁用,剩下16根地址线,留10根列地址线表示列地址范围,可以轻松表示的列地址范围为2^10=1024个=1K个,剩下6根用来表示读写状态/刷新状态/行使能、等等复用功能。

·这样,我们可以把1个BANK划分成67108864个=64M个地址编号。如下所示

·所以1个BANK可以分成65536行,每行1024列,每个存储单元16bit。

-每行可以存储1024*16bit=2048bit=2KB。每行的存储的容量,称为Page Size。

-单个BANK共65536行,所以每个BANK存储容量为65536*2KB=128MB。

-单个BANK GROUP共4个BANK,每个BANK GROUP存储容量为512MB。

-单个DDR4芯片有2个BANK GROUP,故单个DDR4芯片的存储容量为1024MB=1GB。

至此,20根地址线和16根数据线全部分配完成,我们用正向设计的思维方式,为大家讲解了DDR4的存储原理以及接口定义和寻址方式。

=========================================================================

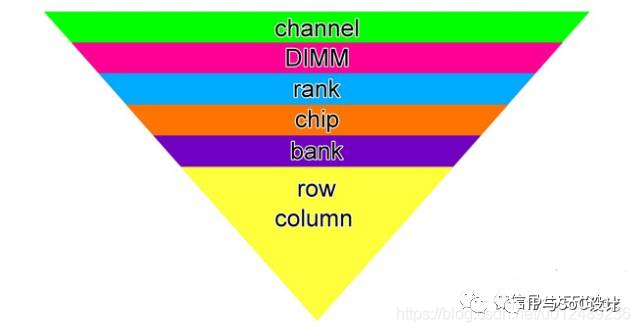

·Channel:一个主板上可能有多个插槽,用来插多根内存。这些槽位分成两组或多组,组内共享物理信号线。这样的一组数据信号线、对应几个槽位(内存条)称为一个channel(通道)。简单理解就是DDRC(DDR控制器),一个通道对应一个DDRC。CPU外核或北桥有两个内存控制器,每个控制器控制一个内存通道。内存带宽增加一倍。(理论上)

·DIMM(dual inline memory module)是主板上的一个内存插槽。一个Channel可以包括多个DIMM。

·Rank是一组内存芯片的集合,当芯片位宽x芯片数=64bits(内存总位宽)时,这些芯片就组成一个Rank。一般是一个芯片位宽8bit,然后内存每面8个芯片,那么这一面就构成一个Rank(为了提高容量,有些双面内存条就有两个rank。在DDR总线上可以用一根地址线来区分当前要访问的是哪一组)。同一个Rank中的所有芯片协作来共同读取同一个Address(一个Rank8个芯片 * 8bit = 64bit),这个Address的数据分散在这个Rank的不同芯片上。设计Rank的原因是这样可以使每个芯片的位宽小一些,降低复杂度。

·Chip是内存条上的一个芯片。由图中是由8个bank组成了一个memory device。

·Bank:Bank是一个逻辑上的概念。一个Bank可以分散到多个Chip上,一个Chip也可以包含多个Bank。Bank和Chip的关系可以参考下面的图,每次读数据时,选定一个Rank,然后同时读取每个chip上的同一bank。

·Row/Column组成的Memeory Array:Bank可以理解为一个二维数组bool Array[Row][Column]。而Row/Column就是指示这个二维数组内的坐标。注意读取时每个Bank都读取相同的坐标。

-

相关阅读:

Rust中的智能指针:Box<T> Rc<T> Arc<T> Cell<T> RefCell<T> Weak<T>

PMP每日一练 | 考试不迷路-11.19(包含敏捷+多选)

pytorch深度学习实战lesson25

Redis无法正常连接

分布式服务的接口幂等性如何设计

IDE应用kotlin官方编码规范并配置阿里java开发规约插件

UNCTF-日常训练-reverse-ezRust

前后端接口设计与配置中心系统<二十九>-------HiAbility SDK开发4【支付能力集成】

【详细讲解Edge使用心得与深度探索】

自然语言处理应用(一):情感分析

- 原文地址:https://blog.csdn.net/rainbowbirds_aes/article/details/125891069