-

基于FPGA的误码检测

基本原理

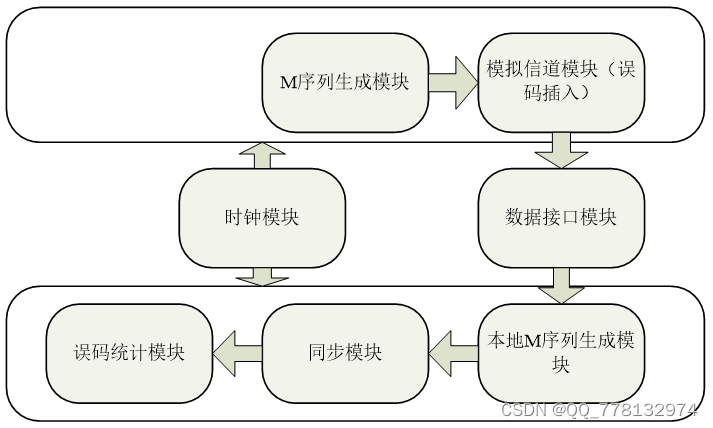

主要分为以下几个部分:

(1)锁相环

(2)M序列生成模块

(3)数据接口模块

(4)模拟信道模块

(5)本地M序列生成模块

(6)同步模块

(7)误码统计模块

锁相环

主要产生系统时钟信号和输出同步时钟信号。

采用Altera自带的IP模块

M序列生成模块

伪随机信号发生器又叫PN序列发生器或者是m序列发生器。m序列是一种线性反馈寄存器序列,m序列的产生可以利用r级寄存器产生长度为2^r-1的m序列,该实验中采用3级寄存器产生7序列发生器。其原理框图如下:(实验中反馈的信号采用异或进行反馈)数据接口模块

由于没有实际信道,所以收发模块预留,这里进行了人为地插入误码,并将此误码作为模拟实际的信道。模拟信道模块

误码插入模块,采用的简单的方法进行插入。

根据输入的M序列和序列的位置,对某些想要插入的位置的M序列进行取反操作,然后进行插入。

本地M序列生成模块

与M序列生成模块相同。

同步模块

同步判断是进行误码统计的先决条件,只有对接收的码序列与本地码序列不断地进行同步判断,确定收、发端处于同步状态,那么误码统计才有意义。在通信系统中同步的方法有很多,通常采用的方法有滑动相关法,匹配滤波法等。

本设计中采用的是滑动相关法,以7个 -

相关阅读:

mybatis-plus分页

数据结构--7.1散列表(哈希表)查找

MySQL精简复习

[附源码]Python计算机毕业设计Django医院门诊管理信息系统

USB协议学习(二)设备枚举过程分析

linux驱动开发led绑定亮灯

MacOS怎么配置JDK环境变量

Centos下载配置Maven

go-zero jwt 鉴权快速实战

GBase 8s是否支持同城复制

- 原文地址:https://blog.csdn.net/QQ_778132974/article/details/127135105