-

FPGA/HDL 开发的 10 条规则

HDL 开发的 10 条规则

编写良好的、可移植的、可重用的 HDL 代码,使设计能够以所需的频率实现,这绝对是一个挑战。

为此,许多(不是大多数)专业组织都有编码标准。不过,编码规则可能会成为战场。一些公司的编码规则非常复杂,不仅控制代码结构,还控制格式和命名,而有些公司则稍微宽松一些。

但是,如果你是专业开发 FPGA,或者是作为爱好者,都应该有一些基本的编码规则。当你来到项目的后端并且必须实现时序收敛时,遵守这些基本规则可以节省大量时间和精力。为此,我开始思考我的 HDL 开发的 10 大规则是什么??

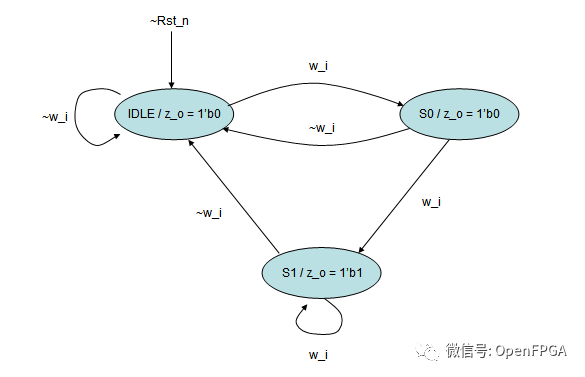

状态机——只是单个进程。忘记关于组合部分和顺序部分的学校和课程。所有状态机都应该是单个进程。这有助于调试,防止锁存器的出现,并确保所有输出都是寄存器类型,从而减少毛刺并帮助我们实现时序收敛。

状态机——尽可能多地从状态机中解耦功能。这意味着确保计

-

相关阅读:

把握经济大势和个人财运密码必须读懂钱—现代金钱的魔力

RK3399平台开发系列讲解(FLASH篇)内核MTD层数据结构体

后端传递数据给前端做导出Excel的vo类

从零手写实现 nginx-13-nginx.conf 是 HOCON 的格式吗?

PostgreSQL之SQL高级特性

关于#c++#的问题,请各位专家解答!

网页正文获取易语言代码

基于SSH开发新闻管理系统

FFmpeg进阶-给视频添加马赛克效果

MySQL的锁

- 原文地址:https://blog.csdn.net/Pieces_thinking/article/details/127116577