-

学习:DDR3基础知识(1)

1 DDR3 简介

1.1 DDR存储器介绍

1、DDR3,即第三代双倍数据率同步动态随机存取存储器(Double-Data-Rate Three Synchronous Dynamic Random Access Memory,一般称为DDR3 SDRAM)。

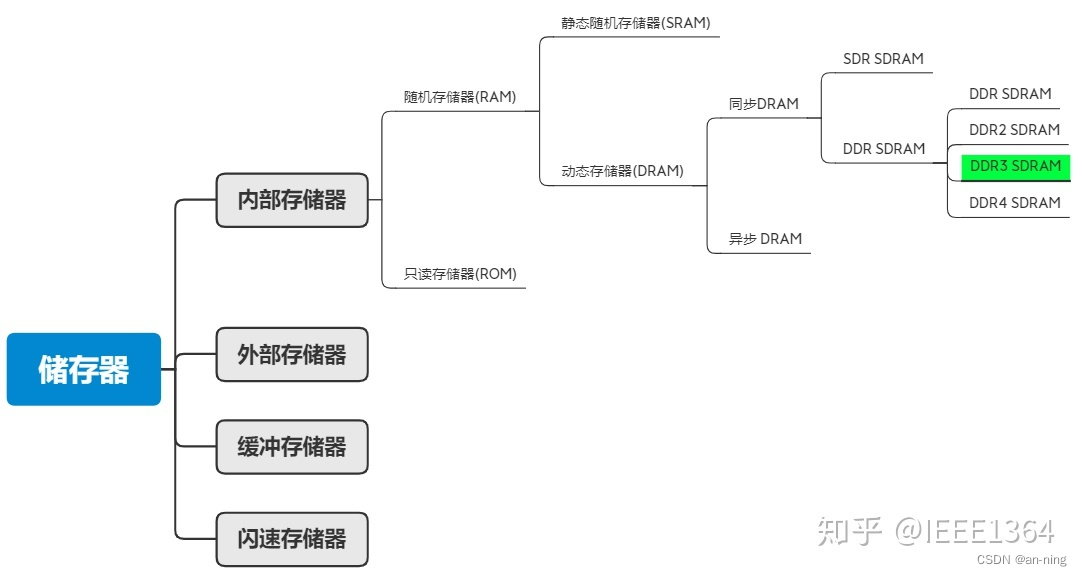

2、存储器一般来说可以分为内部存储器(内存),外部存储器(外存),缓冲存储器(缓存)以及闪存这几个大类。内存也称为主存储器,位于系统主机板上,可以同CPU直接进行信息交换。其主要特点是:运行速度快,容量小。

3、DDR3即属于内部存储器,内部存储器又分为随机存储器(RAM)和只读存储器(ROM),RAM划分为静态存储器(SRAM)和动态存储器(DRAM),静态存储器不需要进行电路刷新也能保持内部数据的稳定,而动态存储器则需要每隔一段时间进行刷新,否则内部保存的数据就会丢失。DDR从发展到现在已经经历了四代,分别是:第一代DDR SDRAM,第二代DDR2 SDRAM,第三代DDR3 SDRAM,第四代,DDR4 SDRAM。

1.2 基本技术原理

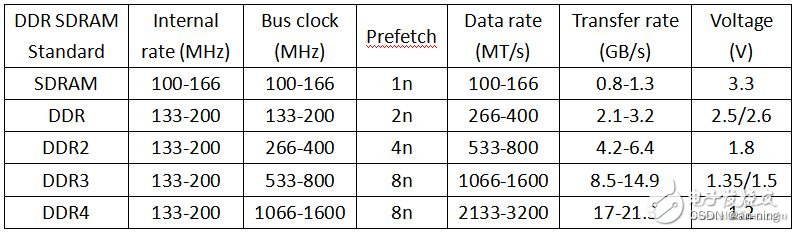

1、DDR里面主要使用了Double Data Rate 和 Prefetch两项技术。实际上,无论是 SDR 还是 DDR 或 DDR2、DDR3,其内存芯片内部的核心时钟基本上是保持一致的,都是 100MHz 到 200MHz(某些厂商生产的超频内存除外)。

DDR即 Double Data Rate 技术使数据传输速度较 SDR 提升了一倍。如下图所示,SDR 仅在时钟的上升沿传输数据,而 DDR 在时钟信号上、下沿同时传输数据。例如同为133MHz 时钟,DDR 却可以达到 266Mb/s 的数传速度。

2、芯片内部数据数据传输速度的提升则是通过 Prefetch 技术实现的。所谓 Prefetch 简单的说就是在一个内核时钟周期同时寻址多个存储单元并将这些数据以并行的方式统一传输到 IO Buffer 中,之后以更高的外传速度将 IO Buffer 中的数据传输出去。这个更高的速度在 DDR I 上就是通过 Double Data Rate 实现的,也正因为如此,DDR I 外部 Clock 管脚的频率与芯片内部的核心频率是保持一致的。如下图所示

DDR I 的Prefetch 过程:在 16 位的内存芯片中一次将 2 个 16bit 数据从内核传输到外部MUX 单元,之后分别在 Clock 信号的上、下沿分两次将这 2 x 16bit 数据传输给北桥或其他内存控制器,整个过程经历的时间恰好为一个内核时钟周期。2 存储结构及工作原理

2.1 存储结构

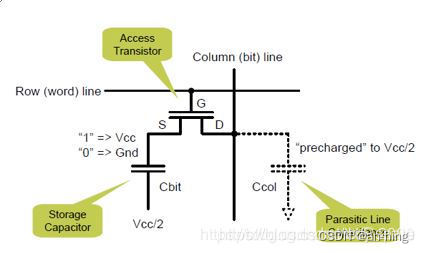

1、DDR3的一个存储电容为其基本存储单元,当access transitor被选通时,可进行读写操作

2.2 大概工作原理

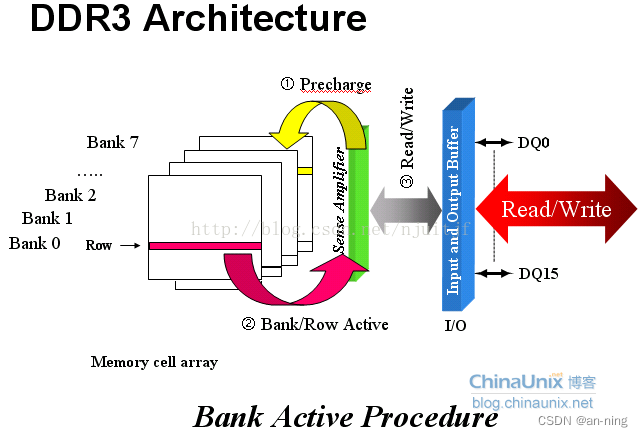

1、DDR3的内部是由基本存储单元组成的存储阵列,所谓读写操作技是将数据填进去和将里面的数据读出来的过程。我们可以将其存储阵列想象成一个表格,和表格的·1检索原理一样,当我们进行寻址时,需要先指定Bank,然后在指定行(Row),最后指定列(Column),这样就可以得到一个固定的单元格,这就是DDR内存芯片寻址的基本原理,而对于DDR来说,每张表格就是一个逻辑Bank(存储阵列),而一个单元格就是一个存储单元。DDR3工作时则先进行预充电处理,然后行选通,最后再进行列读写(具体的工作过程及名词解释可以参照:SDRAM的数据存储实现并对其数据进行读写操作),DDR是在SDRAM的基础上发展而来的,因此很多地方还是相同的。

2、下图就是我们将Bank抽象成一张表格的形式,目前市场上的DDR3一般是八个Bank的,行地址使用R代表,列地址用C代表,B代表Bank地址编号,如果寻址命令是B1、R2、C6,那么对应的确定的地址就是图中标红的位置

目前DDR3内存芯片基本上都是8个Bank设计,也就是说一共有8个这样的“表格”,寻址的流程也就是先指定Bank地址,再指定行地址,然后指列地址最终的确寻址单元。

2.3 DDR、SDRAM之间的区别

1、各速率之间的区别

2、DDR SDRAM(Double Data Rate SDRAM):为双信道同步动态随机存取内存,是新一代的SDRAM技术。别于SDR(Single Data Rate)单一周期内只能读写1次,DDR的双倍数据传输率指的就是单一周期内可读取或写入2次。在核心频率不变的情况下,传输效率为SDR SDRAM的2倍。第一代DDR内存Prefetch为2bit,是SDR的2倍,运作时I/O会预取2bit的资料。举例而言,此时DDR内存的传输速率约为266~400 MT/s不等,像是DDR 266、DDR 400都是这个时期的产品。

3、DDR2 SDRAM(Double Data Rate Two SDRAM):为双信道两次同步动态随机存取内存。DDR2内存Prefetch又再度提升至4 bit(DDR的两倍),DDR2的I/O频率是DDR的2倍,也就是266、333、400MHz。举例:核心频率同样有133~200MHz的颗粒,I/O频率提升的影响下,此时的DDR2传输速率约为533~800 MT/s不等,也就是常见的DDR2 533、DDR2 800等内存规格。

4、DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。DDR3内存Prefetch提升至8 bit,即每次会存取8 bits为一组的数据。DDR3传输速率介于 800~1600 MT/s之间。此外,DDR3 的规格要求将电压控制在1.5V,较DDR2的1.8V更为省电。DDR3也新增ASR(AutomaTIc Self-Refresh)、SRT(Self-Refresh Temperature)等两种功能,让内存在休眠时也能够随着温度变化去控制对内存颗粒的充电频率,以确保系统数据的完整性。

5、DDR4 SDRAM(Double Data Rate Fourth SDRAM):DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200 MT/s。DDR4 新增了4 个Bank Group 数据组的设计,各个Bank Group具备独立启动操作读、写等动作特性,Bank Group 数据组可套用多任务的观念来想象,亦可解释为DDR4 在同一频率工作周期内,至多可以处理4 笔数据,效率明显好过于DDR3。 另外DDR4增加了DBI(Data Bus Inversion)、CRC(Cyclic Redundancy Check)、CA parity等功能,让DDR4内存在更快速与更省电的同时亦能够增强信号的完整性、改善数据传输及储存的可靠性。

参考

https://blog.csdn.net/limanjihe/article/details/109060901

https://blog.csdn.net/a_chinese_man/article/details/73381338

https://www.elecfans.com/bandaoti/cunchu/20171117581277.html -

相关阅读:

java word转pdf、word中关键字位置插入图片 工具类

6月第4周榜单丨飞瓜数据UP主成长排行榜(哔哩哔哩平台)发布!

【Linux】25. 生产者消费者模型

基于JAVA+SpringBoot+Mybatis+MYSQL的车辆信息管理系统

(其他) 剑指 Offer 61. 扑克牌中的顺子 ——【Leetcode每日一题】

vue项目中定制化音频展示,wavesurfer.js基本使用

【Redis】Redis的特性和应用场景 · 数据类型 · 持久化 · 数据淘汰 · 事务 · 多机部署

计算机组成原理--------12.4---------开始

Fibonacci数列那些事!

【sql】面试题join on和where

- 原文地址:https://blog.csdn.net/qq_46689721/article/details/126995070