-

Xilinx AXI USB2.0 Device IP 手册阅读笔记

目录

1. 前言

手册链接:

AXI Universal Serial Bus (USB) 2.0 Device v5.0 LogiCORE IP Product Guide

(官网搜pg137也行)The AXI USB 2.0 Device 在Block Design中的样子:

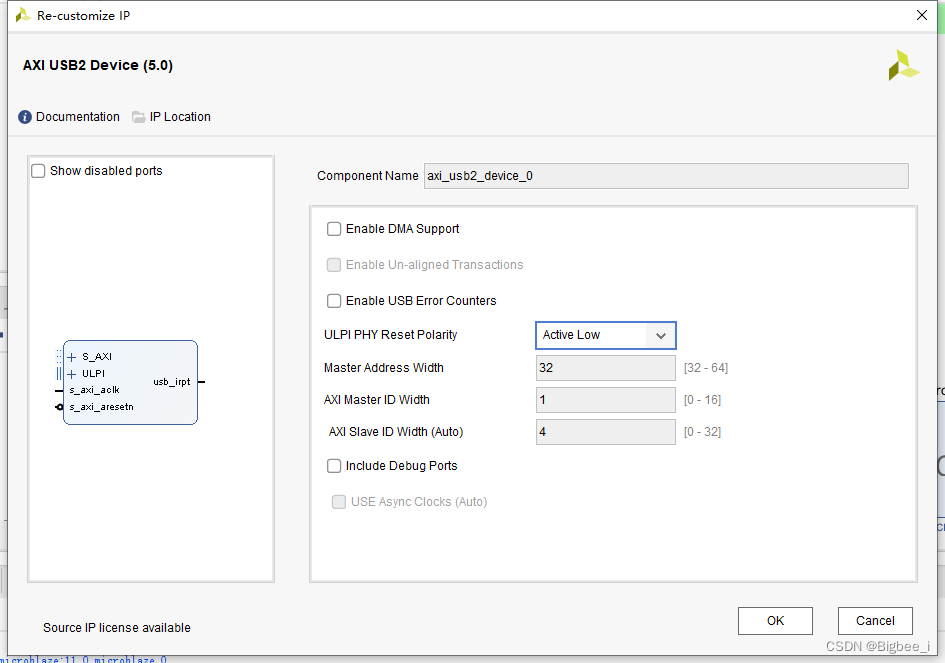

IP默认配置:

很明显FPGA逻辑做主,USB设备做从

2. 概要

2.1 USB2.0协议特点:

- 半双工

- 串行

- 支持480MHz(High Speed)和12MHz (Full Speed)

- 即插即用

- 主从模式

- 每个设备在USB 2.0总线上都有一个地址,并且有一个或多个作为数据源或接收器的Endpoint。所有设备都具有系统控制端点(Endpoint0)。

这些都是USB2.0协议内规定的,可以参考博客。USB2.0协议原文阅读笔记

2.2 The AXI USB 2.0 Device介绍

拥有:1个Endpoint0,7个用户Endpoint

2.2.1 Endpoint0:

Endpoint0只处理控制事务,这些事务从一个8字节的Setup包开始,后面跟着0个或多个数据包。数据包最多可为64个字节,IP专门开辟了一个DRAM进行存储。Setup在0x80,数据包在0x00。如果收到Setup包,SetupPkt 会被置位,如果Data包成功发送或接收,FIFOBufFree和FIFOBufRdy会被置位

Setup packet Data packet 8byte 0~64byte 0x80 0x00 SetupPkt FIFOBufFree / FIFOBufRdy 2.2.2 Endpoint1~7:

- 7个用户端点可以配置为 bulk、interrupt、isochronous三种传输模式。

- 端点可以被设置为INPUT(to the host)或者OUTPUT(form the host)

- 拥有一片乒乓的存储空间用于存储数据

- 用户端点数据缓冲区是单向的,并由各自端点的端点配置和状态寄存器进行配置

- 缓冲区的大小可以配置为0到512字节用于bulk,64字节用于interrupt,多达1024字节用于isochronous

3. 详细说明

3.1 总体框图

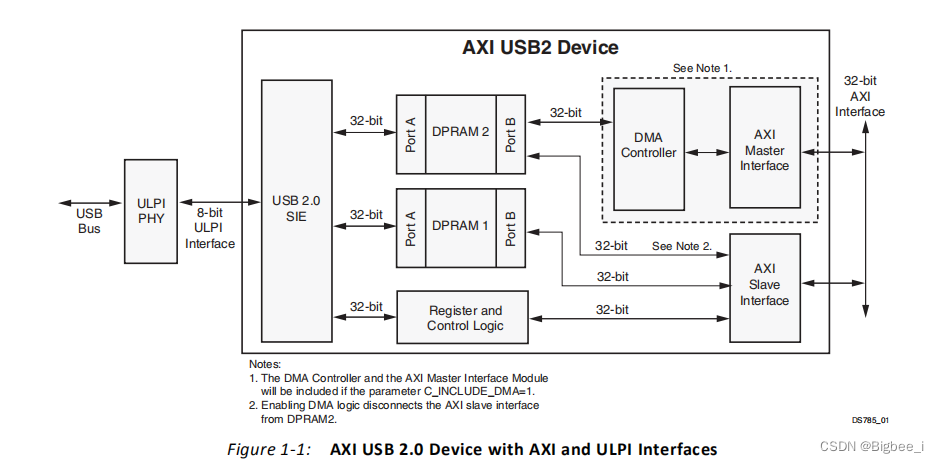

The AXI USB 2.0 Device的总体结构如下图:

3.2 The AXI USB 2.0 Device工作流程

发送数据:FPGA Logic to USB Device

- Host发送一个令牌token,包含以下内容

- OUT PID

- 设备的地址(Device address)

- 端点编号(Endpoint number)

- 数据(Data )

- Device当且仅当数据不存在 Bit Stuff, PID, and CRC 错误的时候回复handshake包

接收数据:USB Device to FPGA Logic

- Host发送一个令牌token,包含

- IN PID

- 设备的地址(Device address)

- 端点编号(Endpoint number)

- Host等待来自Device的数据

- Device检查令牌,没错误的话,Device回复Data

- Device等待来自Host的handshake

- Host回复handshake

3.3 分模块介绍

3.3.1 Register and Control Logic

包括32位寄存器,它为核心提供控制和状态信息,可以通过AXI Slave Interface访问。

3.3.2 USB 2.0 Serial Interface Engine (SIE)

USB 2.0串行接口引擎(SIE)充当如下作用:

- 在字节级处理USB流量的序列化和反序列化

- USB数据的复用和解复用

- 处理USB 2.0的状态转换,如挂起、恢复、USB重置和远程唤醒信号(以从挂起模式中唤醒主机)。

- 12个引脚的ULPI接口连接到PHY。

- 从USB到FPGA的数据从PHY接收,进行错误检查,并加载到DPRAM的适当区域。

- 从FPGA到USB数据从DPRAM加载,协议包装,然后当协议允许时,呈现给PHY,每次1Byte

3.3.3 Dual Port Block RAM (DPRAM)

功能:DPRAM是SIE和AXI接口之间的数据存储区域

特点:

- DPRAM的端口A由SIE使用,端口B由处理器/DMA控制器使用。这两个端口都是32位宽的

- 有两块DPRAM

DPRAM1 DPRAM2 Endpoint 端点0 FIFO和控制寄存器区域 Endpoint1-7的FIFO 64×8位 2K×8位 注:控制寄存器区域定义了内存是如何安排的,并报告每个FIFO缓冲区的状态(准备就绪、未准备就绪或计数)。

- 每个FIFO都是双缓冲的(乒乓),以帮助支持USB 2.0可能的高吞吐量。

- SIE将DPRAM视为FIFO

- 固件或硬件将DPRAM视为普通RAM,可以通过AXI Slave Interface访问

3.3.4 AXI Slave Interface

- 可以读写Register and Control Logic和DPRAM

- 支持DPRAM的字节、半字和字传输,但寄存器只支持字传输。

3.3.5 AXI Master Interface

- 在DMA模式下作为AXI主模式执行读取和写事务

- 在DMA模式下,根据DMA完成情况和DMA错误条件生成中断

3.3.6 Direct Memory Access (DMA) Controller

- 可选

- DMA控制器在DPRAM2和AXI接口上的外部存储器设备或外设之间提供简单的DMA服务。

- 核心中的DMA控制器只执行在DPRAM2和外部存储器之间的数据传输

注:DMA控制器将数据从源地址传输到目标地址,而无需处理器干预

3.3.7 ULPI PHY

USB PHY可以是任何与ULPI兼容的PHY,与USB直接相连,负责将字节数据转换为比特数据。

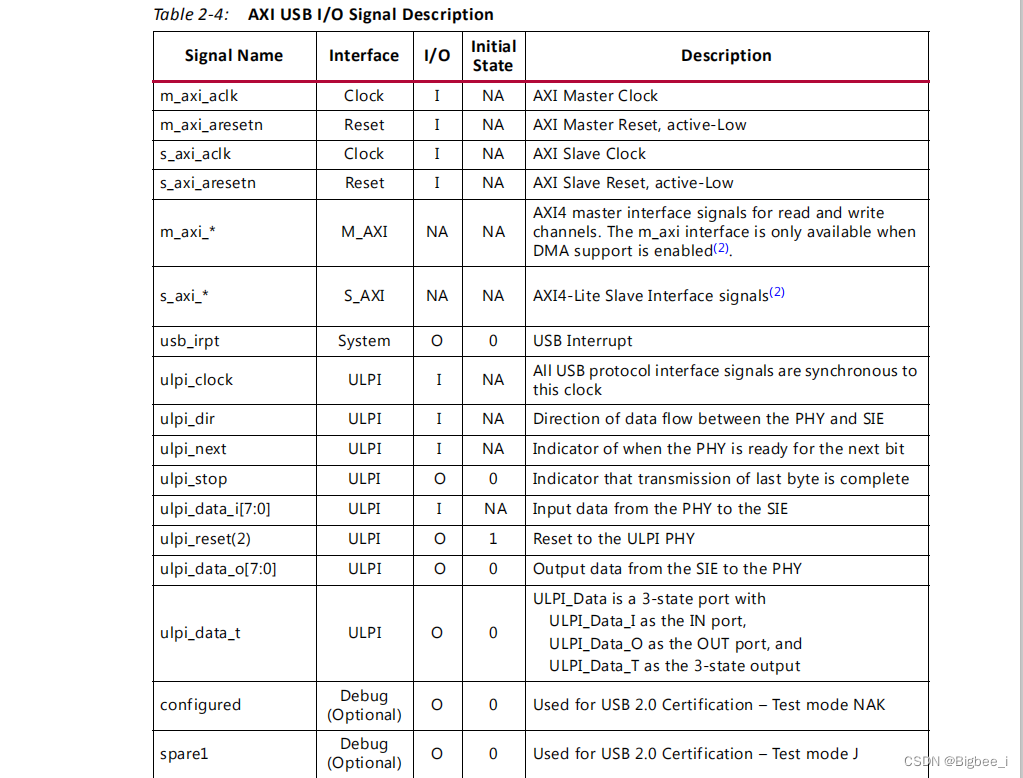

3.4 端口说明

说明:

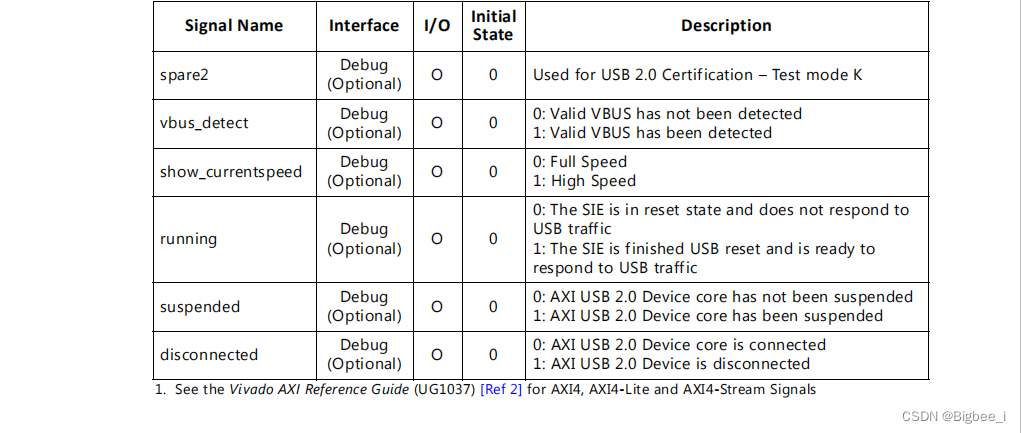

- Debug端口只有在勾选了 Include Debug Ports后才会显示出来,调试的时候可以加进去

- AXI Slave Interface和 AXI Master Interface都是标准的,省略了。

- m_axi_*z只有在使能了DMA才会出现

3.5 寄存器表

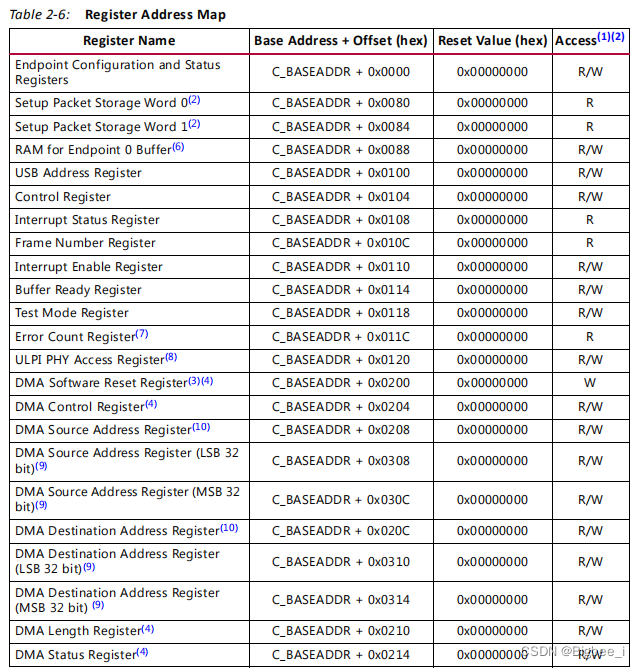

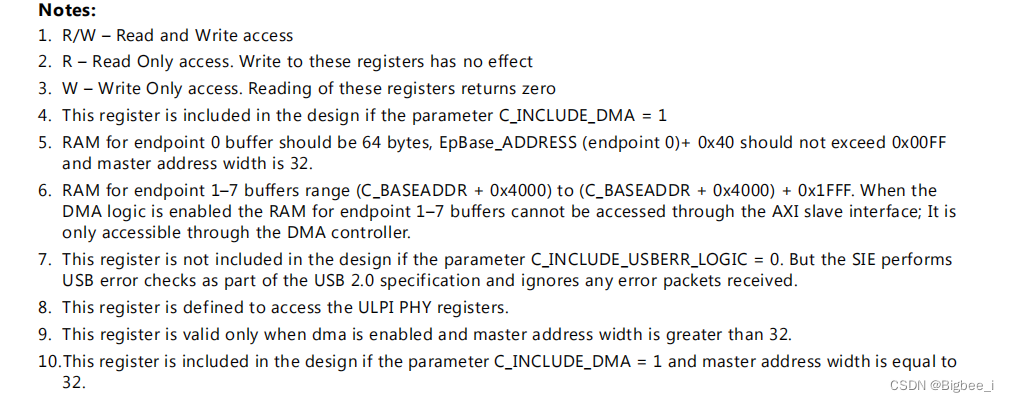

说明:

普通模式:

- 小端模式

- 第一列是寄存器名

- 第二列是Base Address + Offset 基地址是USB IP在整个系统中被分配的基地址。

- 第三列是复位后的默认值,所有的寄存器默认值都是0x0000_0000

- 第四列是读写权限,R表示有读权限,W表示有写权限

- endpoint 0 buffer 至少 64 bytes,偏移地址不能超过0xFF(0x88-0xFF)

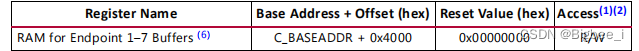

- RAM 中 endpoint 1–7 buffers 范围是 (C_BASEADDR + 0x4000) + 0x1FFF

表格:

DMA相关:

- DMA相关的寄存器只有在使能了DMA功能后才有效

- 启用DMA逻辑后,endpoint 1-7 RAM不能通过AXI Slave Interface 访问;它只能通过DMA控制器访问

蓝字标号的说明:

(内容在手册P15)

常用几个偏移地址:

- Endpoint configuration space (offset 0x0000)

- Setup packet storage space (offset 0x0080)

- RAM for Endpoint 0 buffer (offset 0x0088)

- register space for the USB registers (offset 0x0100)

- RAM for Endpoint 1 to 7 buffers (offset 0x4000)

手册后面还有每个寄存器位和功能的介绍,这里就不贴了,自己看手册理解的更加到位!

4. 后言

大家觉得有帮助的话,在收藏的同时麻烦点个赞!

后续我会写 IP的Example Design 解读和IP的上板测试,链接也会贴在文字的末尾。

欢迎大家的批评指正!

-

相关阅读:

opencv Ubuntu系统交叉编译

【重学C++】02 脱离指针陷阱:深入浅出 C++ 智能指针

【Java】一文认识IO操作流

自已定义一个Java异常——子定义异常,和异常遇到的面试题。

奶茶行业竞争加剧,奈雪全自动化制作,亲身示范如何“内卷”

低代码适用于哪些应用开发场景

酷开科技 | 酷开系统,带你寻觅最爱的影视之旅

redis(一)

SpringMVC入门宝典(四)SpringMVC注解(上)

error /var/lib/jenkins/workspace/*/node_modules/node-sass: Command failed.

- 原文地址:https://blog.csdn.net/liuhandd/article/details/126933696