-

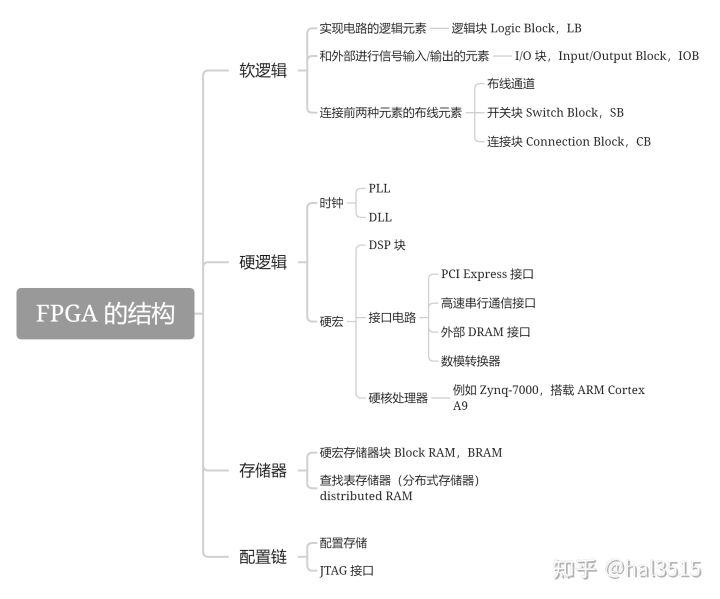

FPGA的基础结构

深入理解 FPGA 的基础结构 - 知乎 (zhihu.com)

原理和结构

FPGA的构成要素

- 逻辑要素(逻辑块, Logic Block, LB):用于实现逻辑电路。可编程逻辑的逻辑块的实现方式有乘积项、查找表、数据选择器(Multiplexer,MUX)等。由可以实现任意逻辑电路的可编程部分触发器(Flip-Flop,FF)等数据存储电路和数据选择器组成。

- 输入/输出要素:连接I/O引脚和内部布线要素的模型。包含(xxxx,xxx i don’t know)控制电路以及触发器等数据存储电路

- 布线要素:作为逻辑块间及逻辑块和I/O块间的连接部分,主要由布线通道、连接块(Connection Block,CB)和开关块(Switch Block, SB)构成

- 其他要素:逻辑块、I/O块、开关块和连接块由配置存储单元控制,用以实现任意逻辑函数和连接关系。配置存储单元前后连接形成配置链。类似配置链这种遍布整个器件的构造还有扫描路径、时钟网络等。此外FPGA上还有LSI测试电路、嵌入式处理器、乘法器等固定功能的硬核电路。

可编程技术

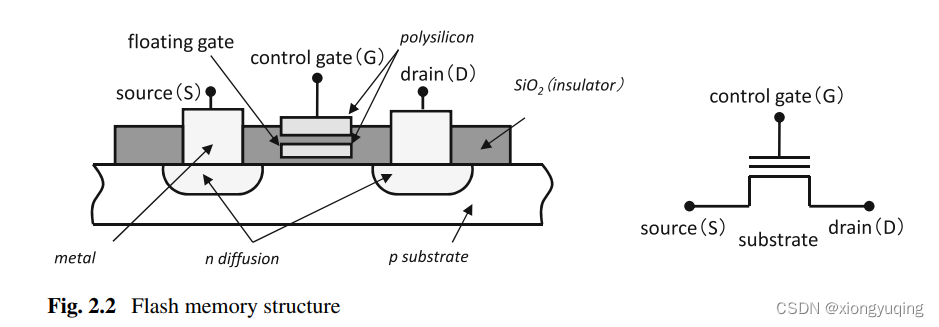

闪存

闪存是EEPROM的一种,采用MOS晶体管技术,绝缘层含有浮置栅极(floating gate),浮栅中的电荷没有逃脱路径,可以半永久的保存数据,属于非易失存储器。闪存分为NAND型和NOR型,NAND型写入需要高电压,NOR型写入需要大电流。NAND型闪存的构造:

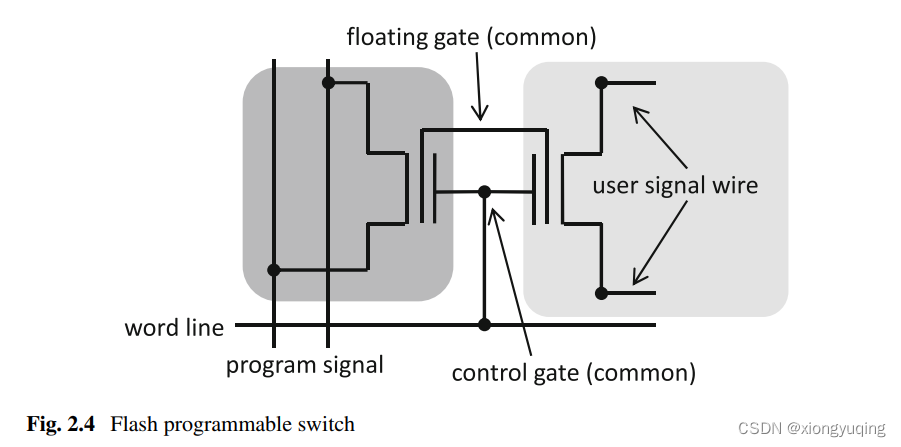

基于闪存的可编程开关:开关使用两个晶体管组成,左侧的小晶体管对闪存进行写入/擦除,右侧的大晶体管是FPGA中控制用户电路的开关,有着共同的控制栅极和浮栅。从编程开关注入电子,可以直接决定开关的状态。

反熔丝

反熔丝开关的初始状态为开放(断开)状态,与熔丝特性相反。

- 多晶硅型反熔丝PLICE,使用多晶硅和 n + n^+ n+ 扩散层作为导体,中间插入ONO电解质作为绝缘体,当加以10V左右电压,并约5mA电流通过时可以形成上下连通的通路。

- Metal-to-Metal型反熔丝,在上下两层金属布线层插入非晶硅(绝缘体)和钨插塞等导体。非晶硅层未编程为高阻抗的绝缘状态,通电编程后变为几乎和金属层连线同等程度的低阻抗状态。

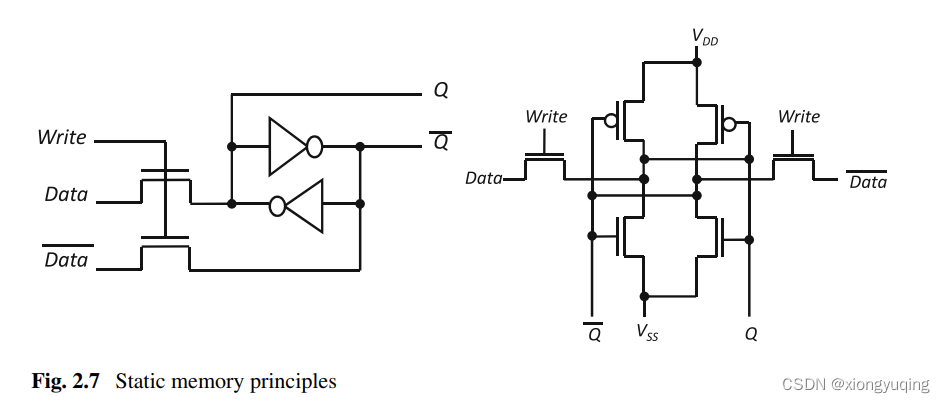

静态存储器

由两个CMOS反相器构成的触发器和两个传输晶体管(Pass-Transistor,PT)组成,利用触发器的双稳态(0和1)记录数据,数据的写入通过传输晶体管进行

FPGA的逻辑实现

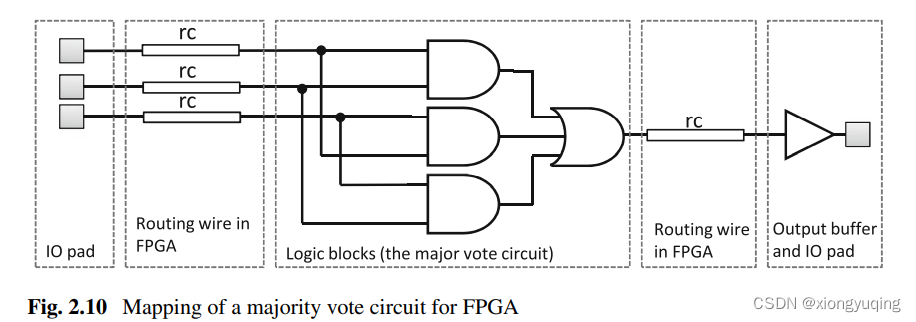

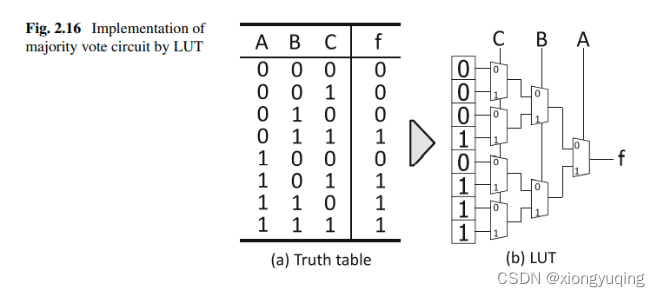

使用多数表决电路说明在FPGA上实现电路的原理

逻辑电路的输入信号从FPGA的I/O PAD进入,由内部布线进入逻辑块。逻辑块基于真值表决定输出,最终再经由布线路径输出到I/O PAD.

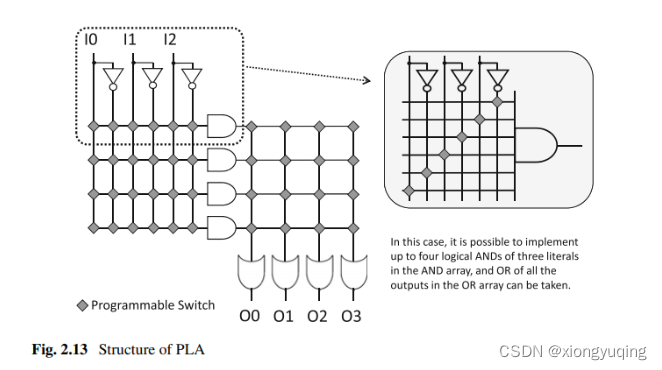

基于乘积项的逻辑实现

PLA(可编程逻辑器件)由一个AND阵列和一个OR阵列构成,两个阵列都是可编程的。使用乘积项实现电路需要计算逻辑函数的最小积之和。积之和形式的逻辑函数将“与项”和“或项”分开,分别使用AND阵列和OR阵列实现。

AND阵列内部,输入信号和各个AND门的输入通过可编程开关连接。OR阵列将AND门的输出和OR门的输入通过可编程开关连接。

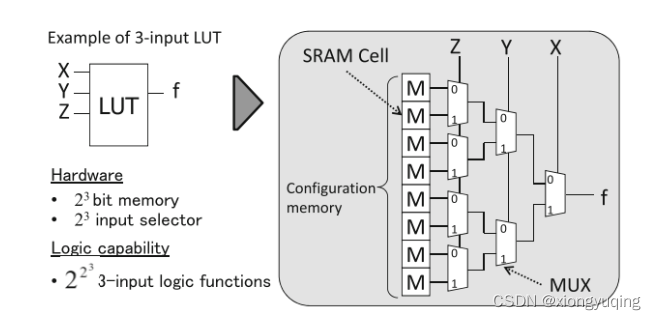

基于查找表的逻辑实现

查找表是1个字(word)只有1位的内存表,字数取决于地址的位数,FPGA上的查找表的存储单元大多使用SRAM实现。

k输入的查找表由 2 k 2^k 2k个SRAM单元和一个 2 k 2^k 2k 输入的数据选择器组成。查找表的输入是内存表的地址信号,输出是该地址所选字的1位数据。可以实现 2 2 k 2^{2^k} 22k 种逻辑函数。

使用查找表时,先一句查找表的输入数对真值表进行转换,然后就可以i将函数值(f栏)直接写入配置内存,当所要实现的逻辑函数输入数比查找表的输入数多时,可以联合多个查找表实现。

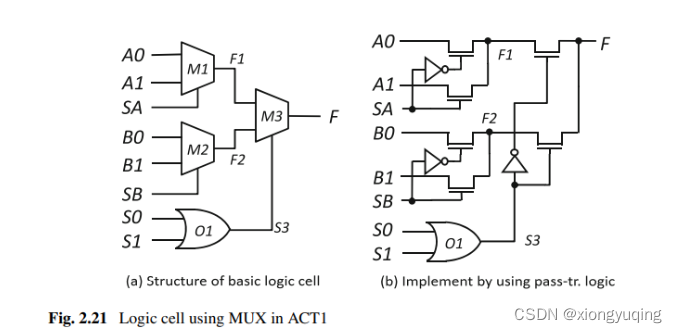

其他逻辑实现(数据选择器)

ACT1逻辑单元由3个2输入1输出的数据选择器(2-1 MUX)和一个逻辑或门组成,可以实现多种8输入1输出以内的逻辑电路。还可以实现四输入以内的NAND,AND,OR和NOR等,也可以实现输入反向,复合门电路,锁存器、触发器。

MUX不能实现其输入数量之内的所有逻辑电路,可以通过组合使用实现逻辑电路得到用户所需的电路。

FPGA的结构

FPGA由三大要素构成,实现逻辑电路需求的可编程逻辑要素、提供外部接口的可编程输入/输出要素,连接前两种要素的可编程布线要素。逻辑块和乘法器块都是用来实现逻辑函数的运算电路,存储器快提供存储功能。乘法器块和存储器块等具有专门用途的电路称为“硬逻辑”,在逻辑块中利用查找表和数据选择器实现的任意逻辑函数称为“软逻辑”。对逻辑块结构的称呼,Xilinx公司称其为CLB(Configurable Logic Block),Altera公司称其为LAB(Logic Array Block)

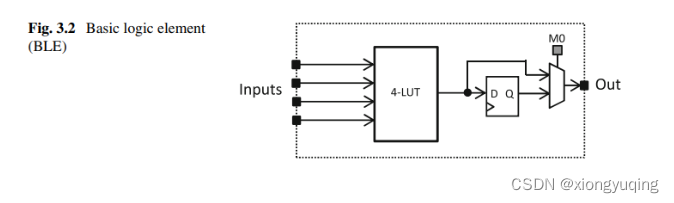

逻辑块的结构

大部分逻辑块的基本要素都包含基本逻辑单元(BLE, Basic Logic Element)。BLE由实现组合电路的查找表、实现时序电路的触发器以及数据选择器构成。数据选择器在存储单元M0的控制下决定直接输出查找表的值还是输出FF中存储的值。

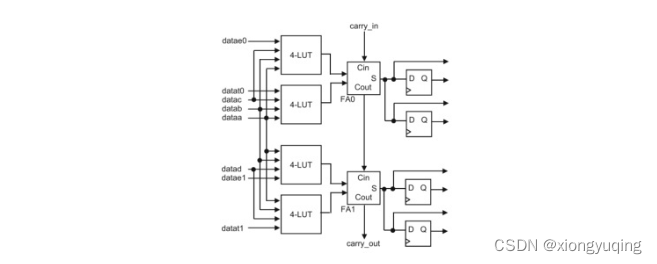

专用进位逻辑

为了提高算术运算电路的性能,商用FPGA的逻辑块还含有专用的进位电路,虽然只用查找表也可以实现算术运算,但采用专用进位逻辑可以获得更高的集成度和运行速度。

上图中的两个全加器(Full Adder, FA)为专用进位逻辑。FA0的进位输入(carry_in)连接到相邻逻辑块的进位输出(carry_out)。这条路径称为高速进位链,为多位算术运算提供高速的进位信号传输。

上图为算术运算模式,各加法器将两个4-LUT的输出相加。此外还有共享运算模式,在查找表中实现求和功能,可以一次完成3输入2位的加法运算。

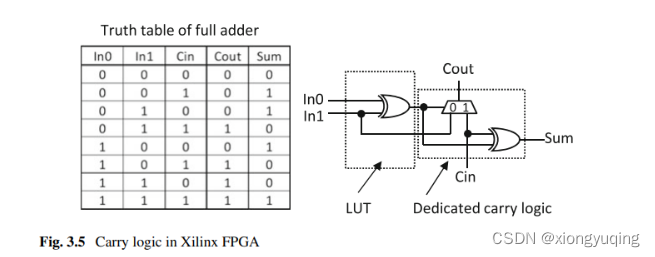

Xilinx公司FPGA的专用进位逻辑没有设计专用的全加器电路,而是使用查找表和进位生成电路的组合实现加法。全加器的加法运算(Sum)用两个2输入的EXOR实现,进位输出(Cout)使用1个EXOR和1个MUX实现,进位信号Cin也通过进位链和相邻的逻辑模块相连,以此扩展实现多位加法器。

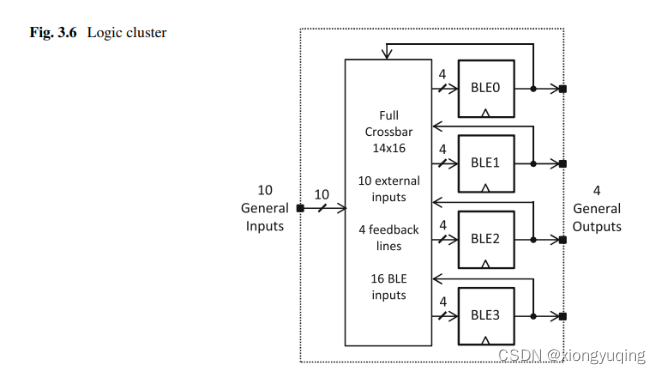

逻辑簇

逻辑簇(logic cluster)结构提高了逻辑块的功能性,但不增加查找表的输入数,由多个BLE群组化形成的逻辑块结构。

全交叉开关矩阵(full crossbar)模块也称局部连接块(local connection block)或局部互联(local interconnect),主要用来连接逻辑块中的BLE。

逻辑簇结构的特征:

- 逻辑簇内的局部布线采用硬连线,比外部的通用布线速度更快

- 逻辑簇内局部布线的负载电容笔外部通用布线小很多,对FPGA的动态功耗的消减有效果

- 逻辑簇内的BLE可以共享输入信号,有助于减少局部连接块的开关数量

含有多BLE的逻辑块最大优势就是在增加逻辑块功能性的同时不会大幅度影响FPGA的整体面积。查找表的面积会随着输入k的增大呈指数级增长,而增加逻辑簇中BLE的数量N,逻辑块的面积值按二次函数增长,逻辑块输入数量I的经验公式

I = k 2 ( N + 1 ) I=\frac{k}{2}(N+1) I=2k(N+1)

如果每个BLE的输入都是独立的,逻辑块总共需要 I = N × k I=N\times k I=N×k 个输入。通过输入信号的共享,可以有效缩减逻辑块的面积。增加N可以增强逻辑块的功能性,提高速度,也会导致局部互联部分的延迟增加。文献中总结出的面积延迟乘积性能最优的结构参数为:$N=3 \sim 10,k=4 \sim 6 $自适应查找表

将较多输入的查找表分解使用的逻辑单元称为可拆分查找表(fracturable LUT)或自适应查找表(adaptive LUT)。用过分解来实现多个逻辑,提升了资源利用的效率。

布线线段

根据各个逻辑块,I/O块之间的连接方式,FPGA的布线结构类型主要分为:完全连接型、一次元阵列型、二次元阵列型(岛型)和层次型。

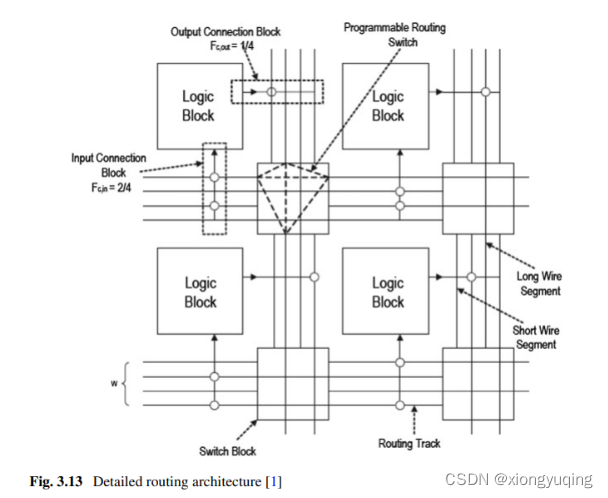

FPGA的布线架构分为全局布线(global routing)和详细布线(detail routing)两部分。全局布线主要解决逻辑块的连接、布线通道的宽度(连线数量)等高层次问题。详细布线架构决定具体的连接方式,例如逻辑块和布线通道间的开关布局。

详细布线架构

布线通道中连线的数量定义为W,包含多种长度类型的布线线段。连接逻辑块和布线通道的连接块(CB)有输入和输出两种,输入连接块和输出连接块的自由度分别由 F c , i n F_{c,in} Fc,in 和 F c , o u t F_{c,out} Fc,out 定义。纵向和横向布线通道的交叉处由开关块(SB),开关块的自由度由 F S F_S FS 定义。

上图中W = 4, Fcin = 2/4 Fcout=1/4,Fs=3

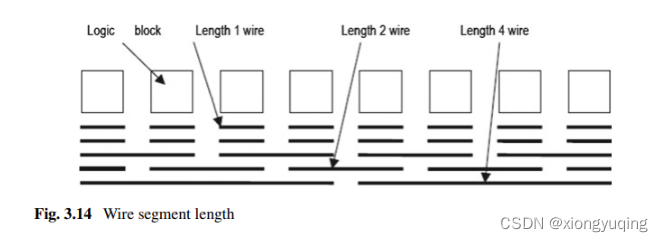

布线线段长度

布线线段长度指的是连线所跨越的逻辑块的数量,图中有长度分别为1(单倍线),2(双倍线),4(四倍线)的连线线段

布线开关的结构

很多FPGA结合使用传输晶体管和三台缓冲器来实现布线开关。

较短路径使用传输晶体管可以减少开关数量,但传输晶体管会影响信号质量,使用多级传输晶体管需要插入中继器(缓冲器)

长距离连线适合三态缓冲器。

文献提到传输晶体管和三态缓冲器各占一半性能最好。

传输信号的连线分为两种:

- 双向连线:减少布线通过中连线的数量,但有一个方向的开关会闲置,并会增加连线电容影响延迟

- 单项连线:布线数量是双向连线的两倍,开关不会闲置,连线电容较小。

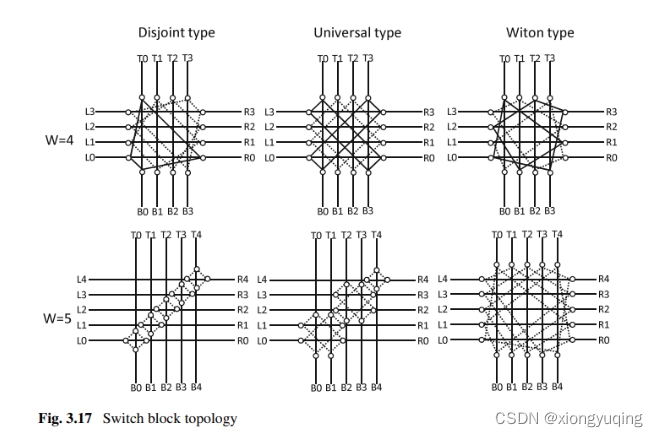

开关块

开关块(SB)位于横向和纵向布线通道的交叉处,通过可编程开关控制布线路径。具有代表性的开关块拓扑:

不相交(Disjoint)型、通用(Universal)型和威尔顿(wilton)型。

- 不相交型:相同序号的连线进行互联

- 通用型:成对的连线在开关块内互联

- 威尔顿型:保证一条连线和序号最远(W-1)的连线相连。

连接块

连接块也由可编程开关构成,用于连接布线通道和逻辑块的输入/输出。布线通道的连线非常多,使用全交叉开关矩阵实现面积非常大,而是使用节省掉一些开关的稀疏开关矩阵。

I/O块

输入输出要素由专用的I/O块(Input/Output Block,IOB)构成,负责器件的I/O引脚和逻辑块之间的接口部分。

I/O 块放置在芯片的外围。FPGA 的 I/O 口除了固定用途的电源、时钟等专用引脚,还有用户可以配置的用户 I/O。I/O 块具有输入/输出缓冲、输出驱动、信号方向控制、高阻抗控制等功能,可以使输入/输出信号能在 FPGA 阵列内的逻辑块和 I/O 块间按指定方式传输。I/O 块里还有触发器,可以锁存输入/输出信号。很多 FPGA 还具有应对高速通信的差分信号(Low Voltage Difference Signaling,LVDS)等功能。

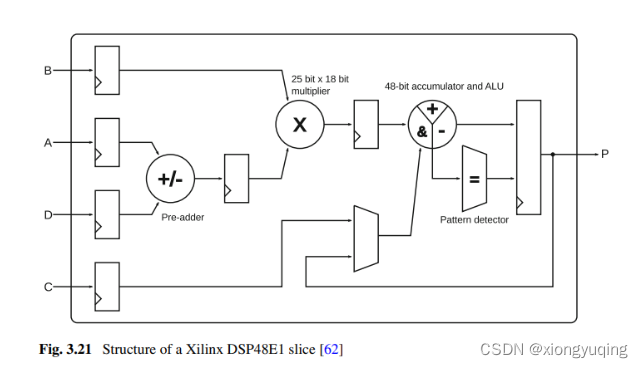

DSP块

FPGA在进行大量乘法运算时,由于其输入信号较多,基于逻辑块的查找表需要大量逻辑块相互连接,因此布线延迟就会增大,难以提高运算性能。为了应对数字信号处理领域中复杂且多样的运算,DSP(Digital Signal Processing)块应运而生。

在信号处理领域,下面这种将乘积结果累加的MACC(Multiply-Accumulate)运算非常多见:

Y ← A × B + Y Y\larr A\times B + Y Y←A×B+Y

结合乘法器和48位累加器,再通过将最后一级的寄存器输出反馈位操作数,来独立完成MACC运算。

运算粒度的灵活性实现:

- 级联路径:直接连接相连2个slice实现多位运算,不消耗通用逻辑资源

- SIMD(单指令多数据流)运算:48位累加器实现4个独立12位加法或2个24位加法

硬宏

将通用接口电路等硬件模块抽象出来,作为专用硬件嵌入FPGA芯片,这些专用硬件电路一般称为硬宏(hard macro)。

硬件乘法器和DSP块属于硬宏,此外FPGA上通常还有PCI Express接口,高速串行通信接口,外部DRAM接口,模拟数字转换器等多种硬宏。

在FPGA上以用户电路的方式实现处理器被称为软核处理器,优点是自由度高可定制。作为硬宏嵌入的处理器称为硬核处理器。

嵌入式存储器

可用作存储要素的只有逻辑块中的触发器,因此很难在芯片上保存大量数据,要实现这样的需求需要在FPGA上连接外部存储器,而FPGA和外部存储器间的带宽会成为系统的瓶颈,限制整体性能,于是开始集成高效的片上存储器。

这种FPGA内部的存储器统称位嵌入式存储器。

- 存储器块硬宏:以硬宏的形式正在架构中嵌入存储器块

- 查找表存储器:当逻辑块实现组合逻辑电路时,查找表中存储的真值表就可以用作小规模的存储器

配置链

将电路编程到FPGA上的过程叫做配置,向FPGA写入的电路信息叫做配置数据。配置数据中包含FPGA上实现电路的所有信息。

根据所使用的存储单元不同,FPAG的配置存储器技术分为三类:

- SRAM型:没有重写次数闲置,SRAM属于易失性存储器,断电后FPGA上的电路信息会丢失。

- 闪存型:非易失性存储器,没有写入次数的限制,写入速度不SRAM慢。

- 反熔丝型:非易失性,配置一次后不能再改变

JTAG(Joint Test Action Group)为边界扫描测试IEEE 1149.1的总称。很多商用FPGA利用这种边界扫描框架实现配置存储器机制。

使用JTAG接口进行配置时,先将配置数据一位一位序列化,再通过边界扫描用的移位寄存器写入FPGA。这条移位寄存器的路径就称为配置链(configuration chain)

PLL 和DLL

在FPGA上的各种电路,其关键路径不同,时钟频率也各不同,当FPGA与外部系统通信也需要生成和外部输入的时钟没有相位差的时钟信号,对应外部接口也需要使用多个不同频率相位的时钟信号。因此需要FPGA具有生成各种频率的时钟信号的功能,可以基于外部输入的基准时钟,通过可编程PLL机制来生成各种时钟信号。

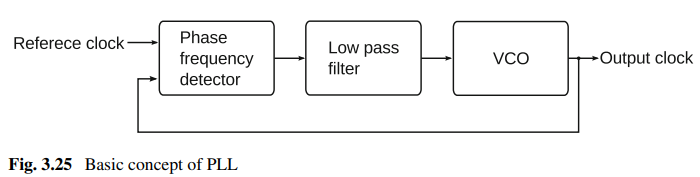

PLL(PhaseLocked Loop)

生成时钟信号的核心部分时压控振荡器(Voltage-Controlled Oscillator,VCO),鉴相器可以比较外部输入的基准时钟和 VCO 自身输出时钟间的相位差。如果两个时钟一致则维持 VCO 电压;如果不一致则需要通过控制电路对 VCO 电压进行调整,最终让输出时钟和基准时钟达到一致。

低通滤波器去掉高频成分再输入VCO,可以更稳定地生成和外部输入时钟相同频率、相同相位的时钟信号。

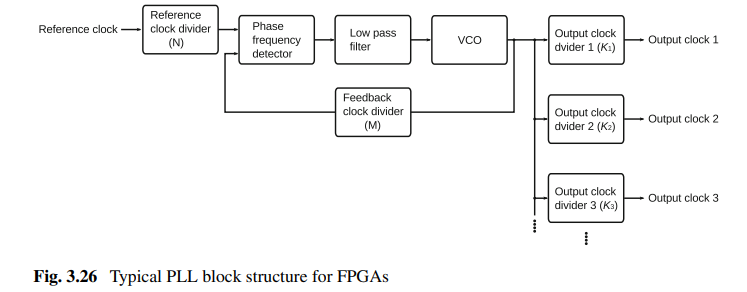

上面的PLL结构只能和外部输入的基准时钟相同的频率震荡,为了产生各种频率的时钟信号,常见的需要再添加几个可编程分频器的PLL块。

基准时钟再输入鉴相器前通过分频器,其分频比为 N N N ,反馈VCO的输出时钟到鉴相器的路径也追加了分频器,其分频比为 M M M 。基准时钟的频率为 F r e f F_{ref} Fref ,VCO的振荡频率为 F v c o F_{vco} Fvco ,他们的关系为:

F v c o = M N F r e f F_{vco} = \cfrac{M}{N}F_{ref} Fvco=NMFref

M M M , N N N 的值时可自由设定的,但也有限制。VCO的后端也有多个独立的分频器,可以再次分频。第 i i i 个时钟的频率为 F i F_i Fi ,对应的输出分频器的分频比为 K K K ,那么基准频率和输出频率的关系为:

F i = 1 K F v c o = M K i ⋅ N F r e f F_i = \cfrac{1}{K}F_{vco} = \cfrac{M}{K_i \sdot N}F_{ref} Fi=K1Fvco=Ki⋅NMFref

PLL是一个以外部输入基准信号为目标,以VCO振荡频率为控制对象的反馈控制系统。在启动、复位、基准时钟大幅变动时,反馈系统需要一定的时间让VCO振荡稳定下来。为了预防在输出时钟稳定前,发生不可预测的动作,需要对基准和反馈信号进行监测。当VCO输出稳定并和基准时钟吻合时,称PLL为锁定状态,常常设置1位输出信号来表示。

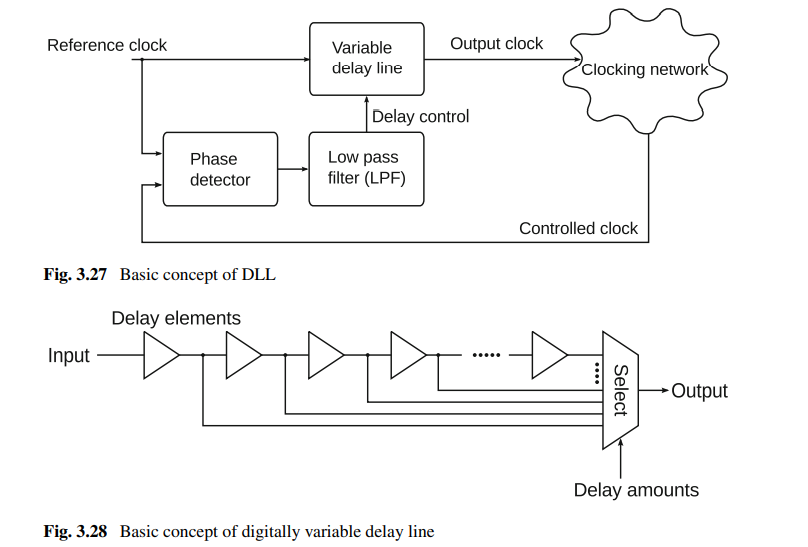

DLL(DelayLocked Loop)

DLL与PLL不同之处在于没有使用VCO,通过可变延迟线来控制时钟信号延迟量。主要采用预设多个延迟单元,再通过选择器选择所需延迟量的路径。

DLL也可以实现受控时钟和输入时钟的相位跟踪,通过调整基准时钟到受控时钟的延迟来实现。DLL 的作用是消除分配时钟与参考时钟之间存在相位差。工作原理是在参考时钟(Reference Clock)和反馈时钟(Controlled Clock)之间插入延迟,直到两个时钟的上升边缘对齐,使两个时钟错位360度 (意味着它们是同步的)。

-

相关阅读:

O2OA(翱途)开发平台 V8.1正式发布

docker-compose.yml(spark)

嵌入式基础_STM32F103C8T6从零开始建立一个项目(库函数)

Python把word转为html(去水印版)

Excel 通过条件格式自动添加边框

【实践成果】Splunk 9.0 Configuration Change Tracking

学习6大步

【Node.js】第九章 数据库

如何在Dev-c++中向项目初始源文件插入代码?

hive和hbase的使用问题

- 原文地址:https://blog.csdn.net/qq_45364953/article/details/126820278