亲身经历华为海思面试,专业问题分享解析

回想去年,我参加过的一场面试。当时,我投递的职位是海思数字IC电路设计岗位。不知道为什么,这个岗位投递的人超多。竞争极其残酷。在面试过程中,问了很多问题,先问基础数字电路设计题,再根据简历中的项目问问题。其中一个问题,是关于多周期时钟,在这里我做下详细的记录和解释。

Section1: 多周期基础题,不会的基本…

面试官首先问多周期是什么意思?让我给他做个详细解释。于是我给他balabala讲了下面的知识点,当然现场没那么详细,这里我详细给大家做下解释。

一个多时钟周期的经典例子就是来自DC workshop中的乘法器,图1中时钟CLK的周期为10ns,根据设计规格加法器的延迟约为6个时钟周期。

图1

根据需求,需要加入的setuptime check设计约束如下:

Create_clock–period 10 [get_ports CLK]

Set_multicycle_path–setup 6 –to [get_pins C_reg[*]/D]

图2

加了上面的约束后,DC/PT 将仅仅在第6个上升沿,即第60ns做建立时间的分析,这时,加法器的最大延迟为:

Setup time check 时序如图2,那么,DC怎么做保持时间分析呢?其实DC默认是在setup time check的前一个周期,即第50ns做保持时间分析,这时要求加法器的最小延迟:

其实,这种要求明显是不合理的,也会增加电路的复杂度。

Hold time check 点如图3中绿色箭头所标注位置

图3

为了正确表述电路的功能,我们需要对保持时间做调整,应在0ns时刻做保持时间的检查。正确的约束如下:

Set_multicycle_path –setup 6 –to [get_pins C_reg[*]/D]

Set_multicycle_path –hold 5 –to [get_pins C_reg[*]/D]

图4

保持时间分析提早了5个周期。相应的电路中的加法器允许的延迟也变成为:

相应的电路可以修改成图5的结构进行实现。

图5

Section 2: 多周期进阶,体现水平的时候到了

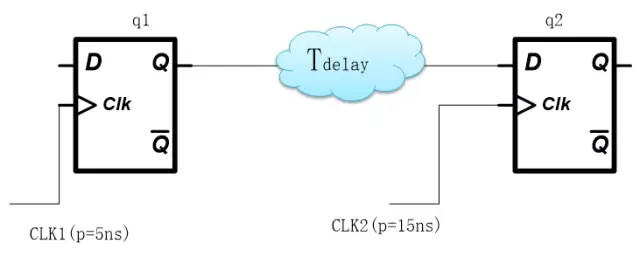

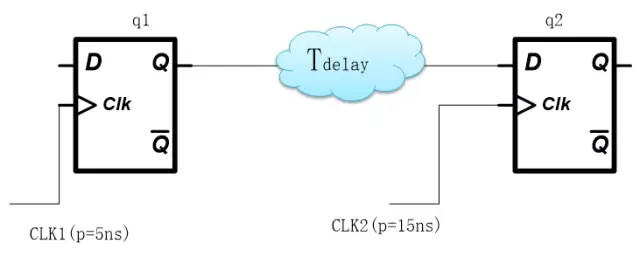

面试官觉得我回答的可以,于是深入继续问,如果上面的电路2个寄存器的CLK不是同频,但是,是同步,又应该怎么考虑?如图6的电路。就是launch CLK和capture CLK 是不一样的CLK,且满足下式:

图6

当时,我就不假思索的写下了下面的SDC,但是答案却是错误的。(根据他的耐心引导,最终还是没搞定)

set_multicycle_path-setup 3 -from clk1 -to clk2

set_multicycle_path -hold 2 -from clk1 -to clk2

解释面试官的题目之前,我们先看一下set_multicycle_path这个SDC命令的其他选项的意思

set_multicycle_path

[-setup | -hold]

[-start | -end]

[-from from_list]

[-to to_list]

[-through through_list]

-Setup和-hold用于说明多周期路径是用在建立时间检查还是用在保持时间检查。

-Start和-end用于说明多周期路径依赖于start clock还是依赖于end clock。

注意-start和-end。

在设置multicycle_path的过程中,一定要注意是start clock 是多周期,还是end clock 多周期。这关系到时序分析的正确性。默认情况下,set_multicycle_path对建立时间的分析是设置end clock为多周期,对保持时间分析师设置start clock为多周期。也就是说,上面的SDC等价于

那么根据这个SDC,DC的建立时间和保持时间check点就变成下面图7所示。可以看到保持时间检查是start clk的多周期就是CLK1。建立时间检查是end clk的多周期就是clk2。但是,保持时间检查明显错了。

图7

为了获取正确的检查点,更正SDC,获得建立时间和保持时间检查点变成图8所示:

set_multicycle_path -setup 3 -from clk1 -toclk2 -end

set_multicycle_path -hold 2 -from clk1 -to clk2–end

我相信将来大家可能还会碰到图9的面试题,区别在于CLK1是慢时钟,CLK2是快时钟。且满足下式:

图9

如果SDC写出下面的形式,建立时间和保持时间检查点会奇葩的变成图10所示。

set_multicycle_path -setup 3 -from clk1 -to clk2

set_multicycle_path -hold 2 -from clk1 -to clk2

为了获得正确的timing检查点,修正SDC如下,timing check点变成图11所示:

set_multicycle_path -setup 3 -from clk1 -to clk2 -start

set_multicycle_path -hold 2 -from clk1 -to clk2

总结

面试官问问题,总是由浅入深,慢慢引导我们。并根据回答情况就可以判断我们学习掌握的是否够深入。从而录取优秀的学生。另外面试官也会考察一个学生知识掌握的广度。最后,对于简历中写的内容务必都要掌握好,不会的东西,不要往简历里塞。最后预祝大家10月份找工作马到成功。