-

Cortex-M3概览

Cortex-M3概览

简介

Cortex‐M3 是一个 32 位处理器内核。内部的数据路径是 32 位的,寄存器是 32 位的,存储器接口也是 32 位的。

CM3 采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访问并行不悖。

但是另一方面,指令总线和数据总线共享同一个存储器空间(一个统一的存储器系统)寄存器组

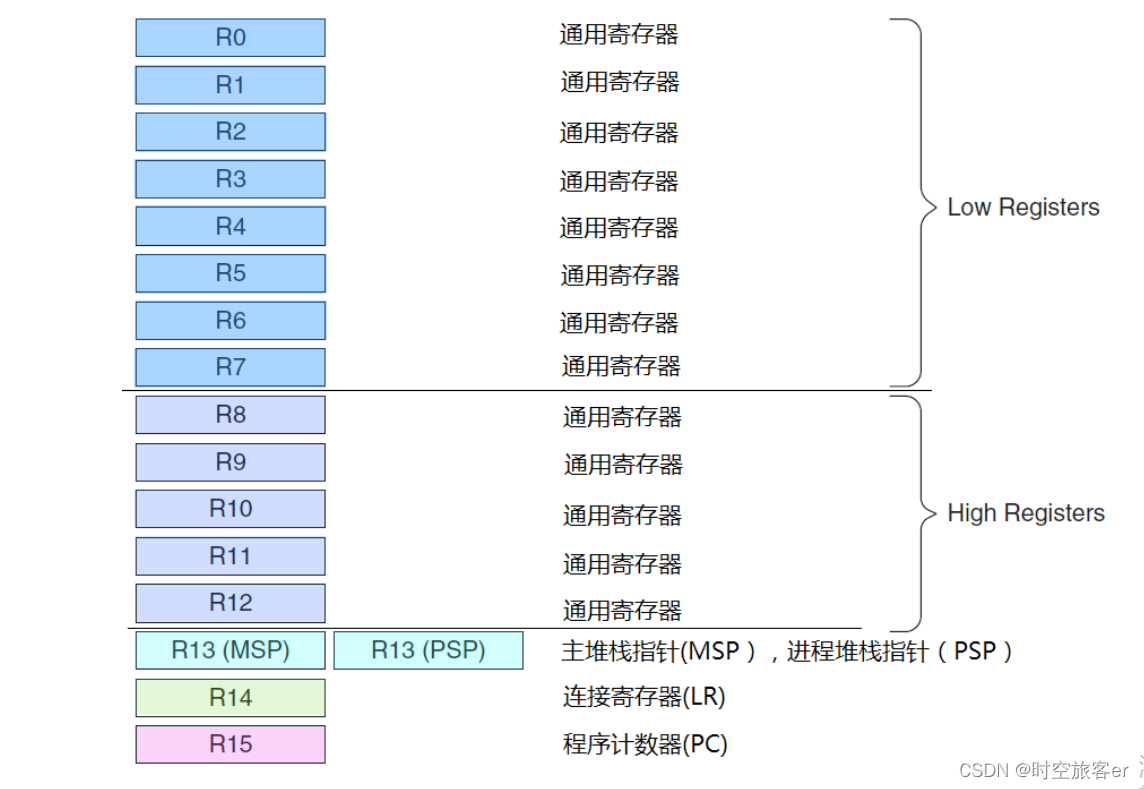

Cortex‐M3 处理器拥有 R0‐R15 的寄存器组。其中 R13 作为堆栈指针 SP。SP 有两个,但在同一时刻只能有一个可以看到,这也就是所谓的“banked”寄存器。

R0-R12:通用寄存器

R0‐R12 都是 32 位通用寄存器,用于数据操作。但是注意:绝大多数 16 位 Thumb 指令只能访问 R0‐R7,而 32 位 Thumb‐2 指令可以访问所有寄存器。

Banked R13: 两个堆栈指针

Cortex‐M3 拥有两个堆栈指针,然而它们是 banked,因此任一时刻只能使用其中的一个。

- 主堆栈指针(MSP):复位后缺省使用的堆栈指针,用于操作系统内核以及异常处理例程(包括中断服务例程)

- 进程堆栈指针(PSP):由用户的应用程序代码使用。

堆栈指针的最低两位永远是 0,这意味着堆栈总是 4 字节对齐的。

R14:连接寄存器

当呼叫一个子程序时,由 R14 存储返回地址。

ARM 为了减少访问内存的次数,把返回地址直接存储在寄存器中。这样足以使很多只有 1 级子程序调用的代码无需访问内存(堆栈内存),从而提高了子程序调用的效率。如果多于 1 级,则需要把前一级的 R14 值压到堆栈里。R15:程序计数寄存器

指向当前的程序地址。如果修改它的值,就能改变程序的执行流。

特殊功能寄存器

Cortex‐M3 还在内核水平上搭载了若干特殊功能寄存器,包括

- 程序状态字寄存器组(PSRs)

- 中断屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI)

- 控制寄存器(CONTROL)

操作模式和特权极别

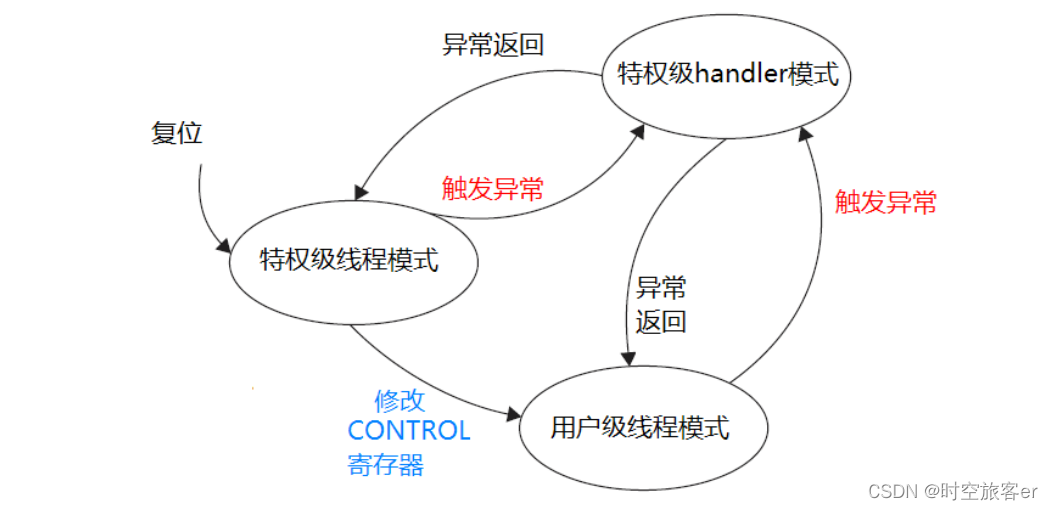

Cortex‐M3支持两种操作模式:handler mode、线程模式。

用于区分普通应用程序代码和异常服务例程的带队吗(包括中断服务例程)

Cortex-M3的另一个侧面是特权的分级:特权级、用户级。提供一种存储器访问的保护机制。在 CM3 运行主应用程序时(线程模式),既可以使用特权级,也可以使用用户级;但是异常服务例程必须在特权级下执行。复位后,处理器默认进入线程模式,特权极访问。在特权级下,程序可以访问所有范围的存储器(如果有 MPU,还要在 MPU 规定的禁地之外),并且可以执行所有指令。

在特权级下的程序可以为所欲为,可以切换到用户级。一旦进入用户级,再想回来就得走“法律程序”了——用户级的程序不能简简单单地试图改写 CONTROL 寄存器就回到特权级,它必须先“申诉”:执行一条系统调用指令(SVC)。这会触发 SVC 异常,然后由异常服务例程(通常是操作系统的一部分)接管,如果批准了进入,则异常服务例程修改 CONTROL 寄存器,才能在用户级的线程模式下重新进入特权级。

指令集

Cortex‐M3 只使用 Thumb‐2 指令集。这是个了不起的突破,因为它允许 32 位指令和 16 位指令水乳交融,代码密度与处理性能两手抓,两手都硬。而且虽然它很强大,却依然易于使用。

调试支持

Cortex‐M3 在内核水平上搭载了若干种调试相关的特性。最主要的就是程序执行控制,包括停机(halting)、单步执行(stepping)、指令断点、数据观察点、寄存器和存储器访问、性能速写(profiling)以及各种跟踪机制。

-

相关阅读:

System design summary

.NET 6 基于IDistributedCache实现Redis与MemoryCache的缓存帮助类

Redis 内存满了怎么办?这样设置才正确!

配置Jedis连接池

mysql之搭建MHA架构实现高可用

JavaWeb

一文解析推特上最常见的加密骗局

【计算机网络】物理层

Java 监控直播流rtsp协议转rtmp、hls、httpflv协议返回浏览器

基于java+springboot+mybatis+vue+elementui的农产品销售商城网站

- 原文地址:https://blog.csdn.net/pengxianchen/article/details/126890553