-

【操作系统】内存管理(四)—— 内存的分配与回收(2)

【操作系统】内存管理(四)—— 内存的分配与回收(2)

前言:操作系统内存的分配分为

连续分配管理方式和非连续分配管理方式,本章主要介绍非连续分配管理方式。内存连续分配管理的介绍可见:

https://blog.csdn.net/weixin_43848614/article/details/126803818一、非连续分配管理方式

连续分配:为用户进程分配的必须是一个连续的内存空间。

非连续分配:为用户进程分配的可以是一些分散的内存空间。- 基本分页存储管理

- 基本分段存储管理

- 段页式存储管理

(一)、基本分页存储管理

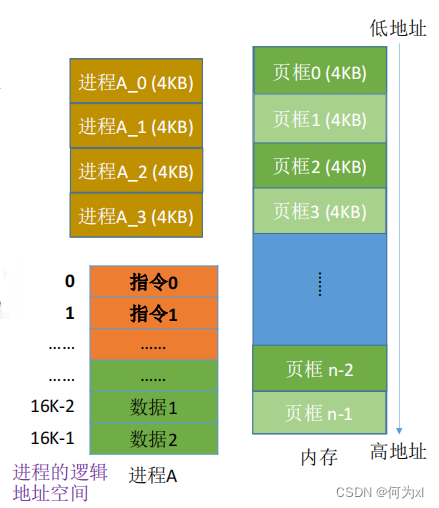

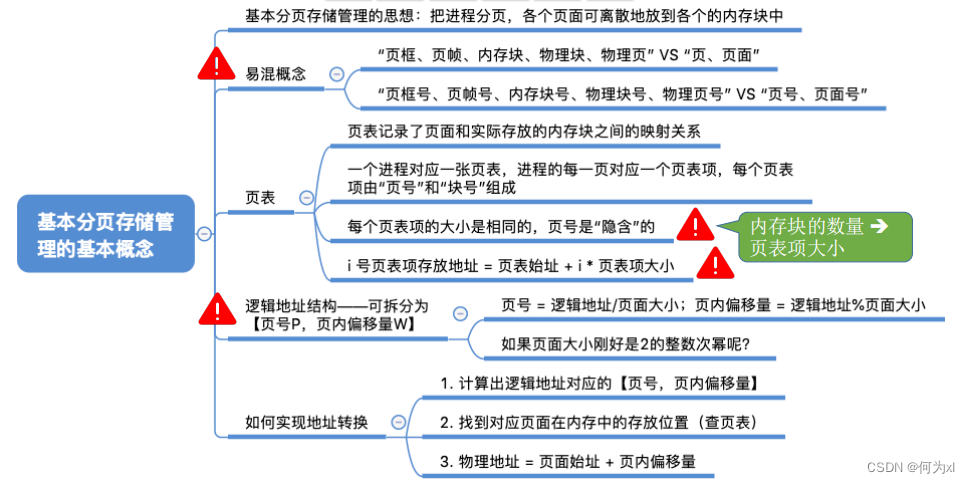

1. 分页

将内存空间分为一个个大小相等的分区(比如:每个4KB),每个分区就是一个“页框”(页框=页帧=内存块=物理块=物理页面)。每个页框有一个编号,即“页框号”(页框号=页帧号=内存块号=物理块号=物理页号),页框号从0开始。

将进程的逻辑地址空间也分为与页框大小相等的一个个部分,每个部分称为一个“页”或“页面” 。每个页面也有一个编号,

即“页号”,页号也是从0开始。注:进程的最后一个页面可能没有一个页框那么大。也就是

说,分页存储有可能产生内部碎片,因此页框不能太大,否则

可能产生过大的内部碎片造成浪费页框=页帧=内存块=物理块=物理页面

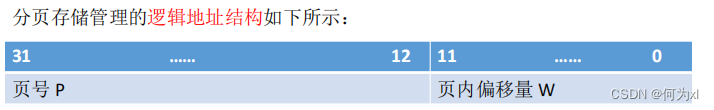

地址结构包含两个部分:前一部分为页号,后一部分为页内偏移量 W。在上图所示的例子中,地址长度为 32 位,其中 0~11位 为 “页内偏移量”,或称 “页内地址”;12~31 位为 “ 页号 ”。

如果有 K 位表示“页内偏移量”,则说明该系统中一个页面的大小是 2 K 2^K 2K个内存单元;

如果有 M 位表示“页号”,则说明在该系统中,一个进程最多允许有 2 M 2^M 2M 个页面。

操作系统以页框为单位为各个进程分配内存空间。进程的每个页面分别放入一个页框中。也就是说,进程的页面与内存的页框有一一对应的关系。

各个页面不必连续存放,可以放到不相邻的各个页框中。

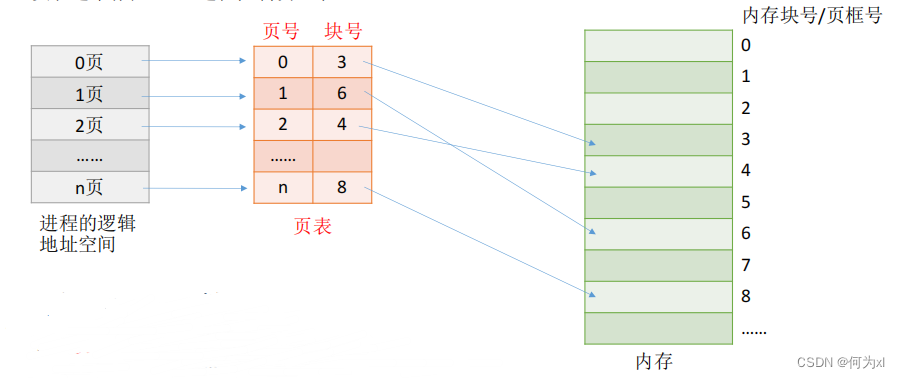

2. 重要的数据结构 —— 页表

为了能知道进程的每个页面在内存中存放的位置,操作系统要为每个进程建立一张页表。【注:页表通常存在PCB(进程控制块)中】

1. 一个进程对应一张页表

2. 进程的每个页面对应一个页表项

3. 每个页表项由 “页号” 和 “块号” 组成

4. 页表记录进程页面和实际存放的内存块之间的映射关系

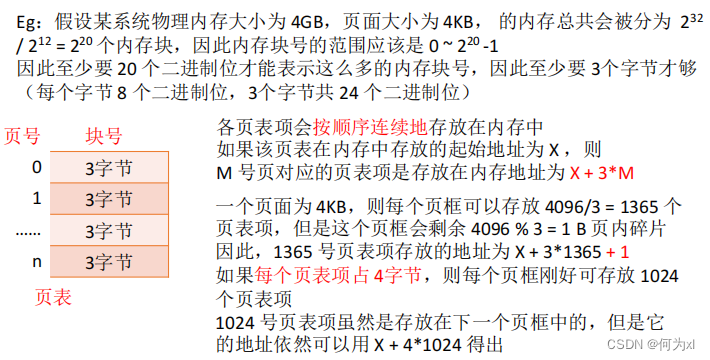

5. 每个页表项的长度是相同的,页号是“隐含”的。Eg:假设某系统物理内存大小为 4GB,页面大小为 4KB,则

每个页表项至少应该为多少字节?

内存块大小=页面大小=4KB= 212 B

4GB 的内存总共会被分为 232 / 212 = 220个内存块

内存块号的范围应该是 0 ~ 220 -1

内存块号至少要用 20 bit 来表示

至少要用3B来表示块号(38=24bit)

由于页号是隐含的,因此每个页表项占3B,存储整个页表至少需要 3(n+1)B注意:页表记录的只是内存块号,而不是内存块的起始地址!

J 号内存块的起始地址 = J * 内存块大小总结:页面大小刚好是 2 的整数幂有什么好处?

① 逻辑地址的拆分更加迅速——如果每个页面大小为 2KB,用二进制数表示逻辑地址,则末尾 K 位即为页内偏移量,其余部分就是页号。因此,如果让每个页面的大小为 2 的整数幂,计算机硬件就可以很方便地得出一个逻辑地址对应的页号和页内偏移量,而无需进行除法运算,从而提升了运行速度。② 物理地址的计算更加迅速——根据逻辑地址得到页号,根据页号查询页表从而找到页面存放的内存块号,将二进制表示的内存块号和页内偏移量拼接起来,就可以得到最终的物理地址。

结论:如果页面大小刚好是2的整数幂,则只需把页表中记录的物理块号拼接上页内偏移量就能得到对应的物理地址

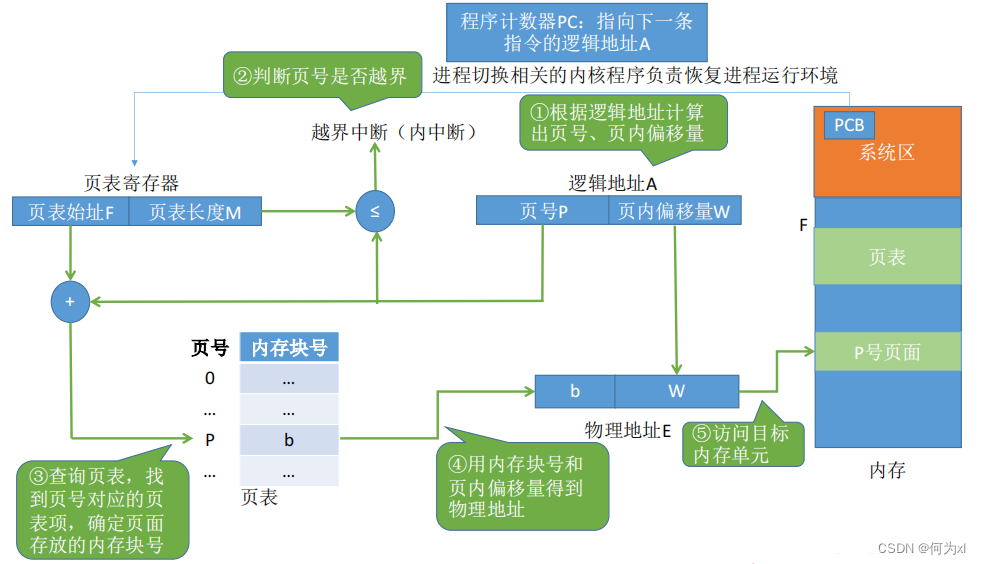

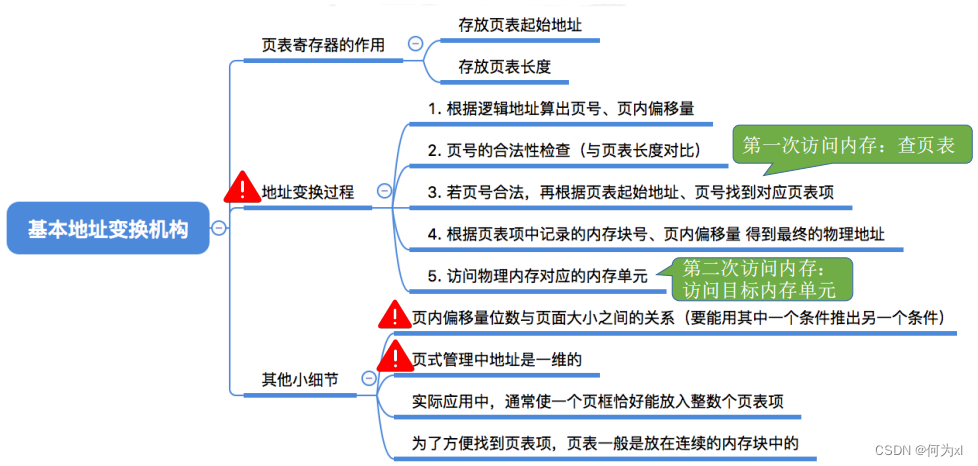

3. 基本分页式的基本地址变换机构(逻辑地址到物理地址的转换)

基本地址变换机构(用于实现逻辑地址到物理地址转换的一组硬件机构)的原理和流程。

通常会在系统中设置一个

页表寄存器(PTR),存放页表在内存中的起始地址F和页表长度M。进程未执行时,页表的始址 和 页表长度放在进程控制(PCB)中,当进程被调度时,操作系统内核会把它们放到页表寄存器中。

注意:页面大小是2的整数幂

设页面大小为L,逻辑地址A 到物理地址E 的变换过程如下:- 计算页号P(P = A/L)和页内偏移量W(W=A%L)。

- 比较页号Р 和页表长度M,若 P>M,则产生越界中断,否则继续执行。

页表中页号Р 对应的页表项地址 = 页表始址F + 页号P x 页表项长度,取出该页表项内容b,即为物理块号。要注意区分页表长度和页表项长度。页表长度的值是指一共有多少页,页表项长度是指页地址占多大的存储空间。- 计算 E= b * L+W,用得到的物理地址E 去访问内存。

例:若页面大小L 为 1K 字节,页号2对应的内存块号 b = 8,将逻辑地址 A=2500 转换为物理地址E。

等价描述:某系统按字节寻址,逻辑地址结构中,页内偏移量占10位,页号2对应的内存块号 b = 8, 将逻辑地址 A=2500

转换为物理地址E。答案: ①计算页号、页内偏移量 页号P = A/L = 2500/1024 = 2; 页内偏移量 W = A%L = 2500%1024 =

452 ②根据题中条件可知,页号2没有越界,其存放的内存块号 b = 8 ③物理地址 E = b * L + W = 8 * 1024 +

425 = 86444. 页表项的大小

实际应用中,通常使一个页框恰好能够放入整数个页表项。

上述例题结论:理论上,页表项长度为 3B 即可表示内存块号的范围,但是,为了方便页表的查询,常常会让一个页表项占更多的字节,使得每个页面恰好可以装得下整数个页表项。

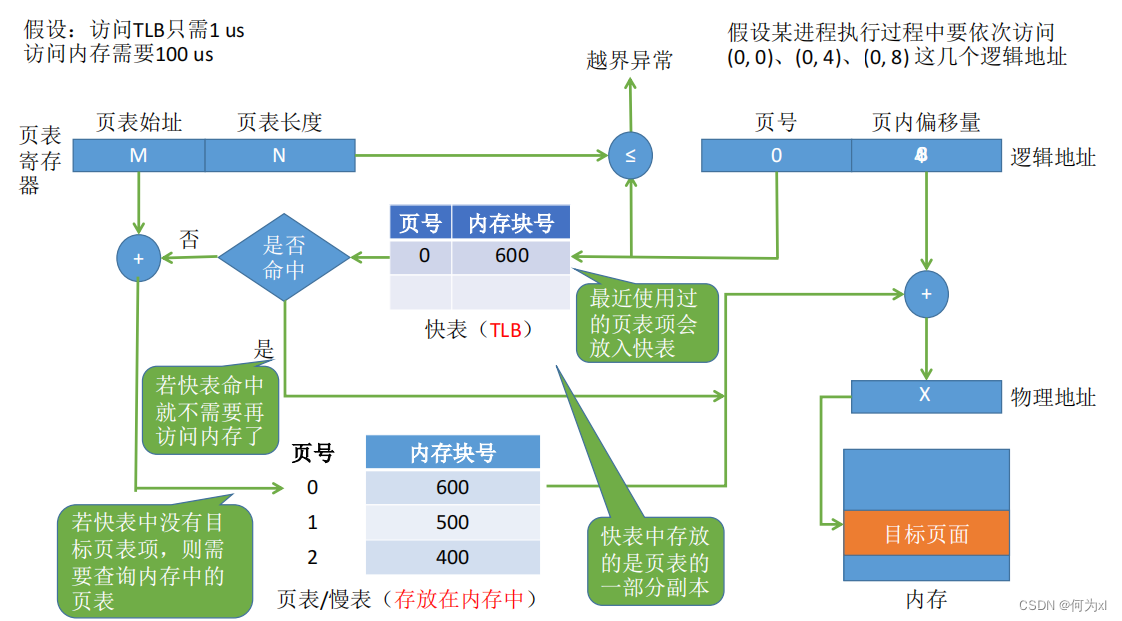

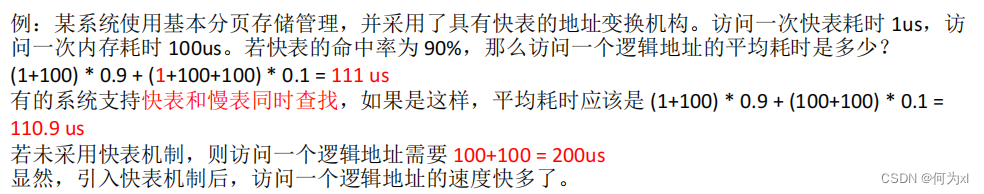

5. 具有快表的地址变换机构

具有快表的地址变换机构是基本地址变换机构的改进版本

快表

快表,又称联想寄存器(TLB, translation lookaside buffer ),是一种访问速度比内存快很多的高速缓存(TLB不是内存!),用来存放最近访问的页表项的副本,可以加速地址变换的速度。与此对应,内存中的页表常称为慢表。

引入快表后,地址的变换过程:① CPU给出逻辑地址,由某个硬件算得页号、页内偏移量,将页号与快表中的所有页号进行比较。

② 如果找到匹配的页号,说明要访问的页表项在快表中有副本,则直接从中取出该页对应的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。因此,若快表命中,则访问某个逻辑地址仅需一次访存即可。

③ 如果没有找到匹配的页号,则需要访问内存中的页表,找到对应页表项,得到页面存放的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。因此,若快表未命中,则访问某个逻辑地址需要两次访存(注意:在找到页表项后,应同时将其存入快表,以便后面可能的再次访问。但若快表已满,则必须按照一定的算法对旧的页表项进行替换)

局部性原理

时间局部性:如果执行了程序中的某条指令,那么不久后这条指令很有可能再次执行;如果某个数据被访问过,不久之后该数据很可能再次被访问。(因为程序中存在大量的循环)

空间局部性:一旦程序访问了某个存储单元,在不久之后,其附近的存储单元也很有可能被访问。(因为很多数据在内存中都是连续存放的)

TLB 和 普通 Cache 的区别——TLB 中只有页表项的副本,而普通 Cache 中可能会有其他各种数据的副本。

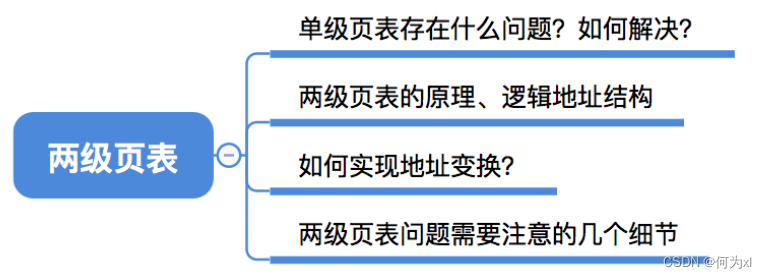

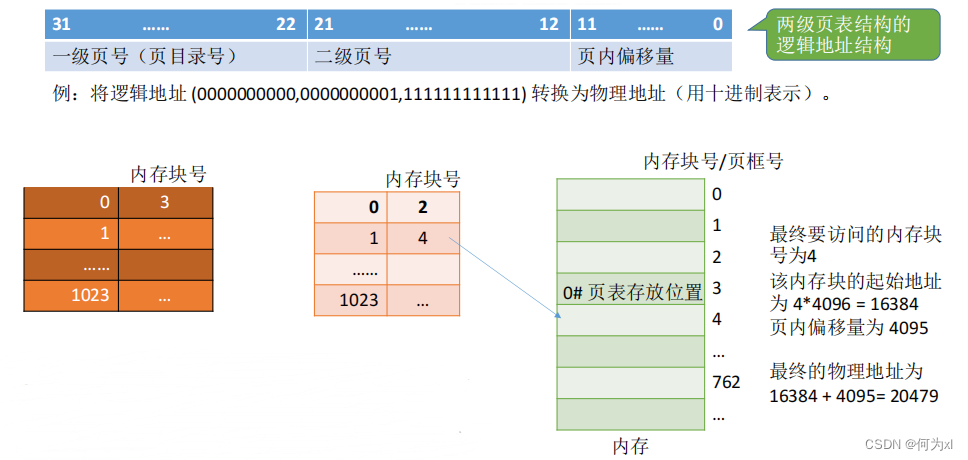

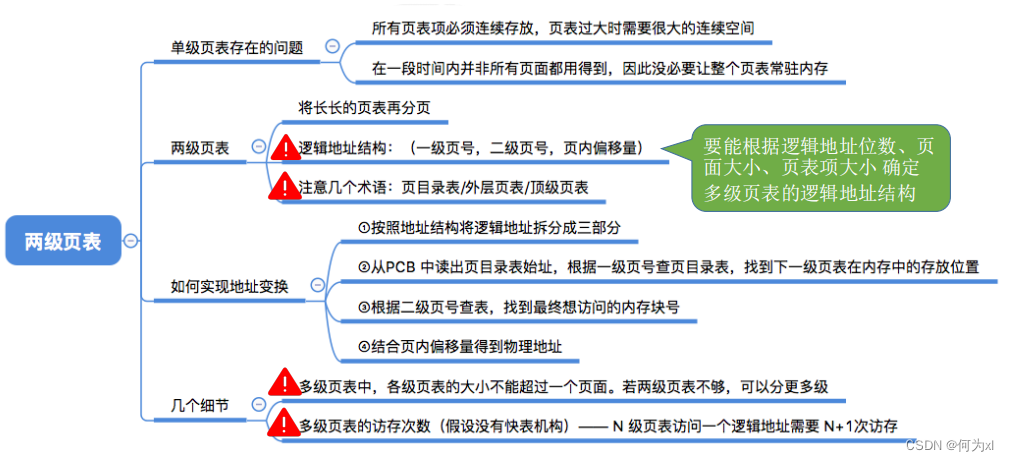

6. 两级页表

单级页表存在的问题

某计算机系统按字节寻址,支持 32 位的逻辑地址,采用分页存储管理,页面大小为 4KB,页表项长度为 4B。

4KB = 2 12 2^{12} 212B,因此页内地址要用12位表示,剩余 20 位表示页号。因此,该系统中用户进程最多有 2 20 2^{20} 220 页。相应的,一个进程的页表中,最多会有 2 20 2^{20} 220 = 1M = 1,048,576 个页表项,所以一个页表最大需要 2 20 2^{20} 220 * 4B = 2 22 2^{22} 222 B,共需要 2 22 / 2 12 = 2 10 2^{22} / 2^{12} = 2^{10} 222/212=210个页框存储该页表。需要专门给进程分配 1024 个连续的页框来存放它的页表。

根据局部性原理可知,很多时候,进程在一段时间内只需要访问某几个页面就可以正常运行了。因此没有必要让整个页表都常驻内存。

把页表再分页并离散存储,然后再建立一张页表记录页表各个部分的存放位置,称为页目录表,或称外层页表,或称顶层页表。

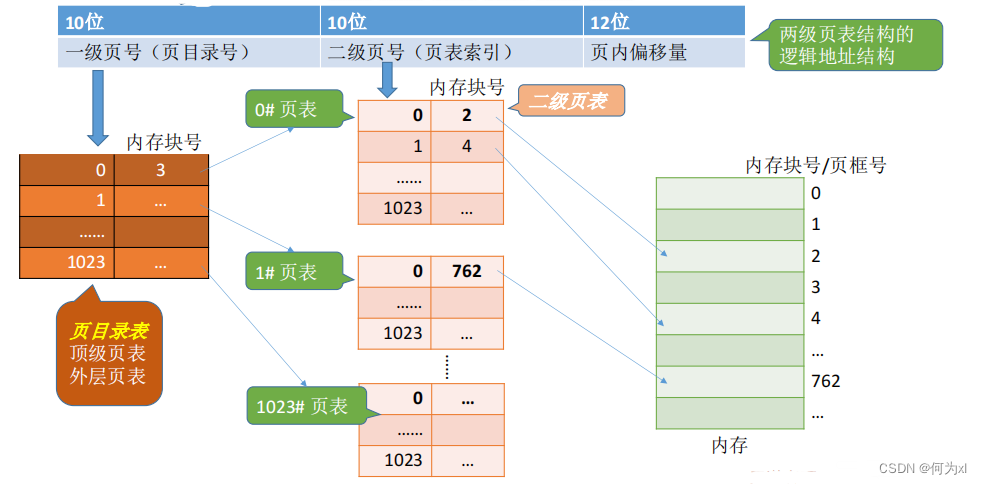

7. 两级页表的原理、地址结构

32位逻辑地址空间,页表项大小为4B,页面大小为 4KB,则页内地址占12位。每个页面可存放 4K/4 =1K = 2 10 2^{10} 210 = 1024 个页表项。

10位一级页号刚好可表示 0~1023,之前计算出页内偏移地址占用了 12 位,还剩下 10 位,恰好使得二级页表的大小在一页之内。

地址变换过程:

①按照地址结构将逻辑地址拆分成三部分;

②从PCB 中读出页目录表始址,再根据一级页号查页目录

表,找到下一级页表在内存中的存放位置;

③根据二级页号查二级页表,找到最终想访问的内存块号;

④结合页内偏移量得到物理地址。

两级页表的访存次数分析(假设没有快表机构)

第一次访存:访问内存中的页目录表

第二次访存:访问内存中的二级页表

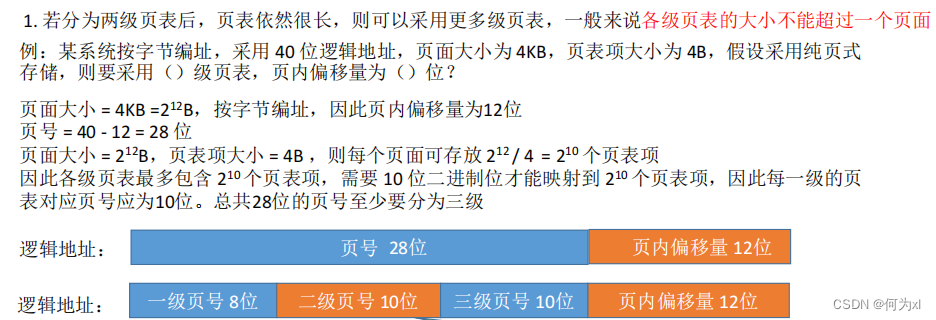

第三次访存:访问目标内存单元8. 多级页表

如果只分为两级页表,则一级页号占 18 位,也就是说页目录表中最多可能有 2 18 2^{18} 218 个页表项,显然,一个页面是放不下这么多页表项的。9. 两级页表总结

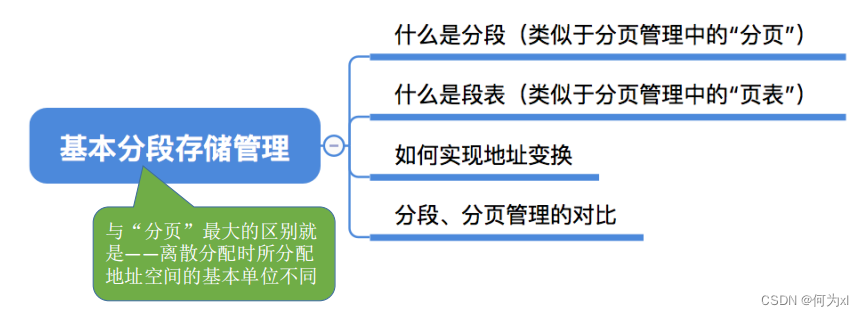

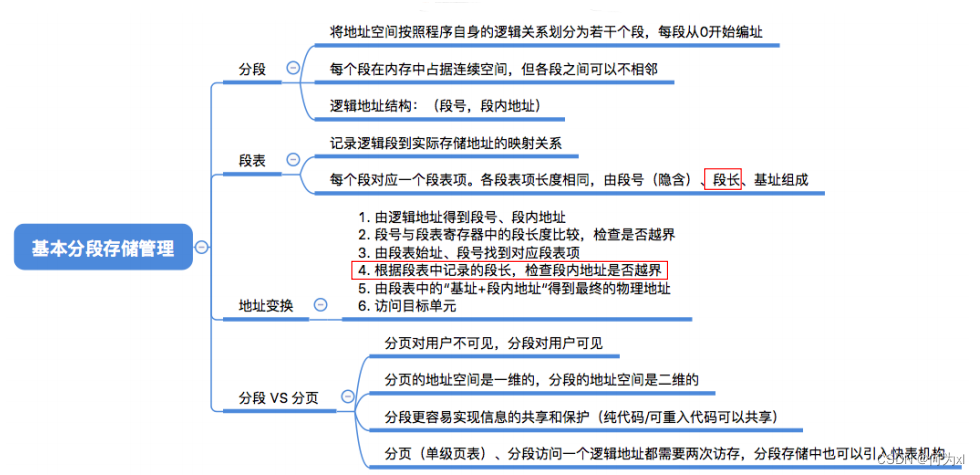

(二)、基本分段存储管理

与“分页”最大的区别就是——离散分配时所分配地址空间的基本单位不同。1. 分段

进程的地址空间:按照程序

自身的逻辑关系划分为若干个段,每个段都有一个段名(在低级语言中,程序员使用段名来编程),每段从0开始编址内存分配规则:

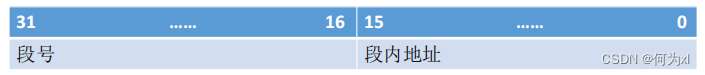

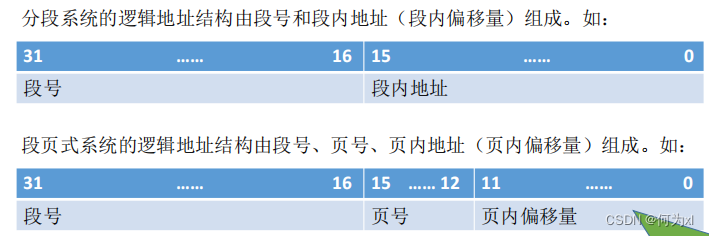

以段为单位进行分配,每个段在内存中占据连续空间,但各段之间可以不相邻。分段系统的逻辑地址结构由段号(段名)和段内地址(段内偏移量)所组成。如:

段号的位数决定了每个进程最多可以分几个段

;段内地址位数决定了每个段的最大长度是多少在上述例子中,若系统是按字节寻址的,则段号占16位,因此在该系统中,每个进程最多有 2 1 6 2^16 216 = 64K 个段。段内地址占 16位,因此每个段的最大长度是 2 1 6 2^16 216 = 64KB。

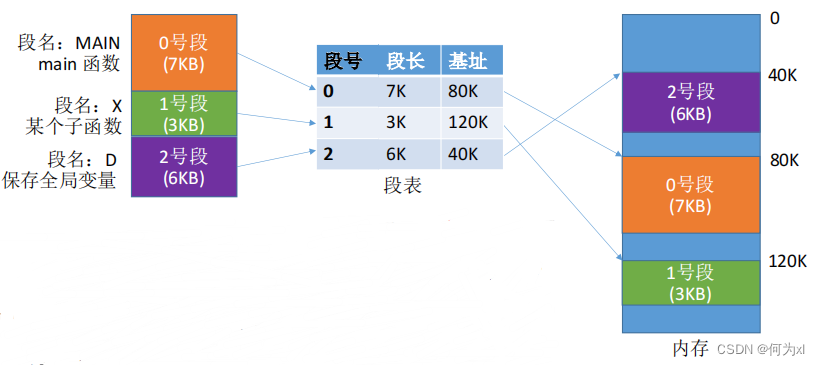

2. 段表

程序分多个段,各段离散地装入内存,为了保证程序能正常运行,就必须能从物理内存中找到各个逻辑段的存放位置。为此,需为每个进程建立一张段映射表,简称“段表”。

- 每个段对应一个段表项,其中记录了该段在内存中的

起始位置(又称“基址”)和段的长度。 - 各个段表项的长度是相同的。例如:某系统按字节寻址,采用分段存储管理,逻辑地址结构为(段号16位, 段内地址16位),因此用16位即可表示最大段长。物理内存大小为4GB(可用32位表示整个物理内存地址空间)。因此,可以让每个段表项占 16+32 = 48位,即 6B。由于段表项长度相同,因此段号可以是隐含的,不占存储空间。若段表存放的起始地址为 M,则 K号段对应的段表项存放的地址为 M + K*6

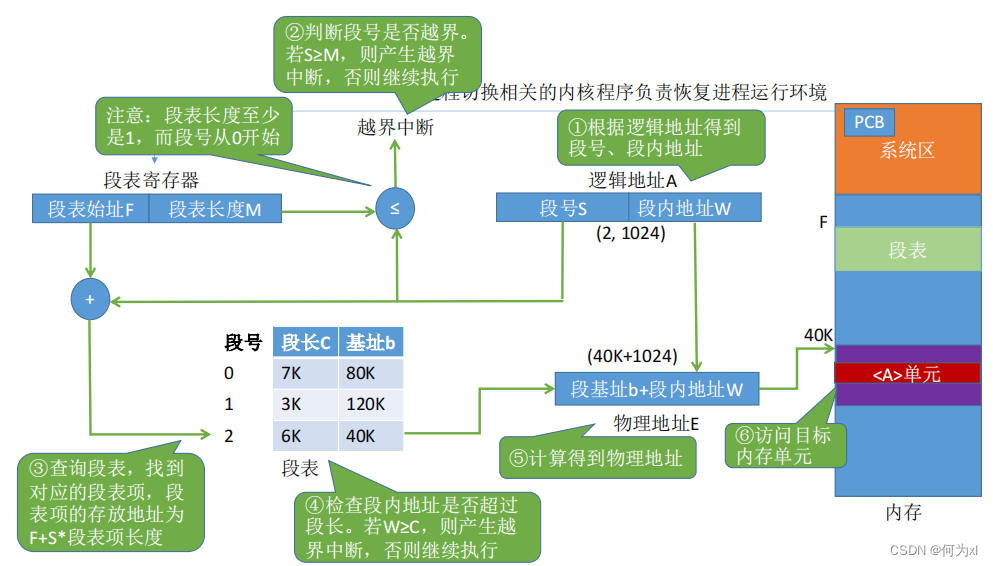

3. 段式的地址变换

4. 分段、分页管理的对比

-

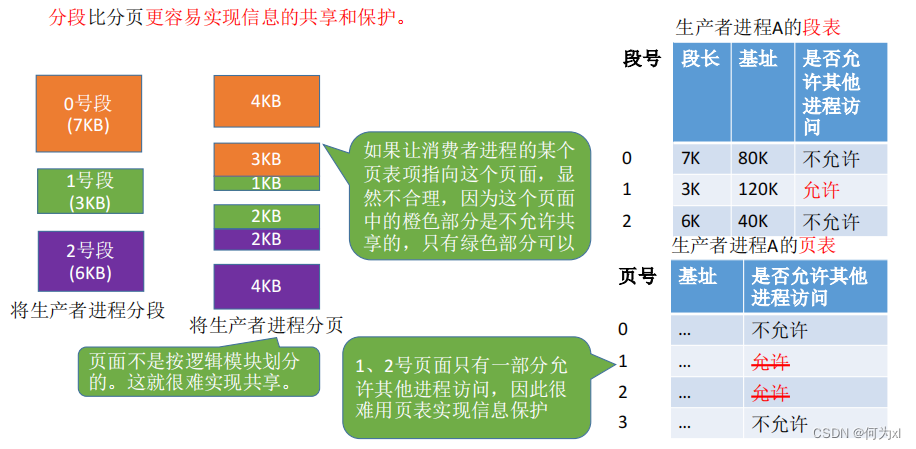

页是信息的物理单位。分页的主要目的是为了实现离散分配,提高内存利用率。分页仅仅是系统管理上的需要,完全是系统行为,分页对用户是不可见的。

段是信息的逻辑单位。分段的主要目的是更好地满足用户需求。一个段通常包含着一组属于一个逻辑模块的信息。分段对用户是可见的,用户编程时需要显式地给出段名。 -

页的大小固定且由系统决定。段的长度却不固定,决定于用户编写的程序。

-

分页的用户进程

地址空间是一维的,程序员只需给出一个记忆符即可表示一个地址。分段的用户进程地址空间是二维的,程序员在标识一个地址时,既要给出段名,也要给出段内地址。 -

分段比分页更容易实现信息的共享和保护。不能被修改的代码称为纯代码或可重入代码(不属于临界资源),这样的代码是可以共享的。可修改的代码是不能共享的。

思考:访问一个逻辑地址需要几次访存?

解答:

-

分页(单级页表):第一次访存——查内存中的页表,第二次访存——访问目标内存单元。总共两次访存。

-

分段:第一次访存——查内存中的段表,第二次访存——访问目标内存单元。总共两次访存。

-

与分页系统类似,分段系统中也可以引入快表机构,将近期访问过的段表项放到快表中,这样可以少一次访问,加快地址变换速度。

5. 基本分段存储管理总结

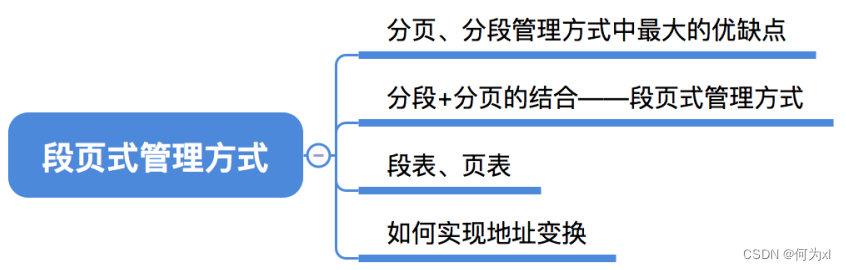

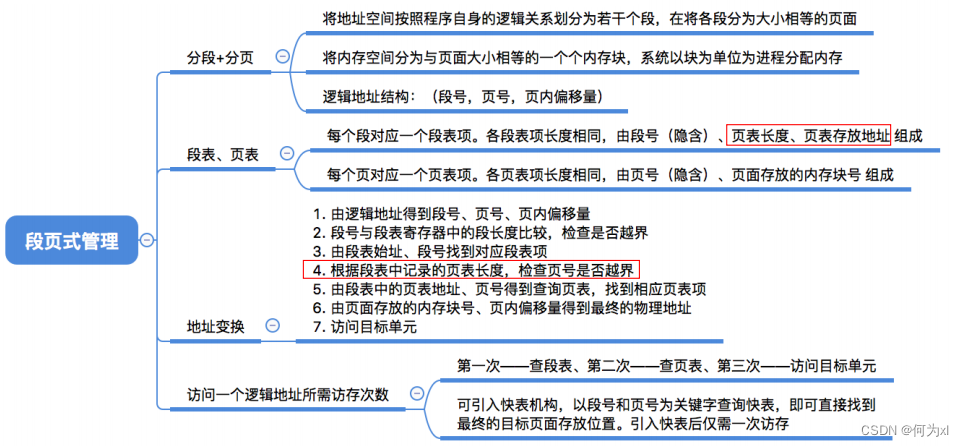

(三)、段页式存储管理

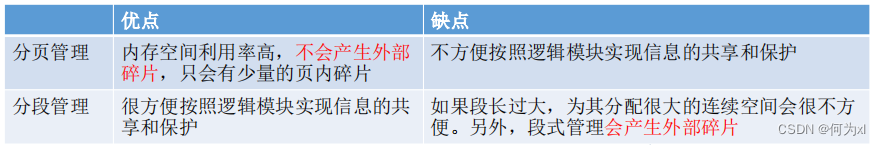

1. 分页、分段的优缺点分析

分段管理中产生的外部碎片也可以用“紧凑”来解决,只是需要付出较大的时间代价。2. 段页式管理方式(分段+分页=段页式管理)

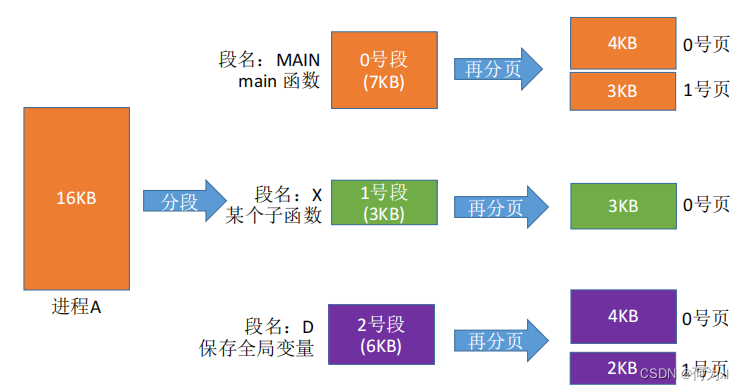

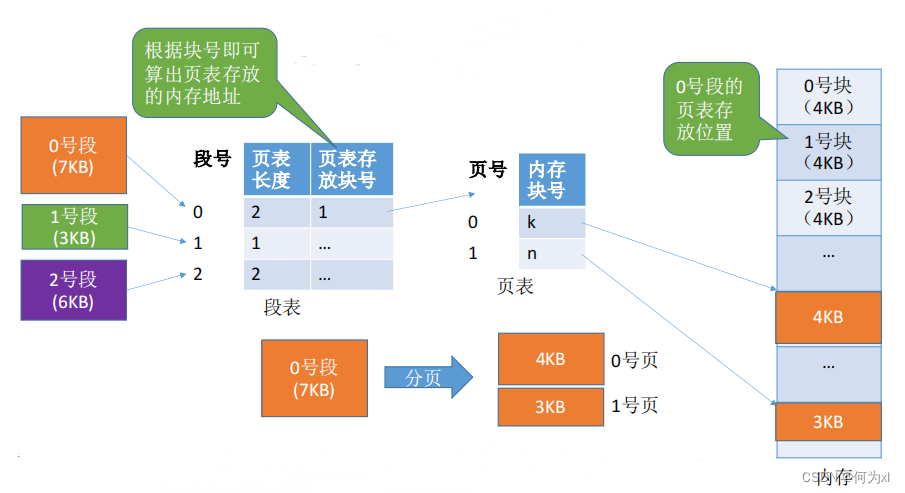

将进程按逻辑模块分段,再将各段分页,再将内存空间分为大小相同的内存块/页框/页帧/物理块进程前将各页面分别装入各内存块中。

3. 段页式管理的逻辑地址结构

段号的位数决定了每个进程最多可以分几个段;页号位数决定了每个段最大有多少页;页内偏移量决定了页面大小、内存块大小是多少。

- 每个段对应一个段表项,每个段表项由段号、页表长度、页表存放块号(页表起始地址)组成。每个段表项长度相等,段号是隐含的。

- 每个页面对应一个页表项,每个页表项由页号、页面存放的内存块号组成。每个页表项长度相等,页号是隐含的。

注:在一个进程中,段表只有一个,而页表可能有多个。

“分段”对用户是可见的,程序员编程时需要显式地给出段号、段内地址。而将各段“分页”对用户是不可见的。系统会根据段内地址自动划分页号和页内偏移量。因此段页式管理的地址结构是二维的。

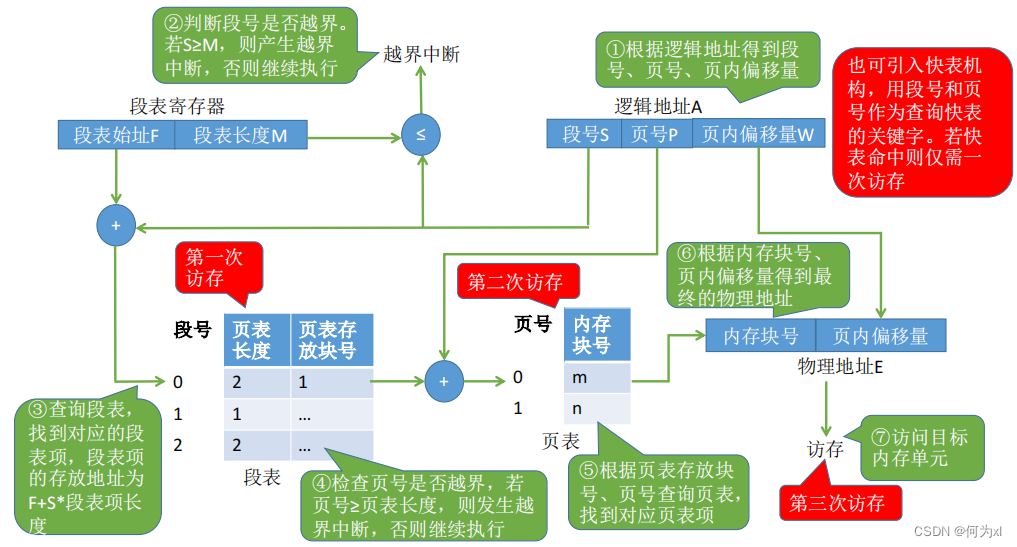

4. 段页式的地址变换

5. 段页式存储管理总结

-

相关阅读:

图论之Floyd,多源图最短路如何暴力美学?

Flutter 安装教程 + 运行教程

linux网络

【附源码】计算机毕业设计JAVA学生校内兼职管理平台

2.21每日一题(隐函数求导+变上限积分求导)

98%的人都不会使用这6种地图可视化方法,学会直接涨薪5K

ssm南工二手书交易平台毕业设计源码172334

给定一个 N×3 的矩阵 matrix,对于每一个长度为 3 的小数组 arr,都表示一个大楼的三个数据,请返回整体的轮廓线数组。

c语言练习题81:颠倒二进制位

【云原生】SpringCloud Alibaba 之 Nacos注册中心实战

- 原文地址:https://blog.csdn.net/weixin_43848614/article/details/126805074