-

IC设计高级019:一种简单超时机制

1、超时判断机制

在设计中,为了增加异常处理能力,保证设备的正常运行,常常需要进行超时判断。

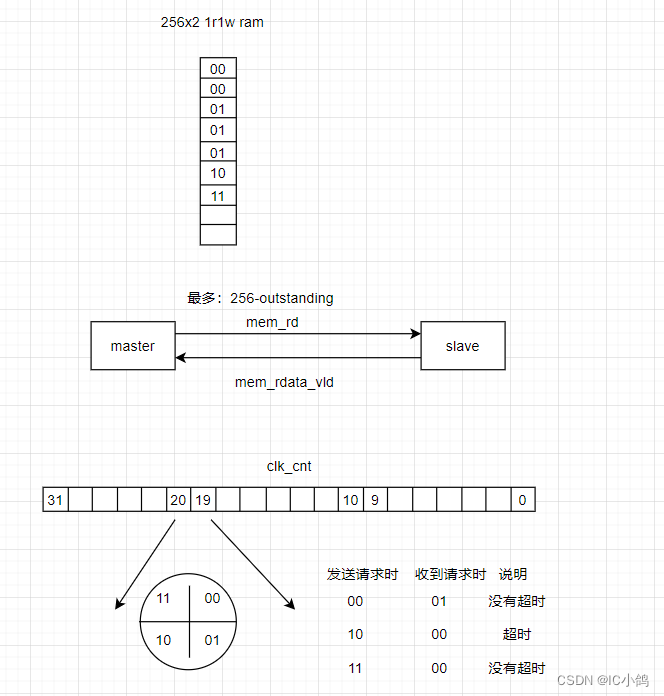

如下图,当master发起mem读请求后,收到读返回数据时,进行超时判断,如果超时,则数据丢弃,如果没有超时,则数据正常接收。

2、一种简单的超时机制

如果在数据发送过程中,发送者向接收者发送数据,通常需要接收者通知发送者自身是否可以接收数据

采用一个公共的32bit clk_cnt作为时间基准,根据不同的超时精度,采用32bit中的连续2bit,1GHz时钟,每个周期1n,例如采用clk_cnt[20:19],可以记录2^21ns级别的精度,即2ms级别的时间精度。

本文中master能够发起256个outstanding请求,req_id[7:0]从0到255,且工作时钟clk为1Ghz,发起的mem读请求,且在1us后都没有收到数据,则认为超时。

步骤1:master发起mem_rd请求时,以req_id作为地址,将clk_cnt[20:19]作为data,写入256x2 1r1w_ram中。

步骤2:当master收到读返回数据时,以req_id作为地址从ram中读取data,记作clk_cnt_record

步骤3:提取当前时刻clk_cnt[20:19],记录为clk_cnt_now,如果clk_cnt_now-clk_cnt_record 的绝对值大于1,则表示超时。

案例:

clk_cnt_record 为 10,clk_cnt_now为00,则表示超时。

clk_cnt_record 为 10,clk_cnt_now为11,则认为不超时。

3、特点说明

优点:此类设计比较简单,所需的逻辑资源较少,并且可以调节超时时间精度。

缺点:

- 如果超时时间过长,已经从clk_cnt_record翻转了一圈再返回时,则无法判断是否为超时。即clk_cnt_record(10)-->11-->00-->01-->10-->11(clk_cnt_now),实际已超时,但是判断为没有超时。

- 没有读返回数据时,无法判断是否超时。

-

相关阅读:

2.4GHz WiFi速率测试指导及Omnipeek 空口log分析

有关直方图的常用操作

三电系统集成技术杂谈

Android Wifi开发——Wifi锁(十九)

番茄免费小说

【【OpenCV实现图像:用OpenCV进行模板匹配】

java计算机毕业设计上虞烟草物流配送系统源码+系统+数据库+lw文档+mybatis+运行部署

20220726汇承科技的蓝牙模块HC-05的AT命令测试

springboot 整合rabbitMq保证消息一致性方案

nginx(三十九) ngx_http_realip_module模块学习

- 原文地址:https://blog.csdn.net/icxiaoge/article/details/126807407