-

计算机组成原理

第一章计算机系统概述

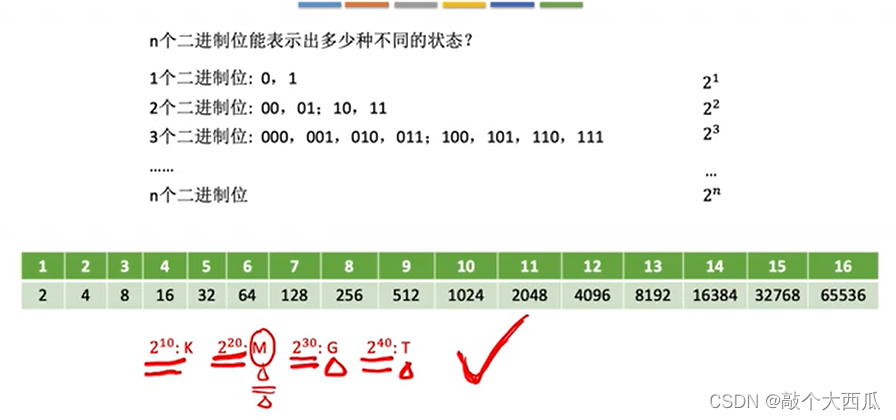

计算机硬件能识别的数据—二进制0/1

用低/高电平分别表示0/1,通过电信号传递数据

通过很多电路可以传递多个二进制数位,每个二进制数位成为1bit(比特)

数字,文字,图像如何用二进制表示呢?

CPU如何对二进制数进行加减乘除运算呢?

如何存储这些二进制数据呢?

如何从内存中取出想要的数据呢?

CPU如何识别和执行我们写的程序呢?什么是计算机系统

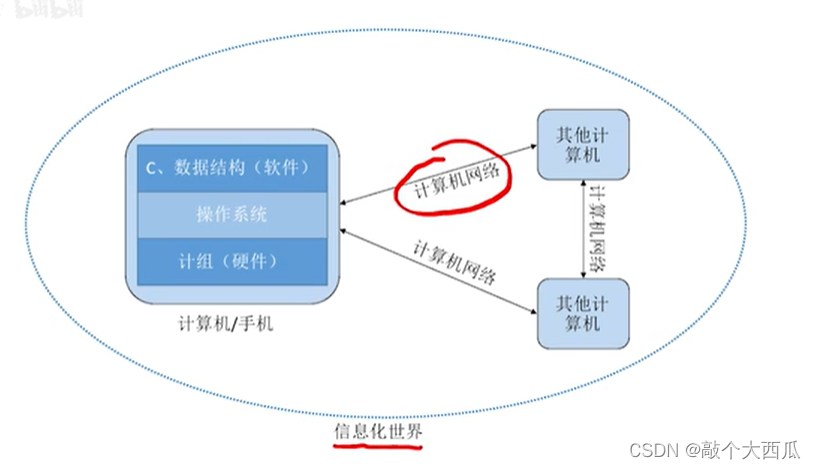

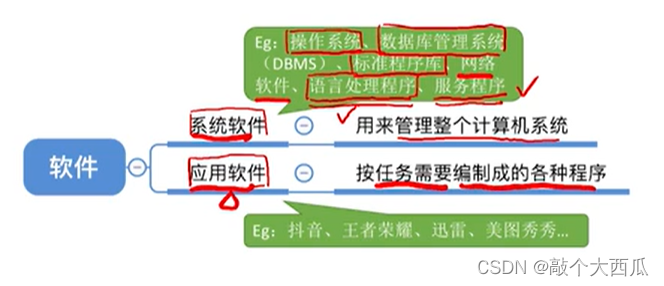

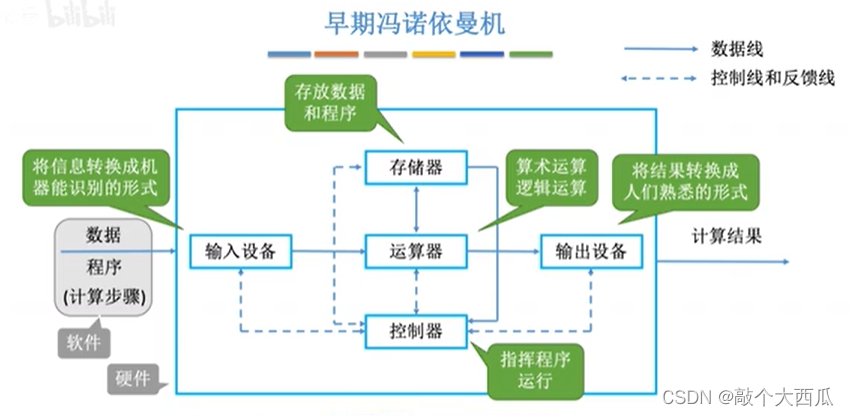

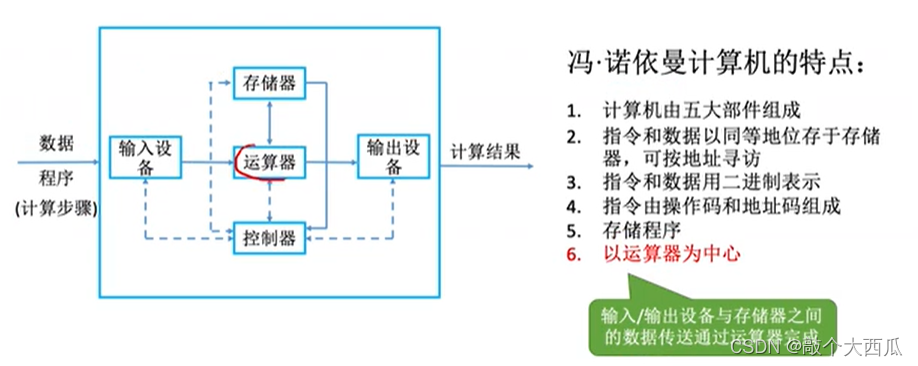

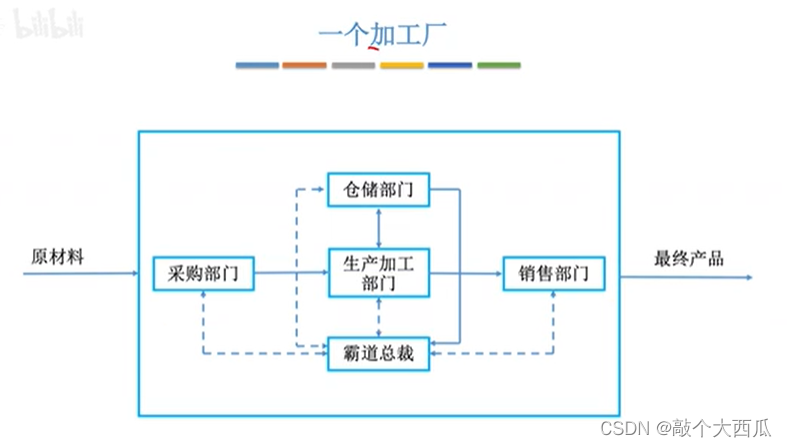

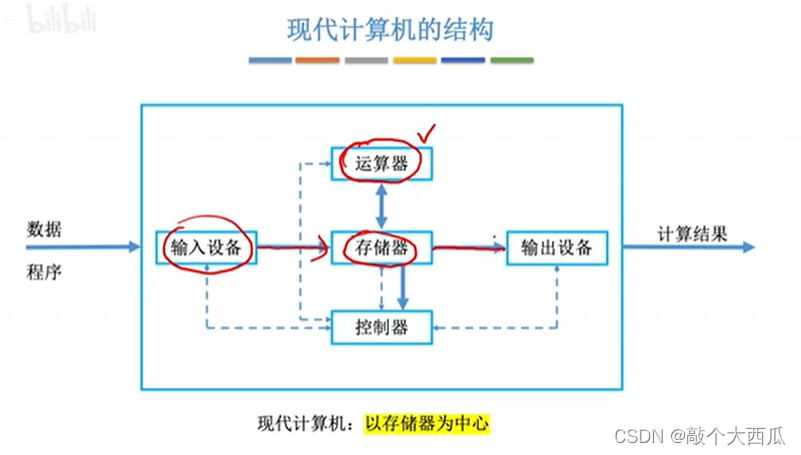

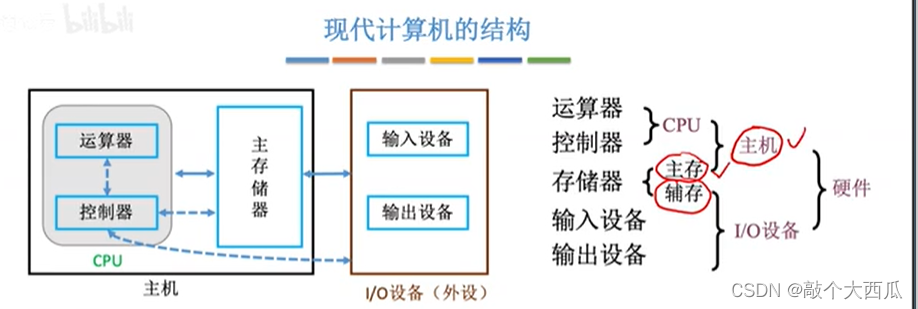

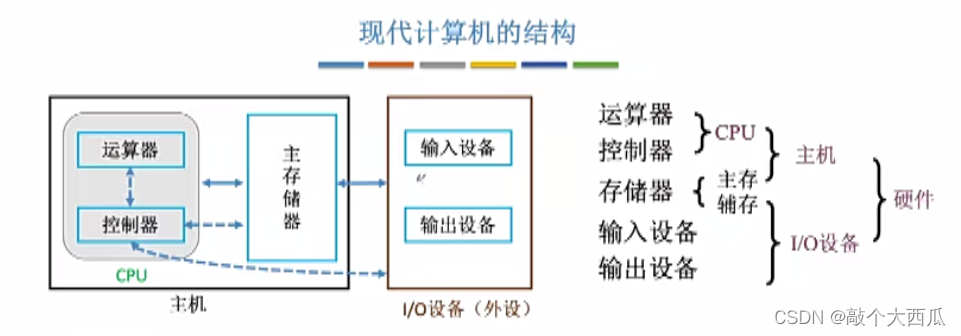

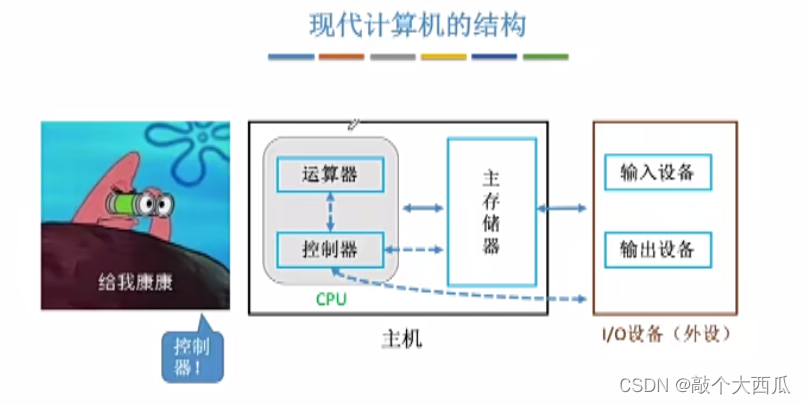

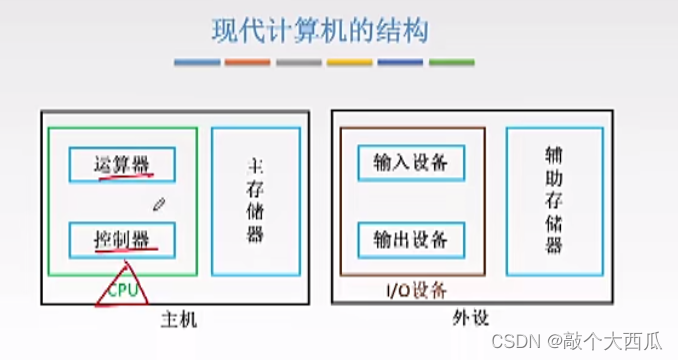

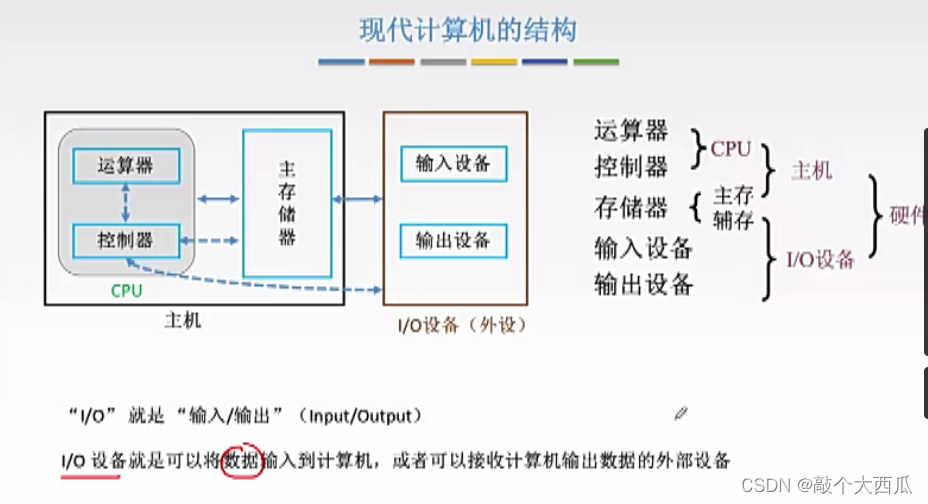

计算机系统等于硬件(计算机实体,如主机,外设等)加软件(由具有各类特殊功能的程序组成)

计算机性能的好坏取决于软硬件功能的总和

计算机应将的基本组成

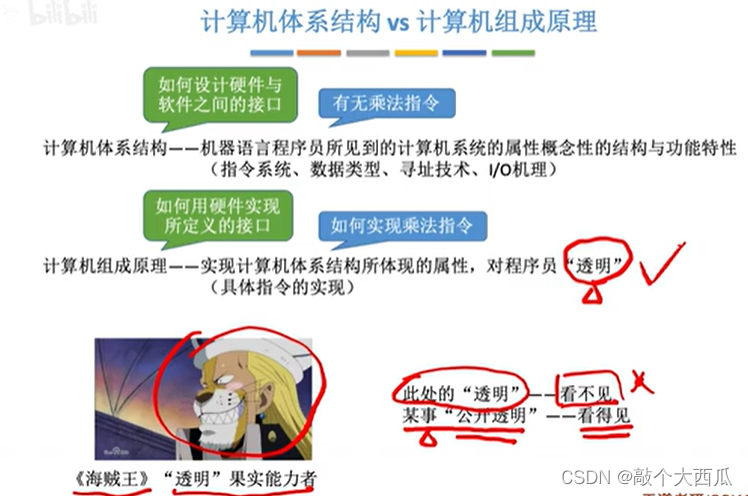

在计算机系统中,软件和硬件在逻辑上是等效的

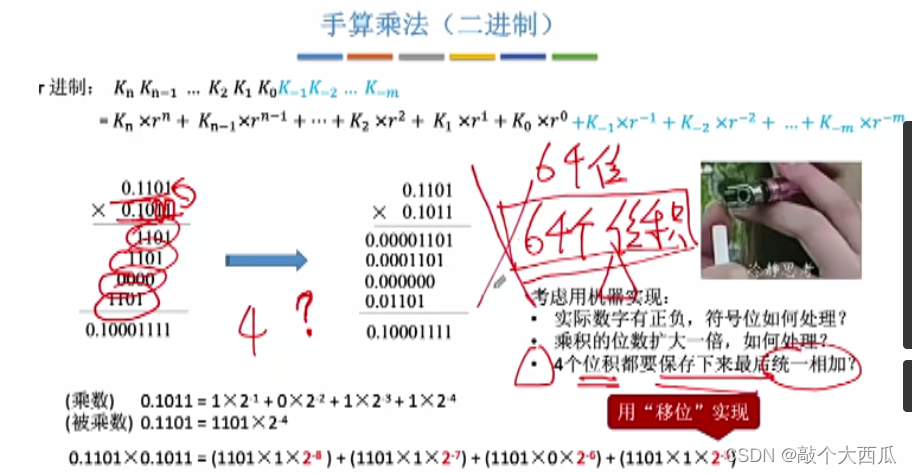

对于乘法运算,可以设计一个专门的硬件电路来实现乘法运算,也可以用软件的方式,执行多次加法运算来实现

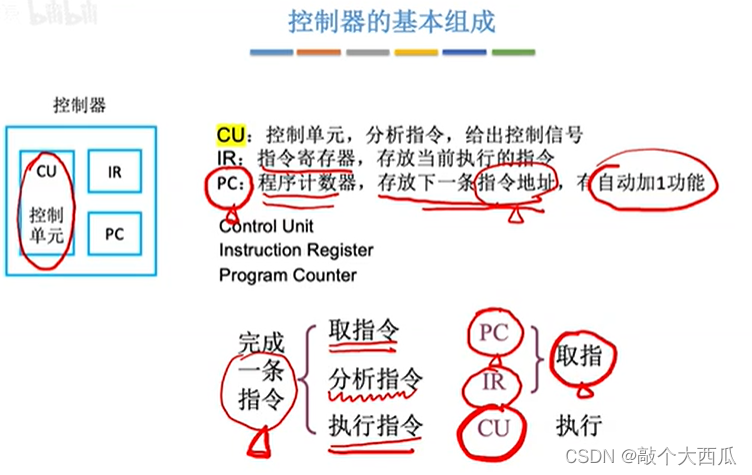

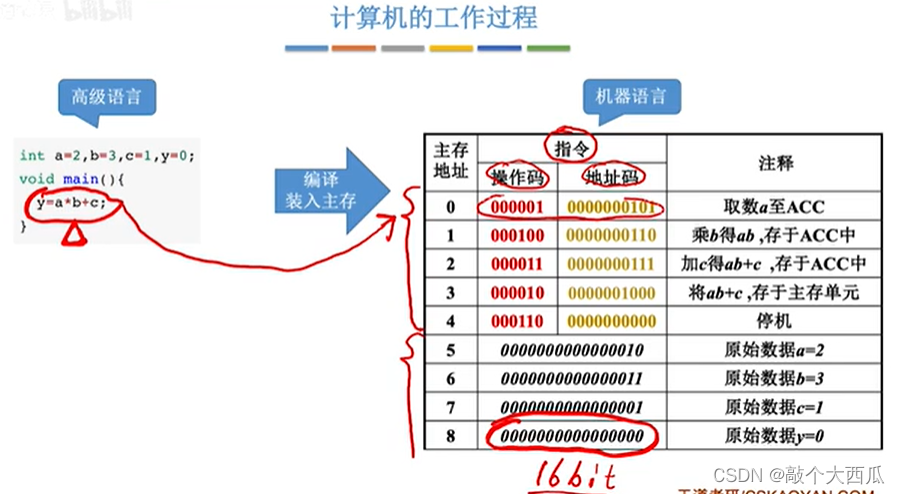

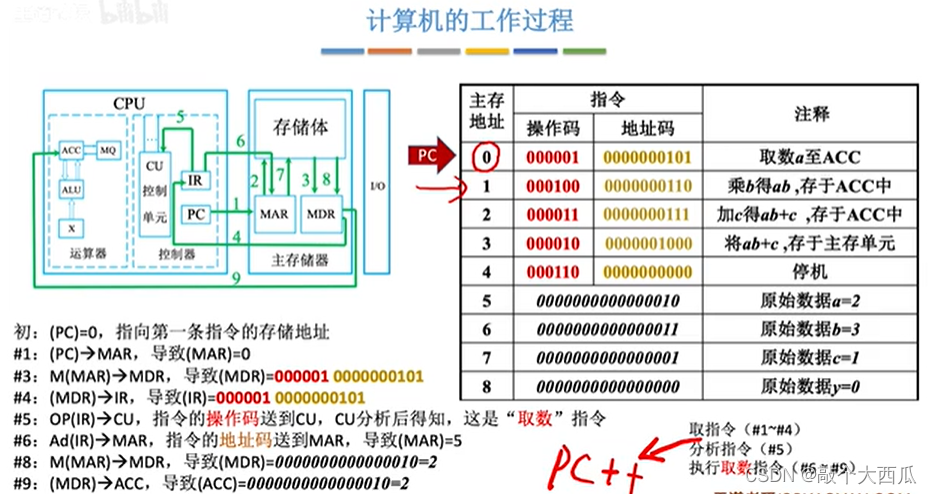

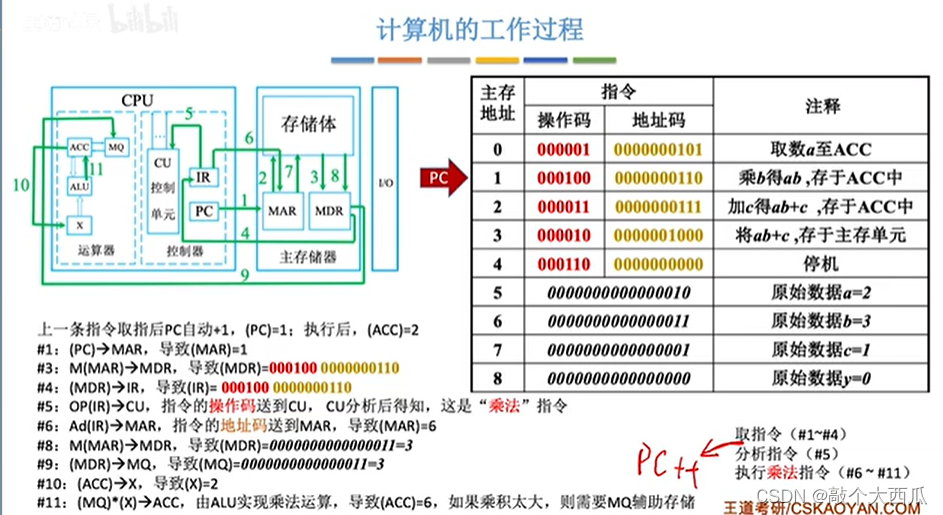

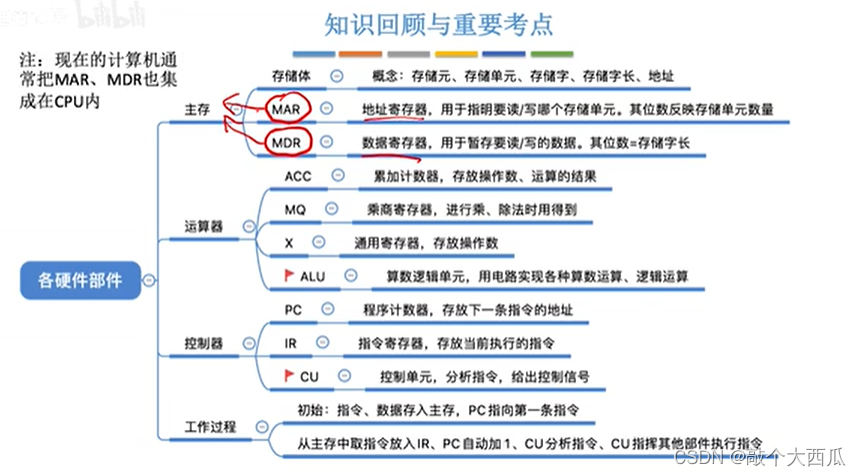

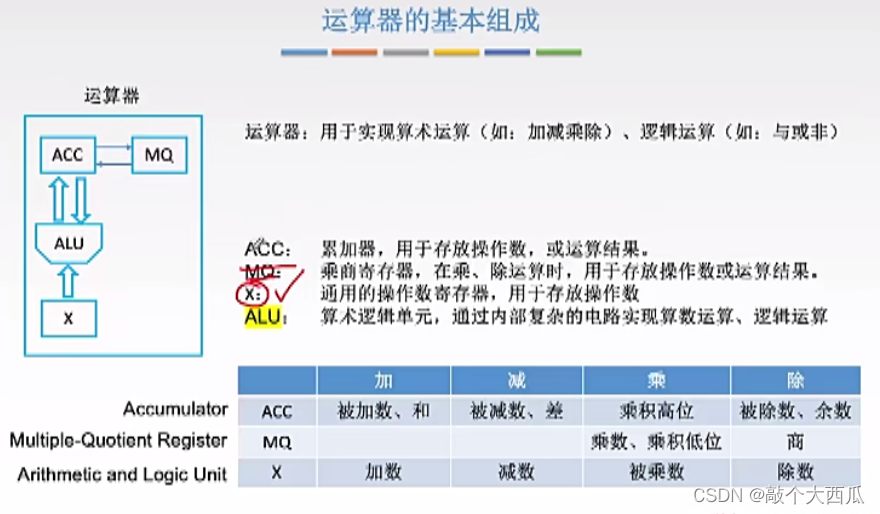

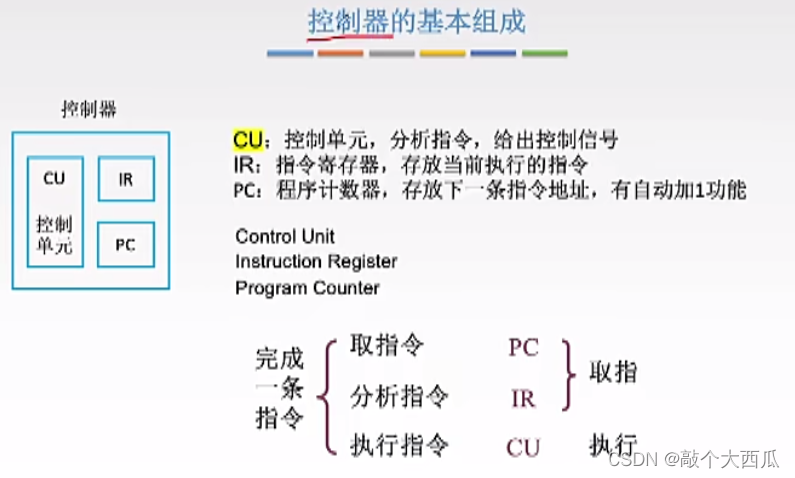

各个硬件的工作原理

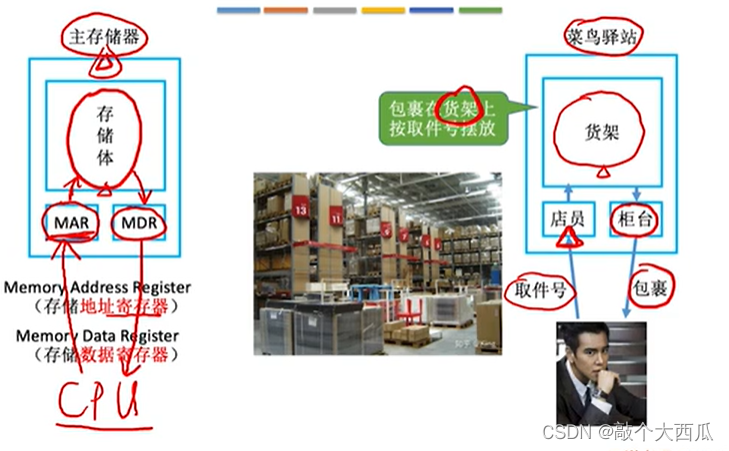

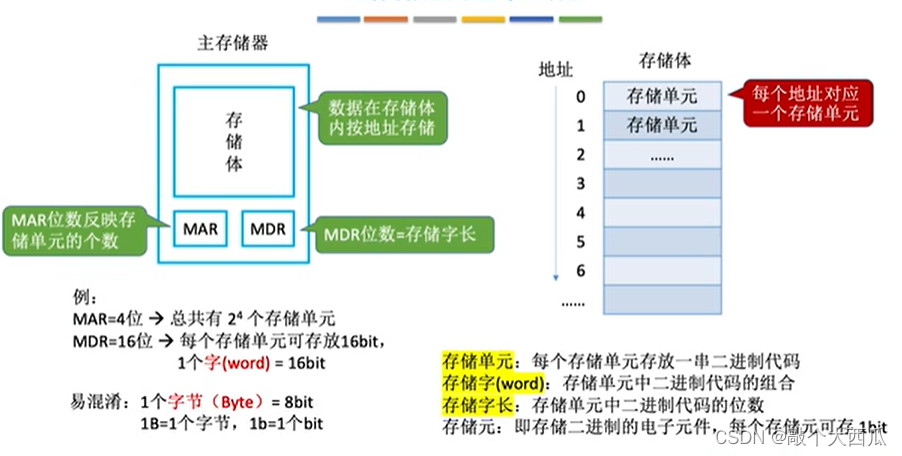

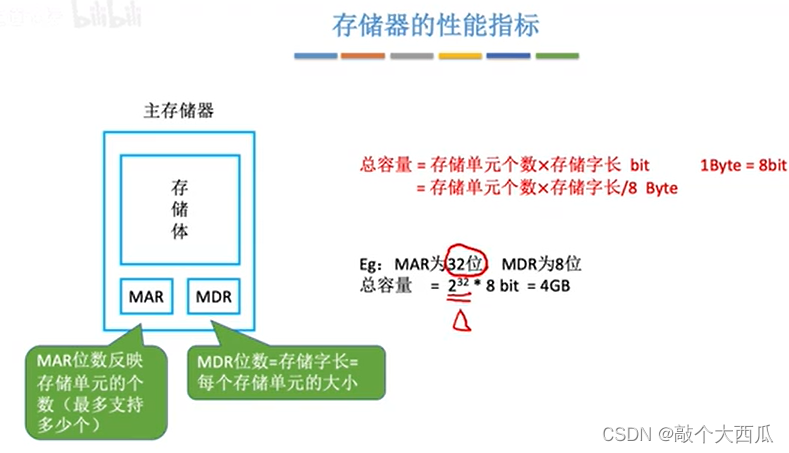

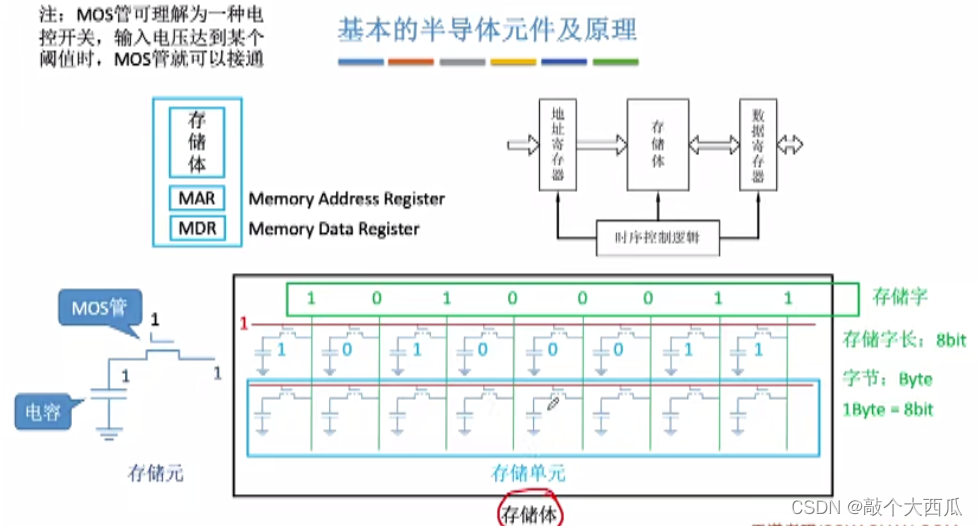

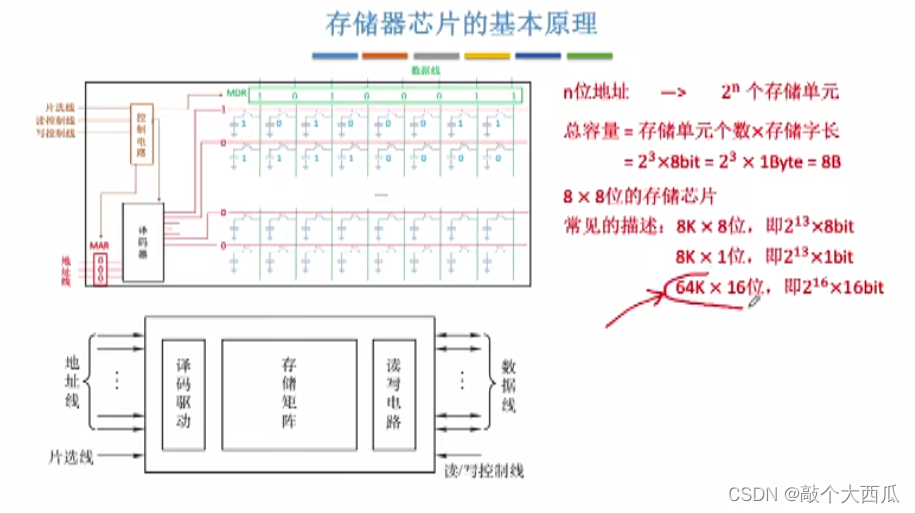

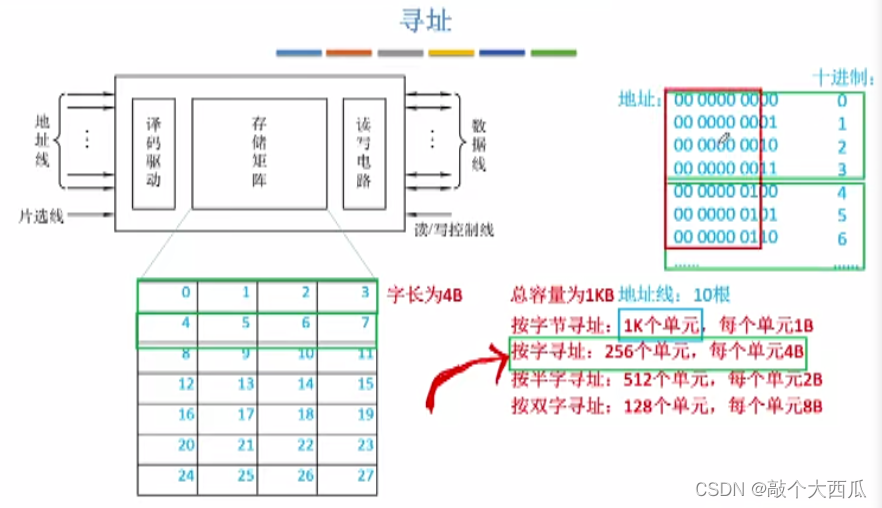

主存储器的基本组成

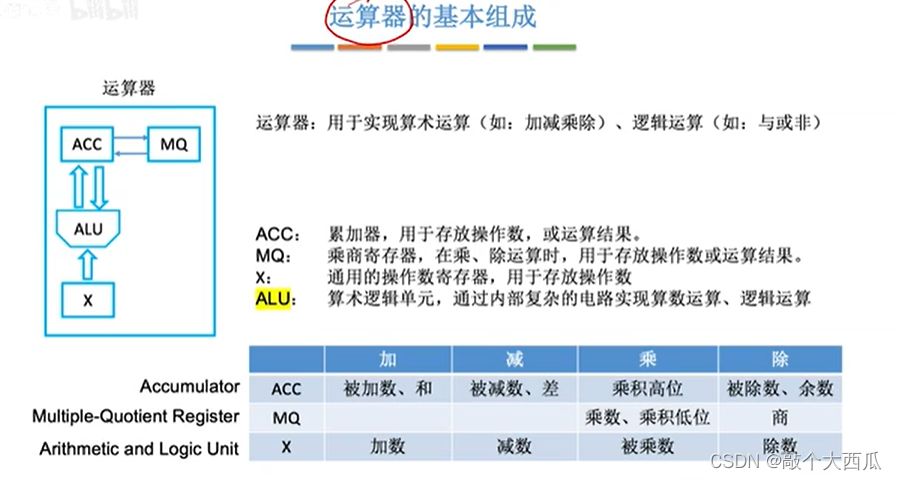

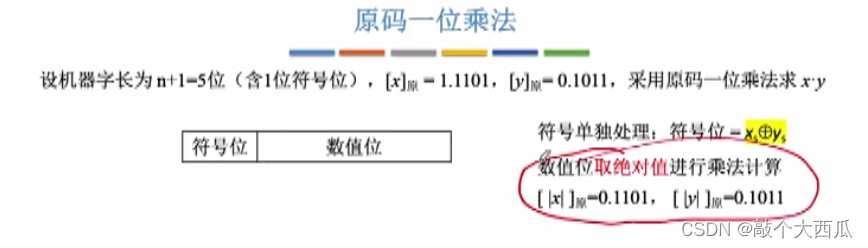

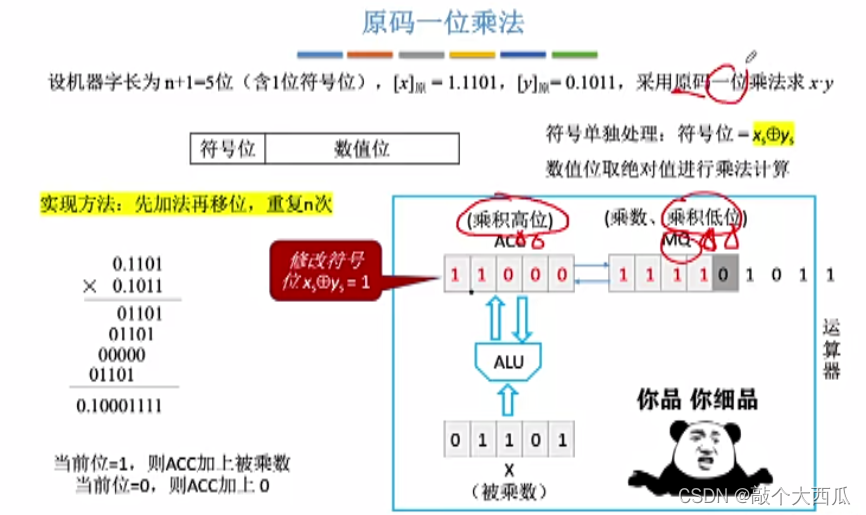

此处注意MQ和X中存放的操作数的种类不同,MQ中存放的是乘数,乘积低位(MQ寄存器中的乘数和X寄存器中的被乘数相乘以后乘积较大时会发生溢出,此时ACC中存放乘积高位,MQ中存放乘积低位),商(X寄存器中的除数除以ACC累加器中的被除数时余数存放在ACC中,商存放在MQ中)

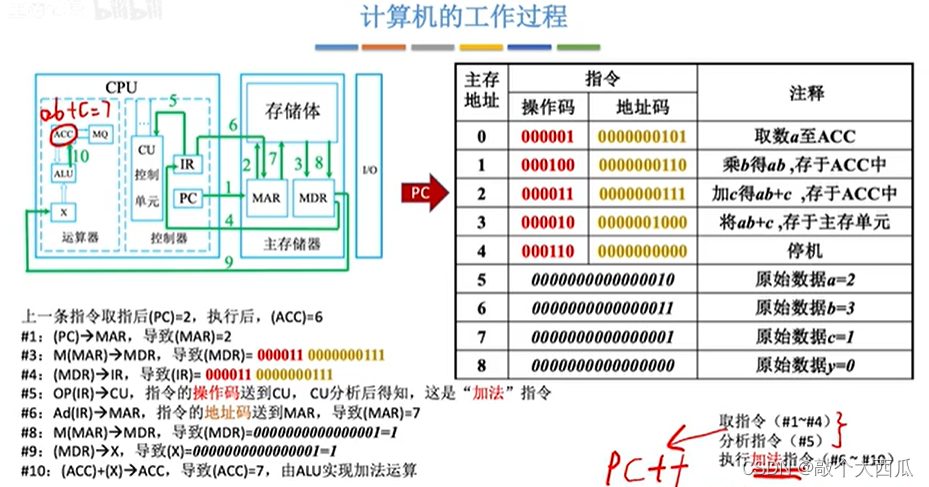

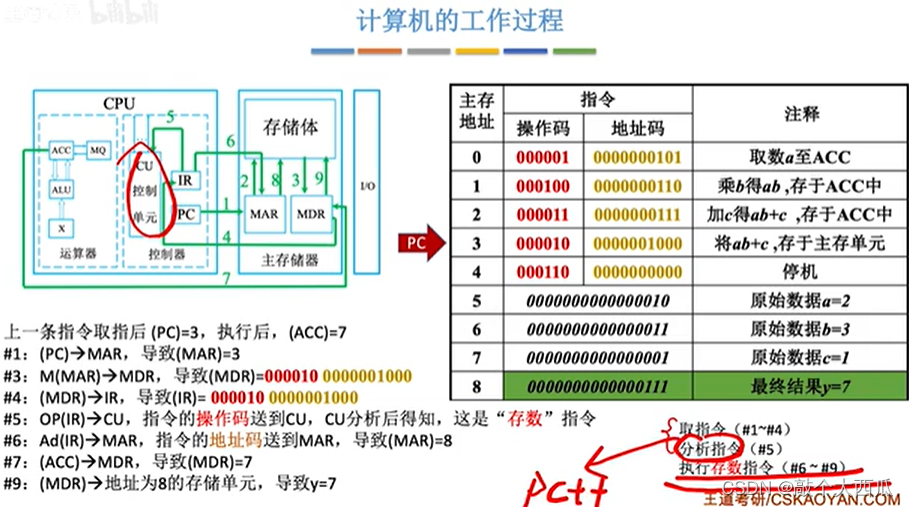

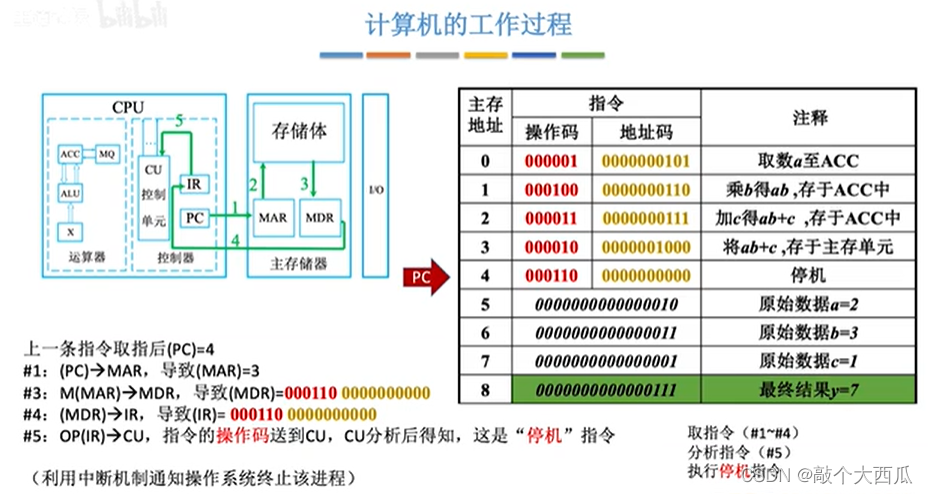

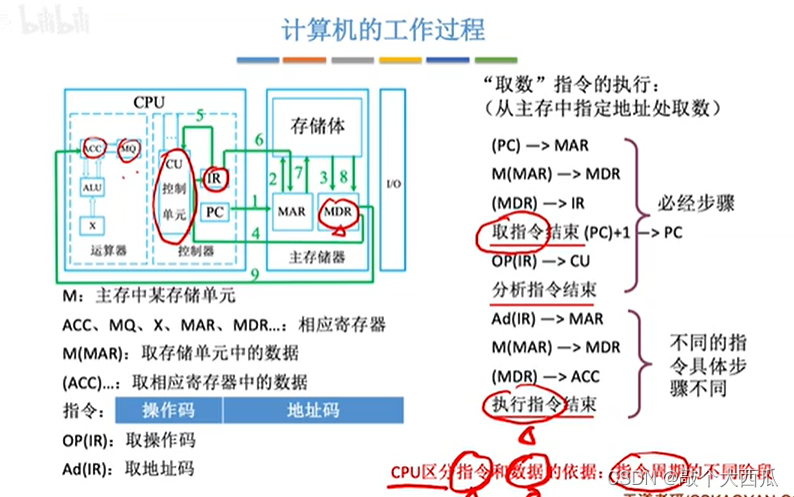

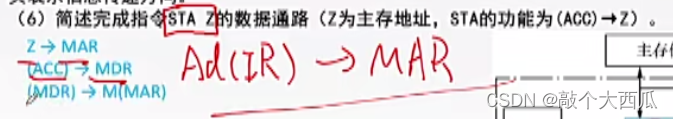

M(MAR)表示主存通过数据总线将MAR所指单元的内容送到MDR,OP(IR)是存在IR中的取数指令的操作码,如MOV就是操作码,Ad(IR)是操作数的地址

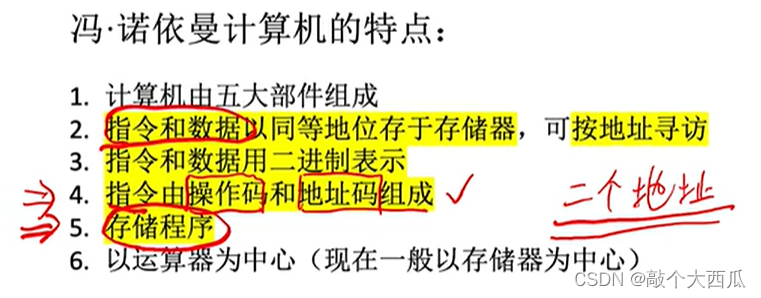

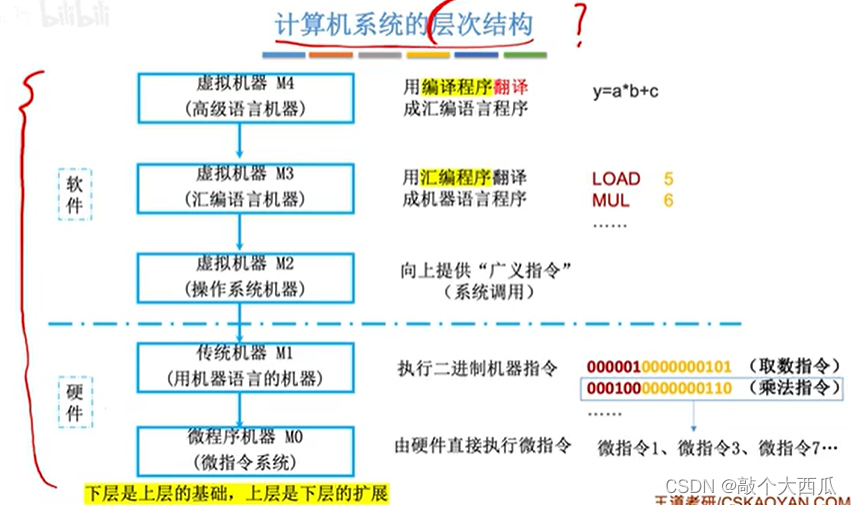

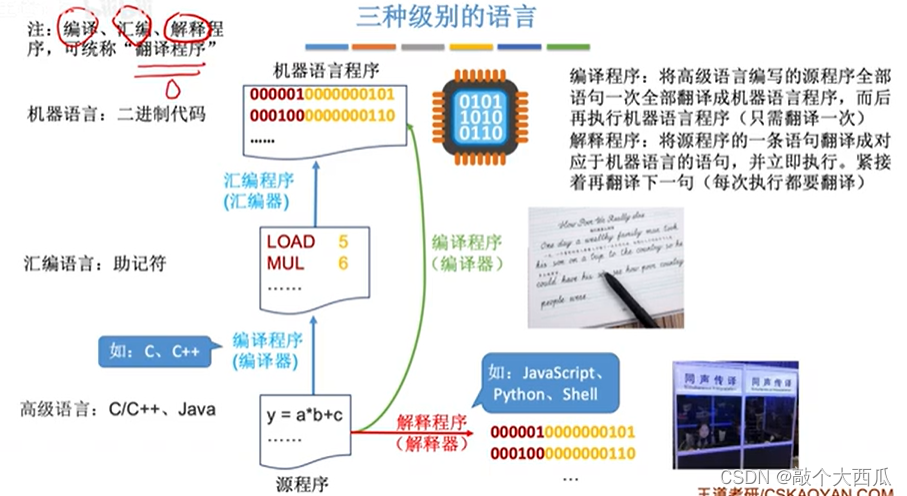

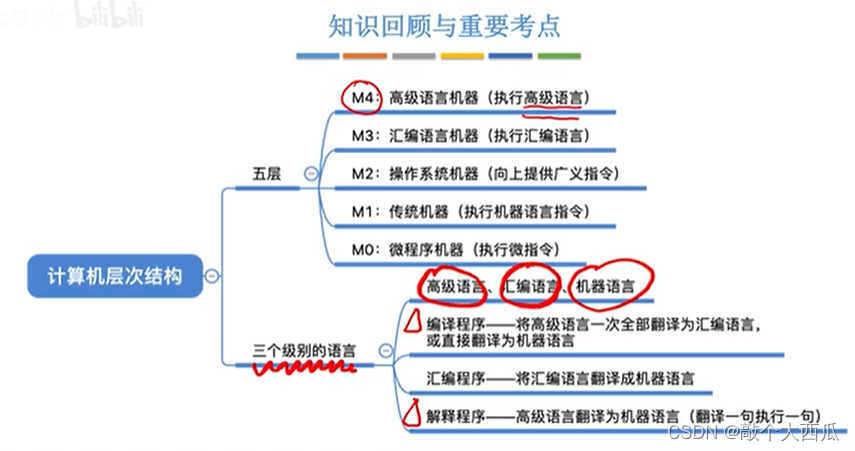

计算机系统的多级层次结构

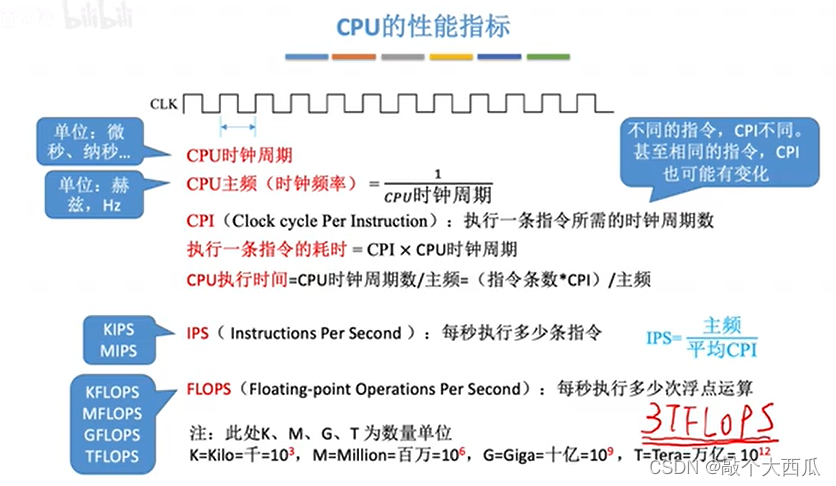

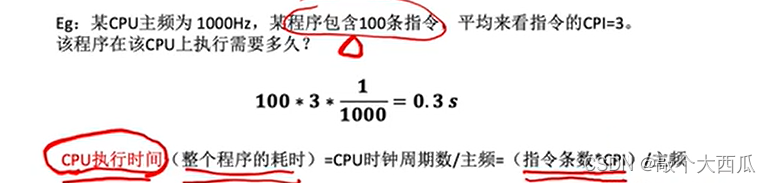

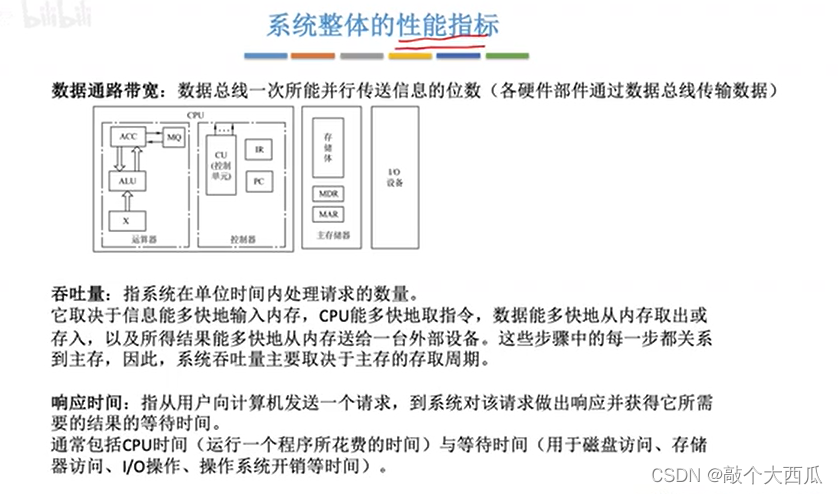

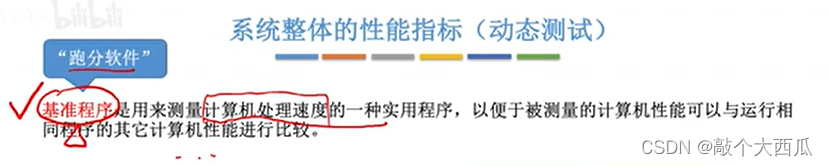

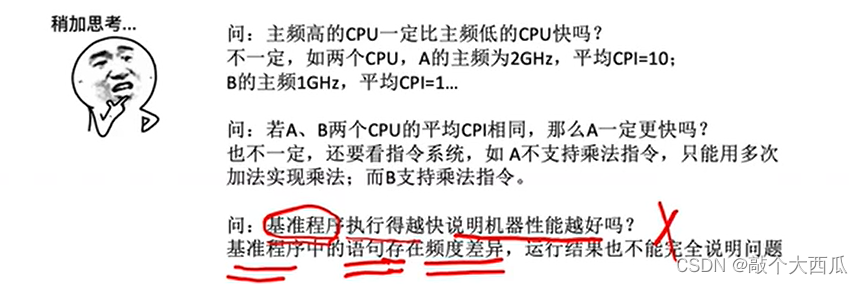

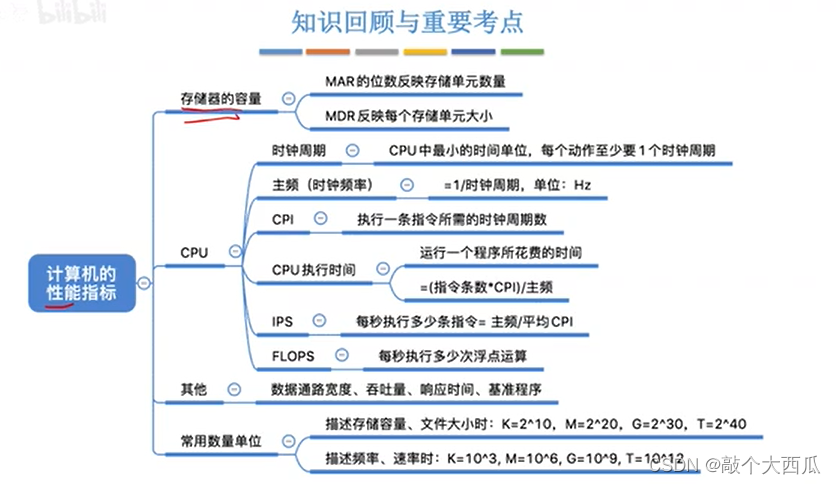

计算机性能指标

第二章 数据的表示和运算

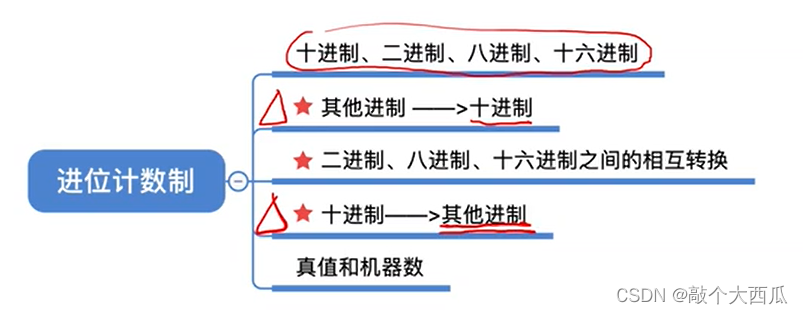

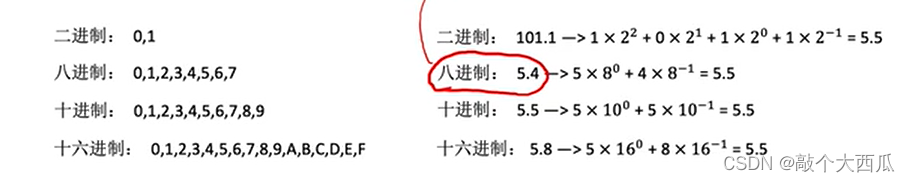

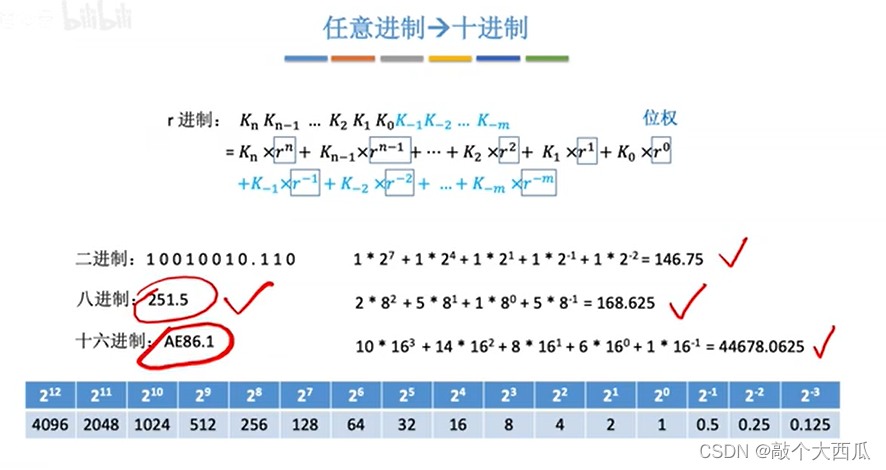

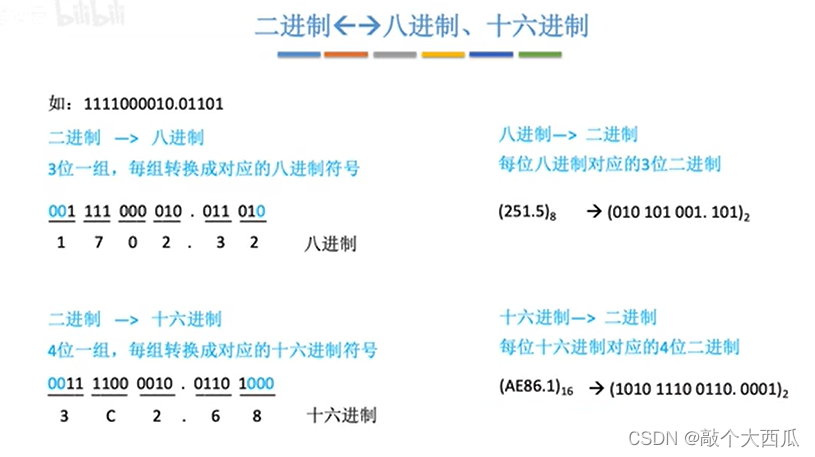

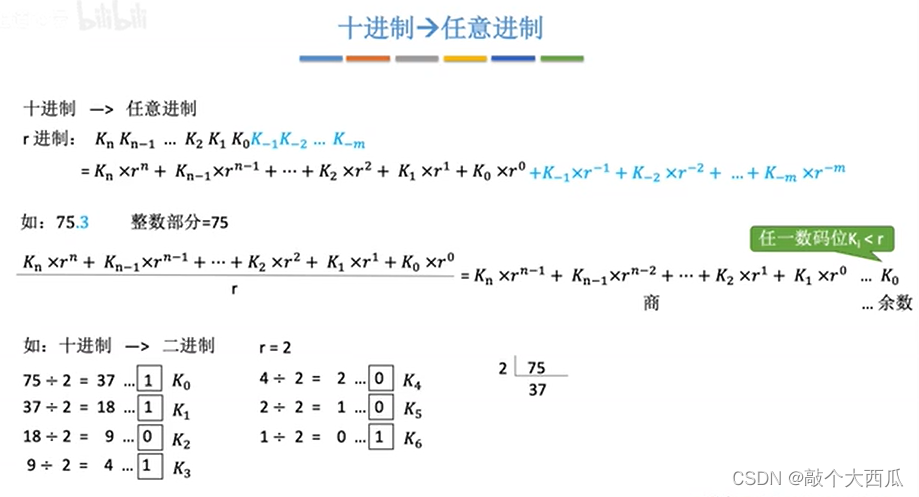

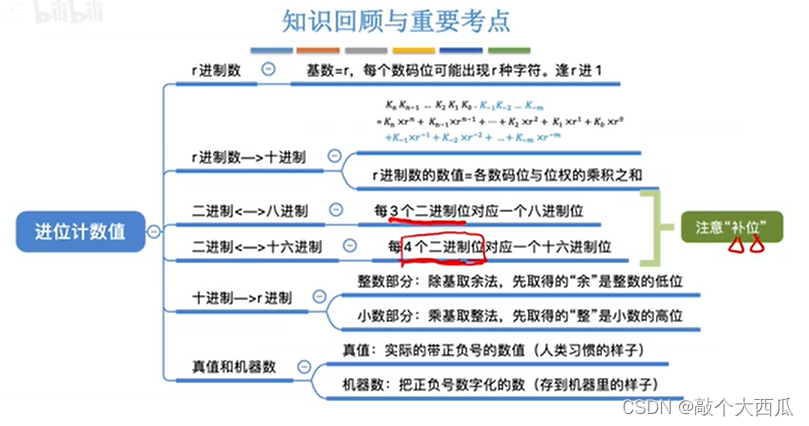

进位计数制

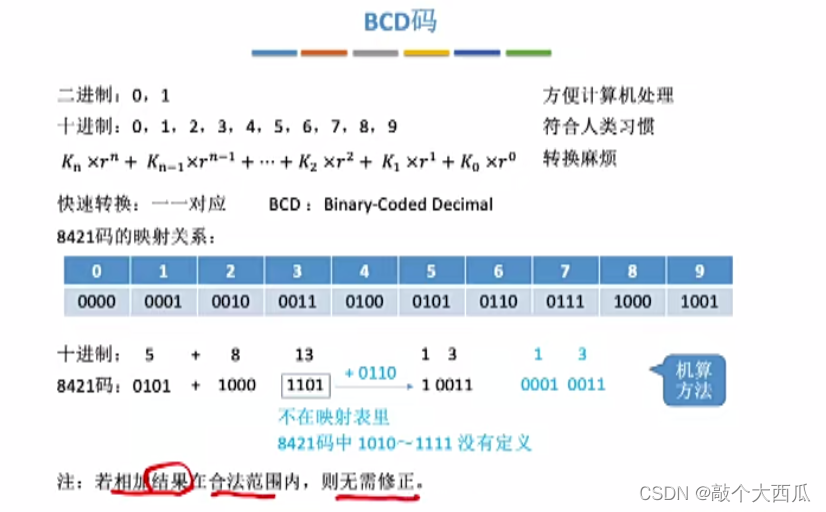

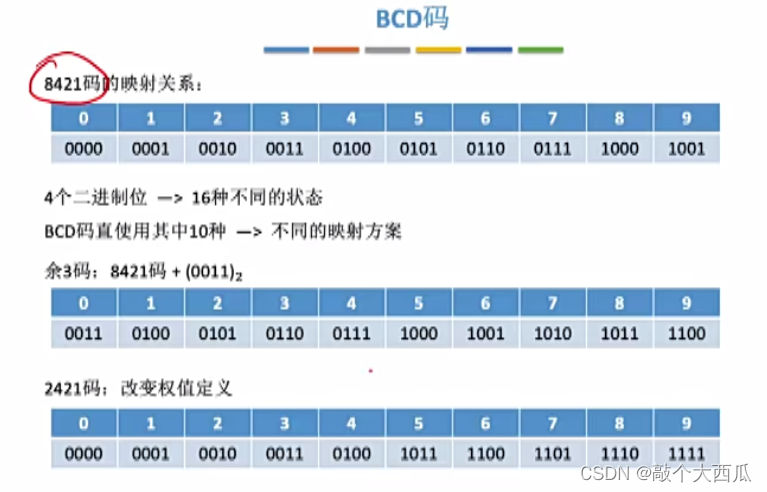

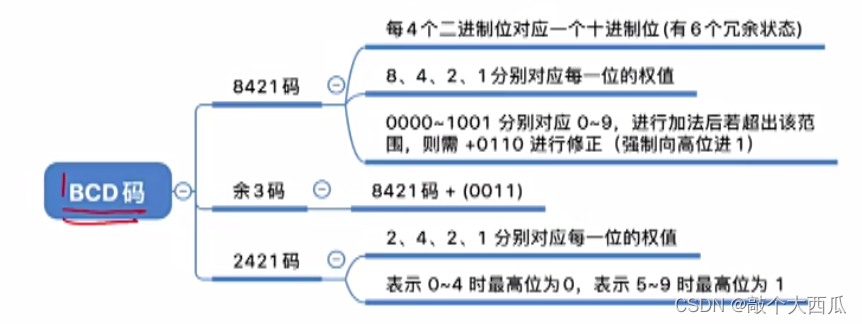

BCD码

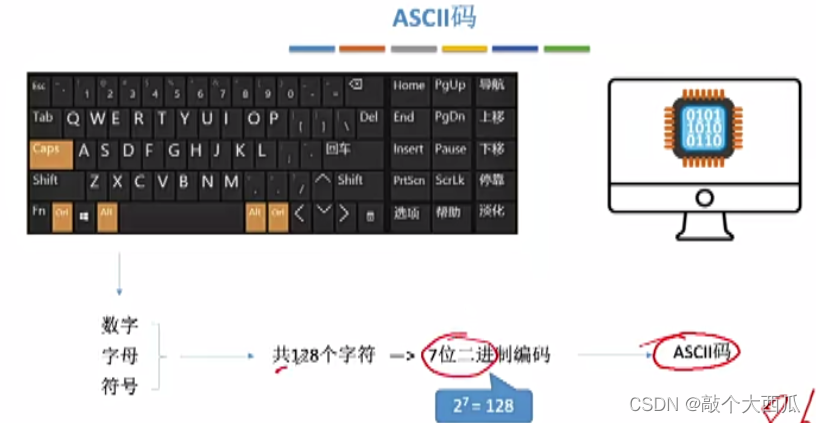

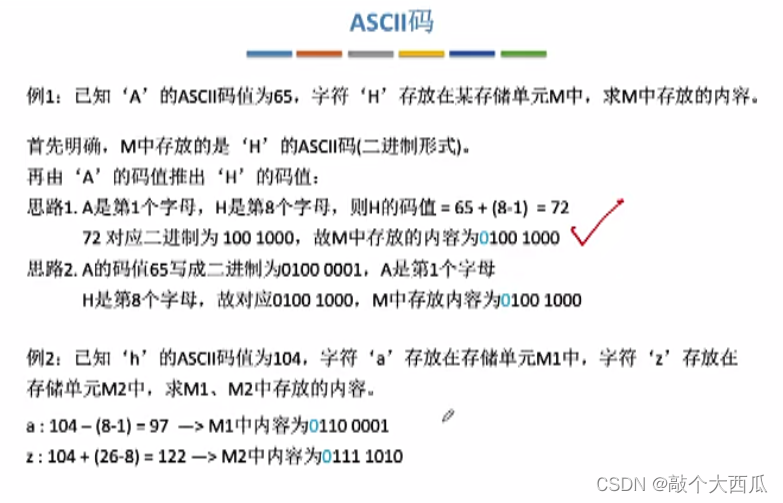

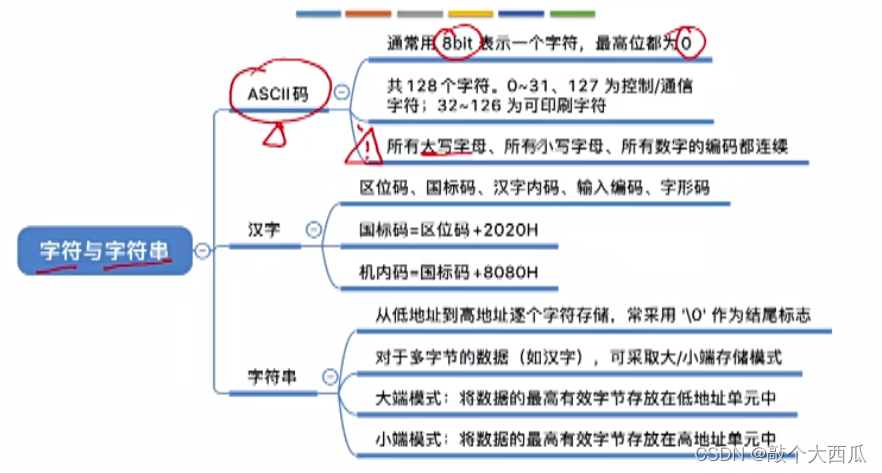

ASCII码

此处注意在存储单元中存放的只能是二进制代码

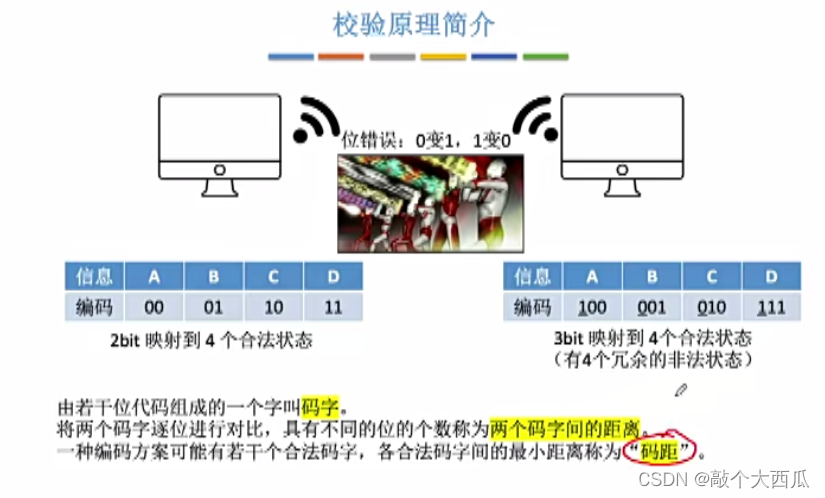

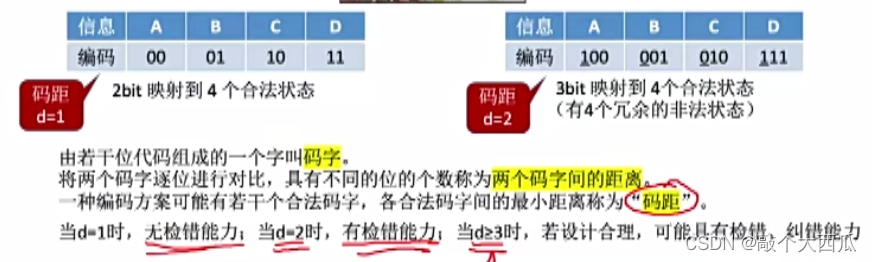

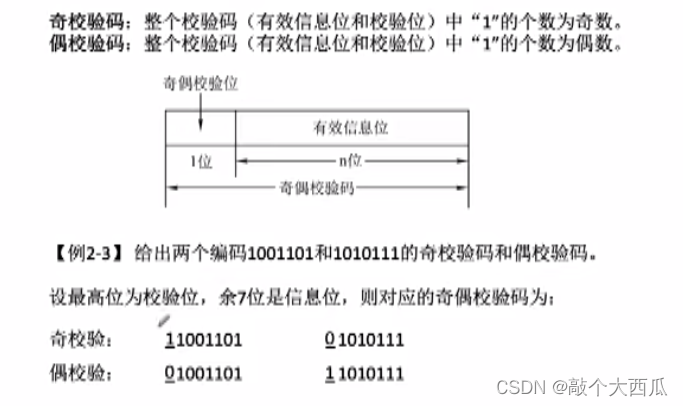

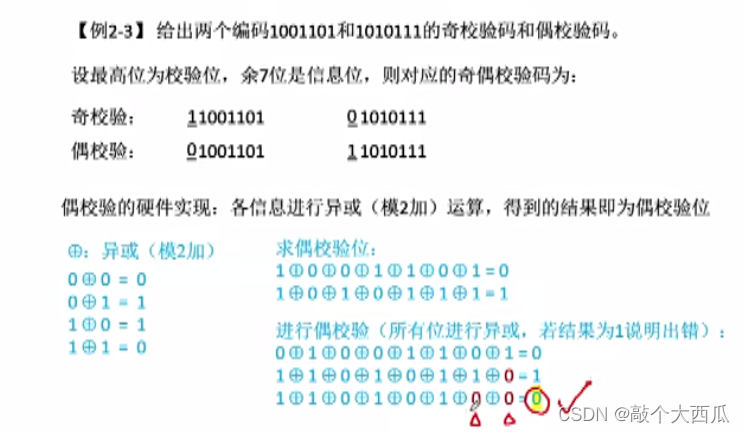

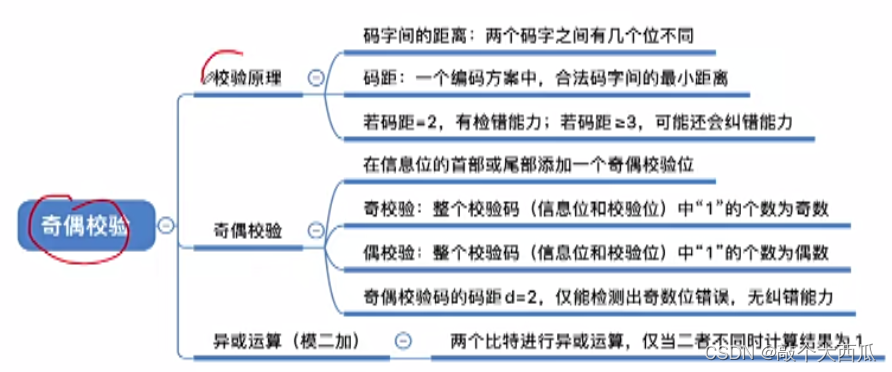

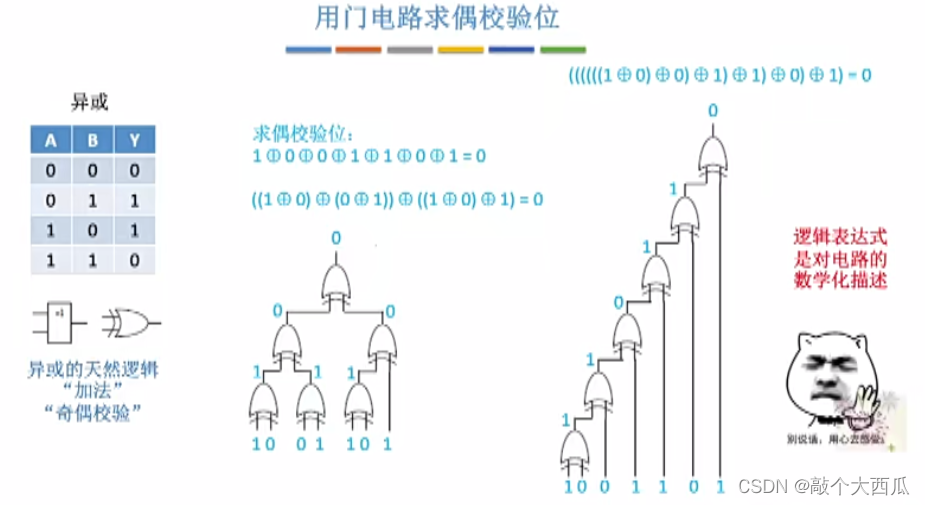

奇偶校验码

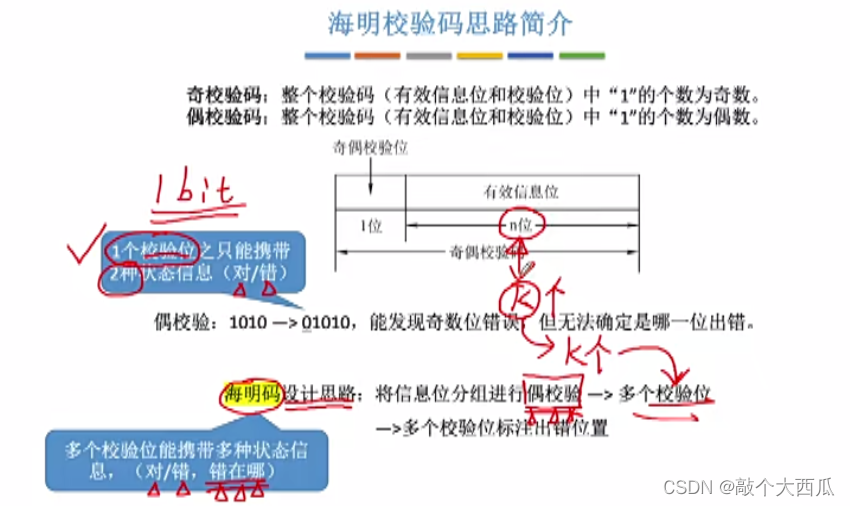

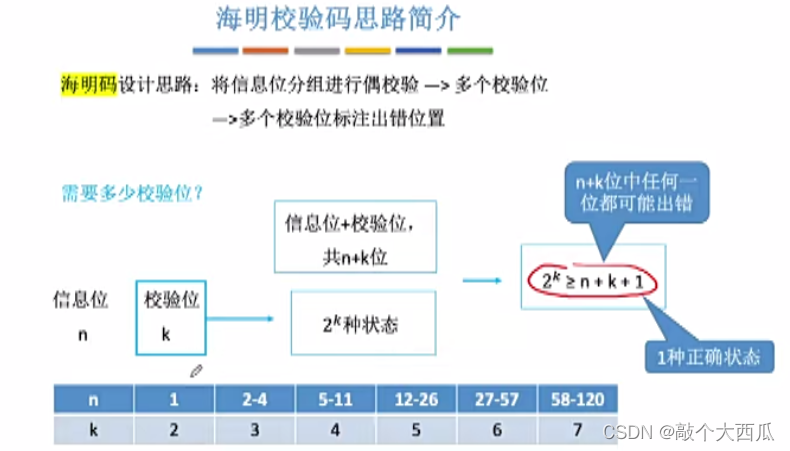

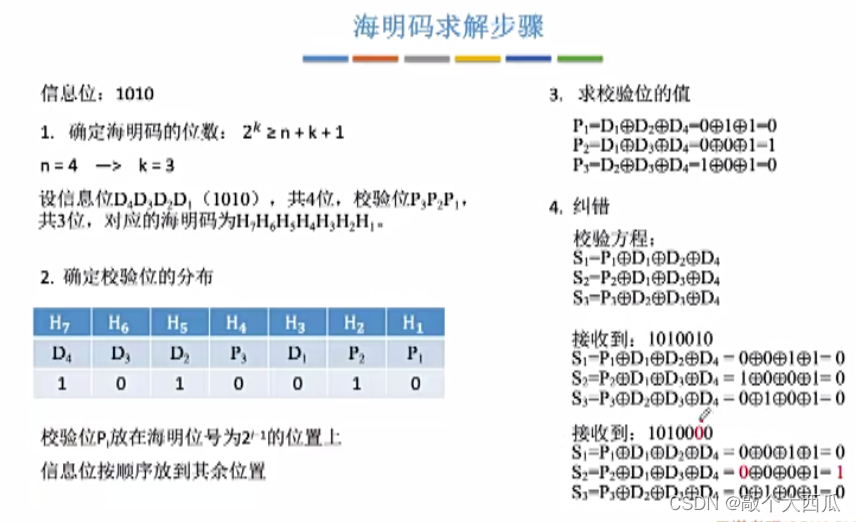

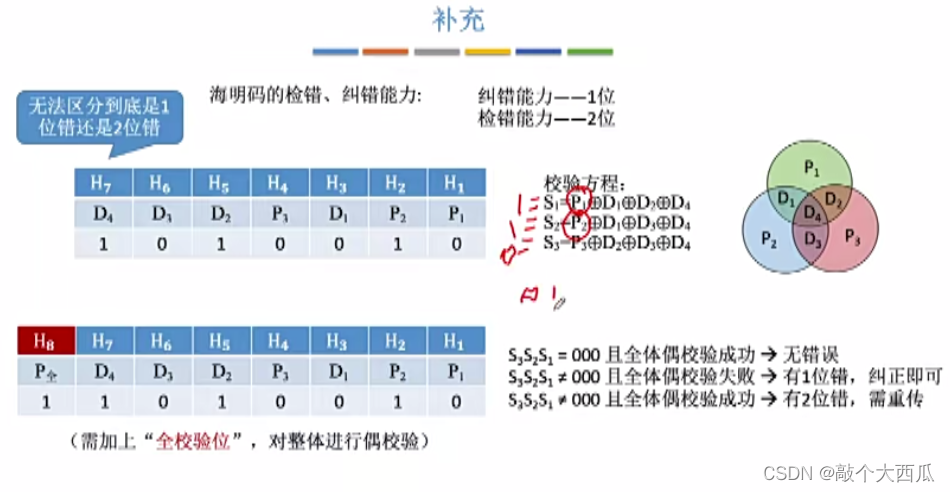

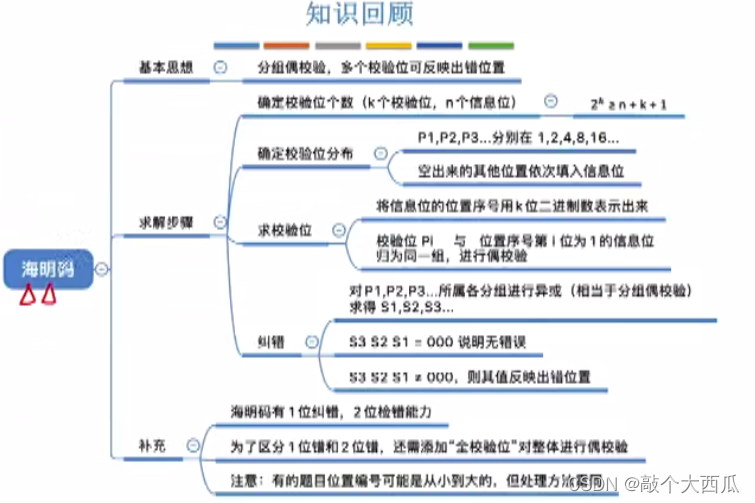

海明校验码

被校验数据位的海明号等于校验该数据位的各校验位海明号之和

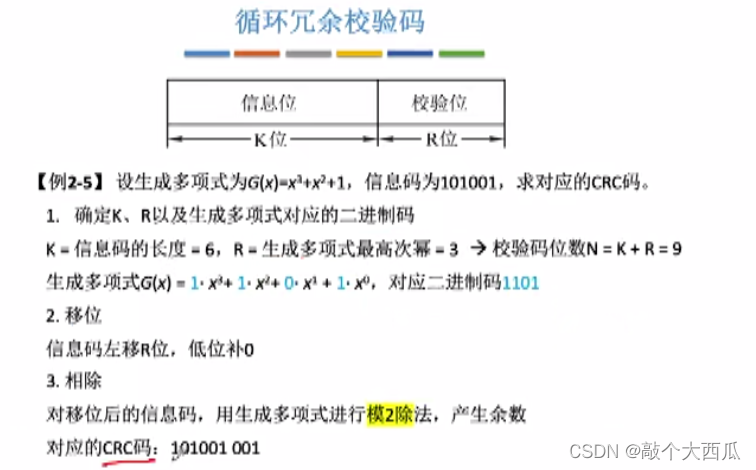

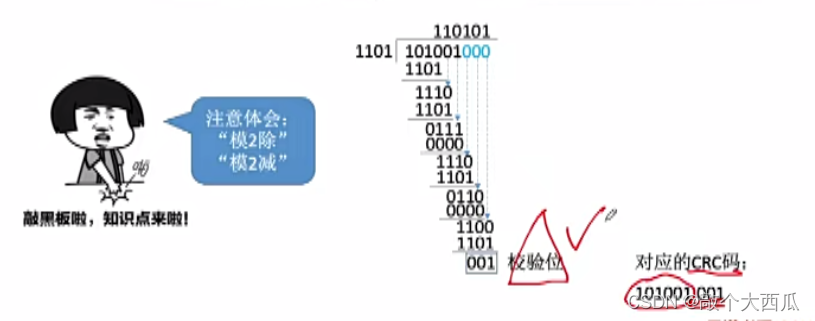

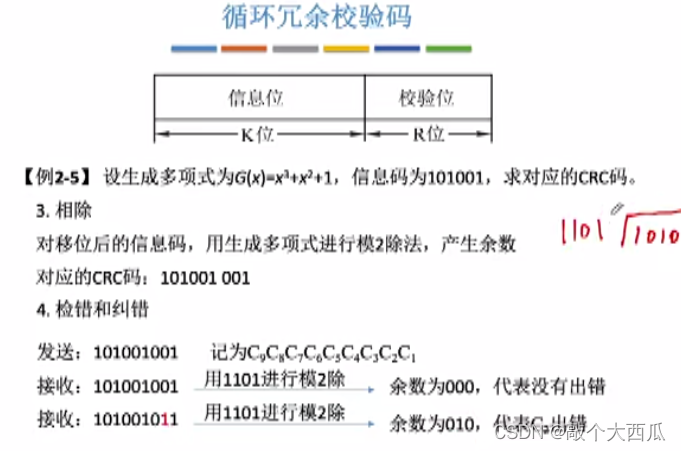

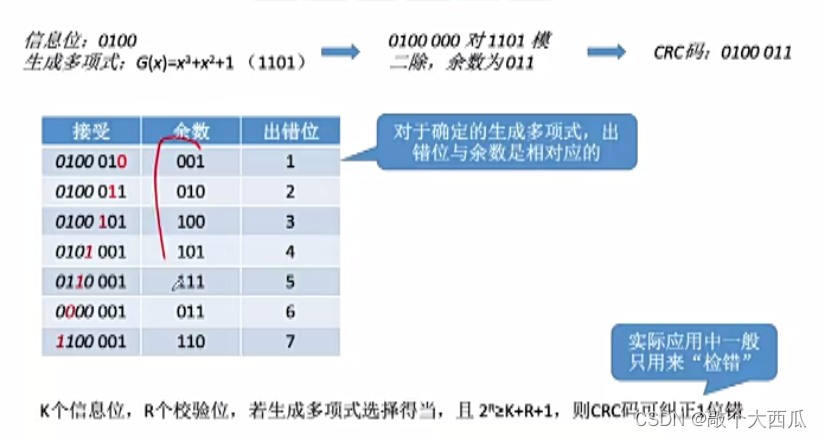

CRC循环冗余校验码

此处注意摸二除法是怎样工作的,

此处注意摸二除法是怎样工作的

二进制 下的除法,模2除法与算术除法类似,但每一位除的结果不影响其它位,即不向上一位借位,所以实际上就是异或

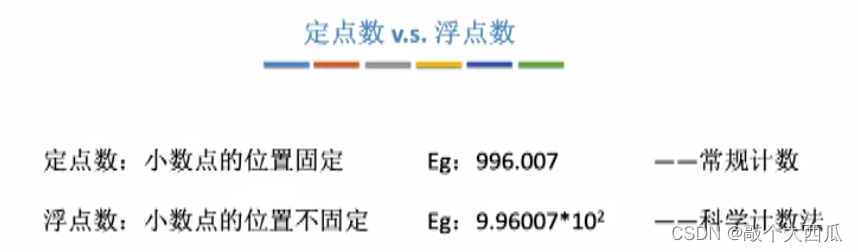

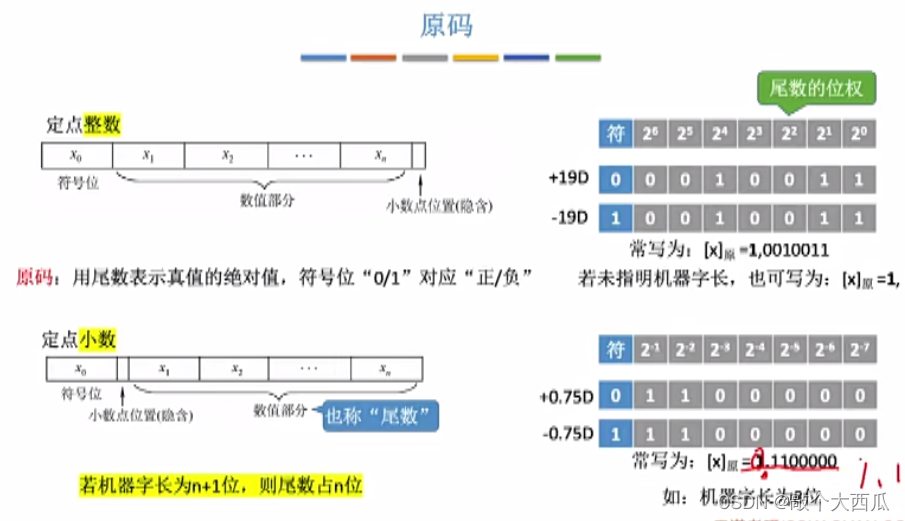

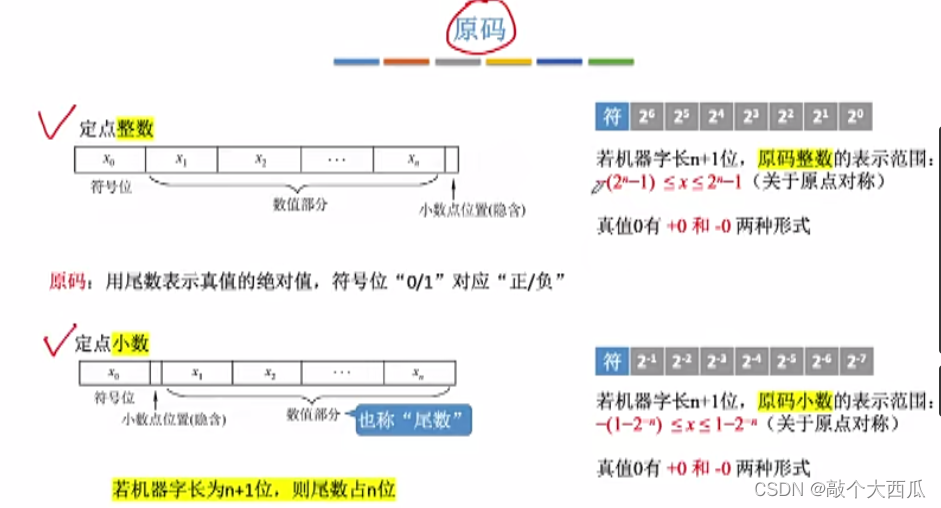

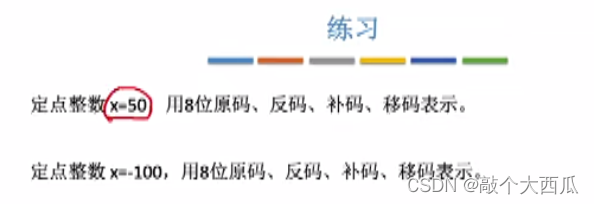

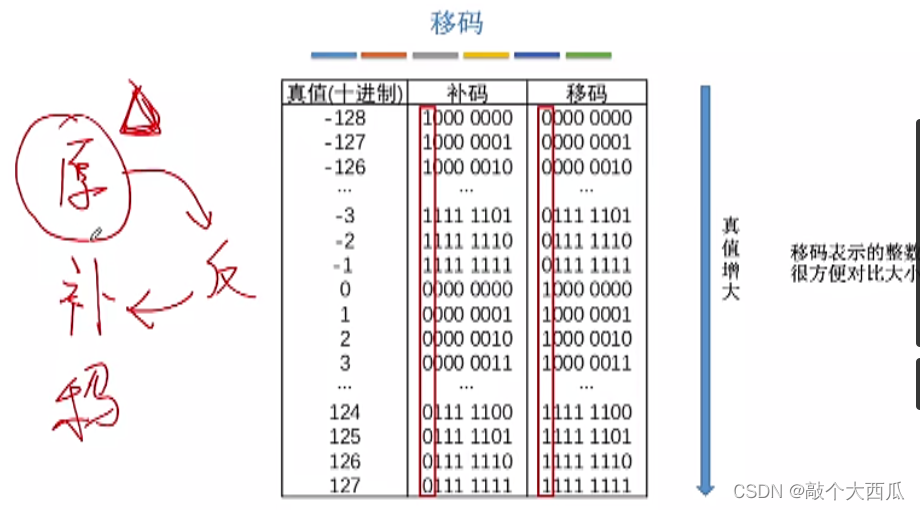

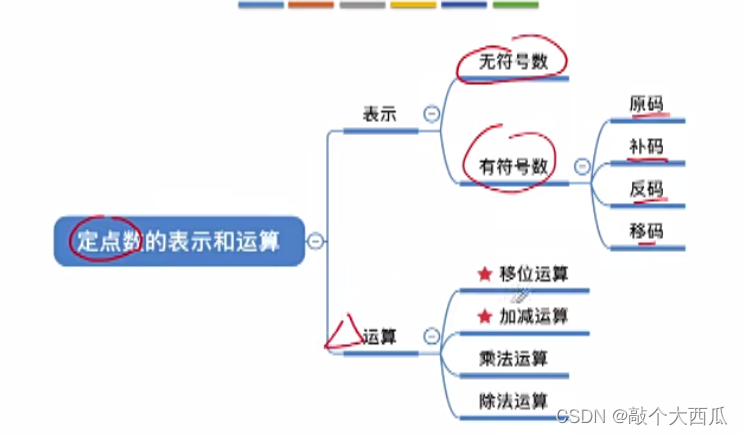

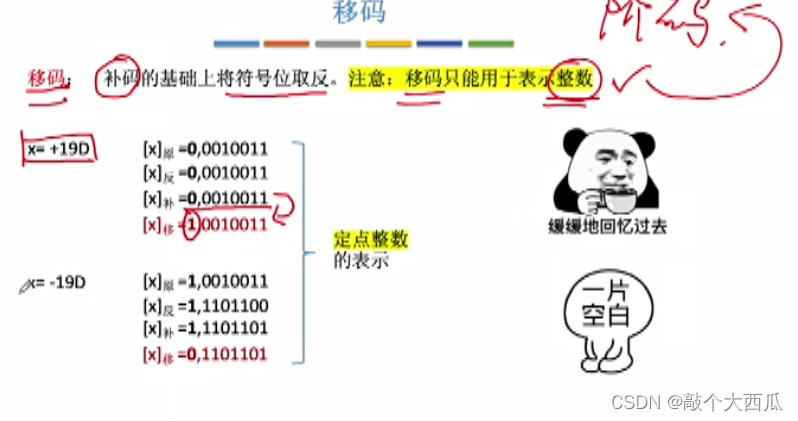

定点数表示

无符号数:整个机器字长的全部二进制位均为数值位,没有符号位,相当于数的绝对值,通常只有无符号整数,没有无符号小数,n位无符号数的表示范围为0到2的n次方减一,

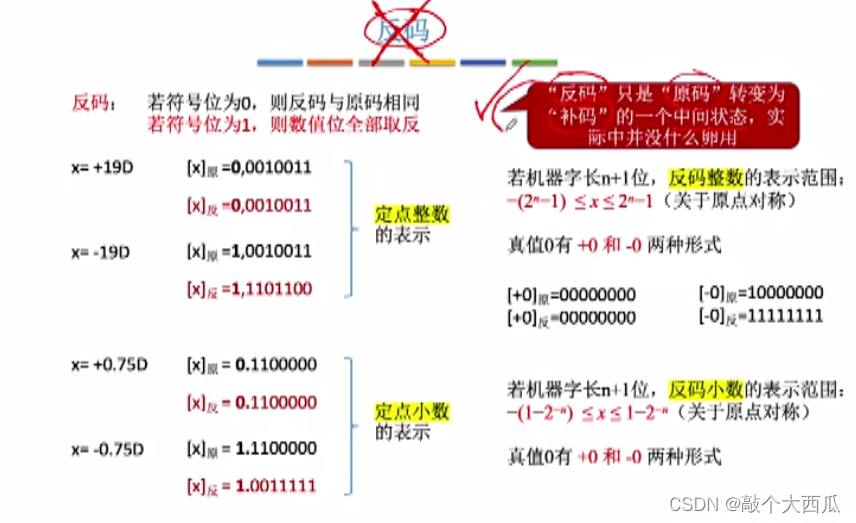

各种码的作用

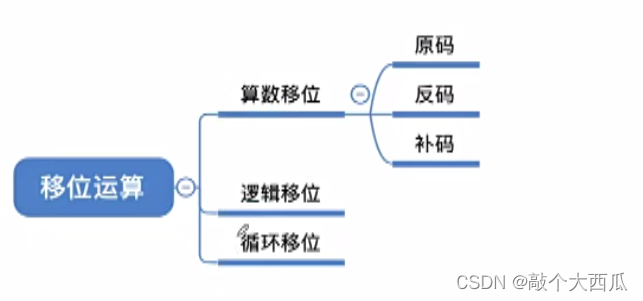

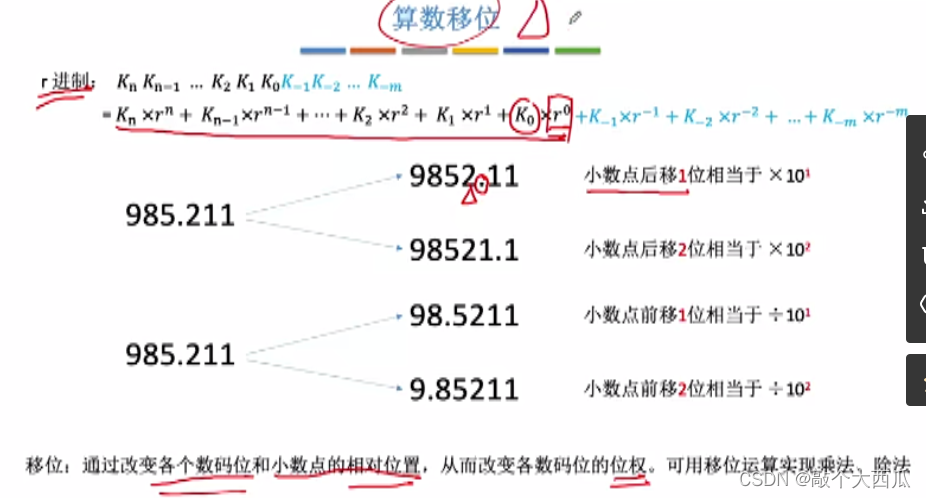

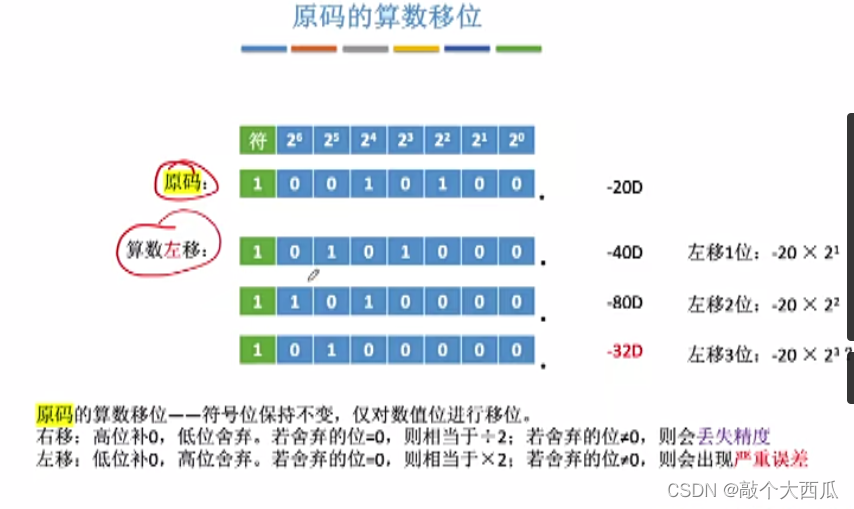

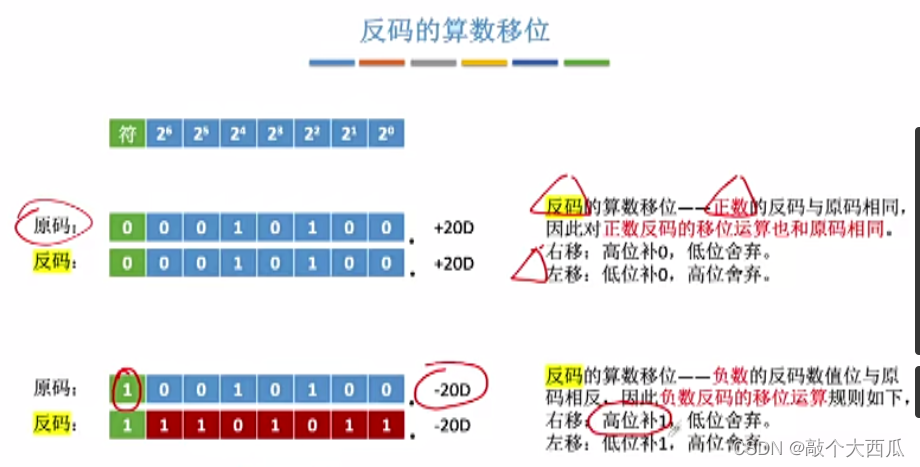

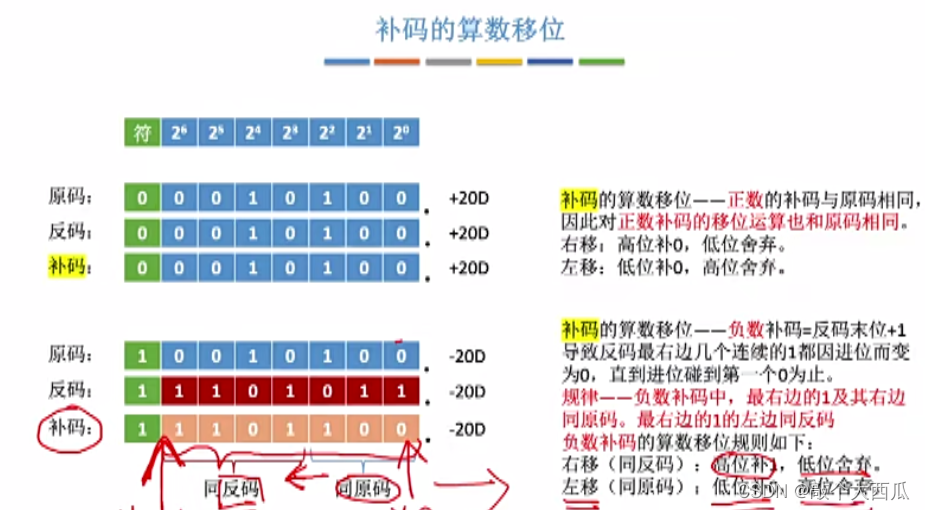

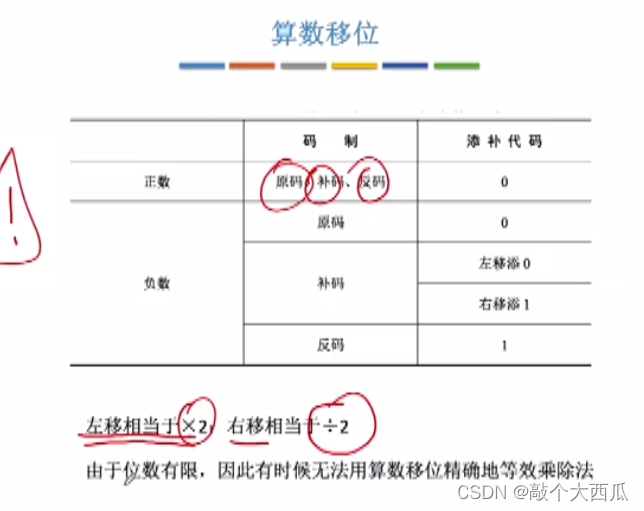

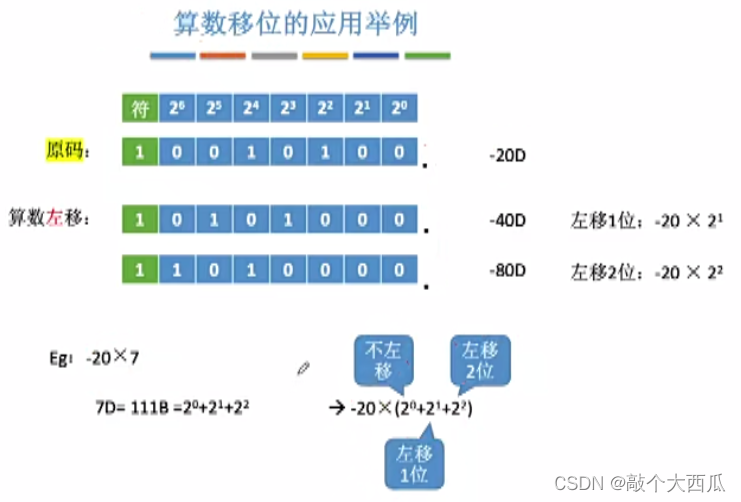

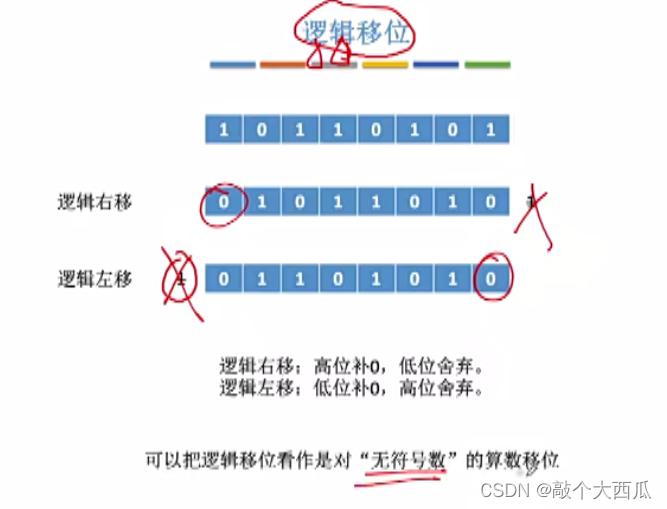

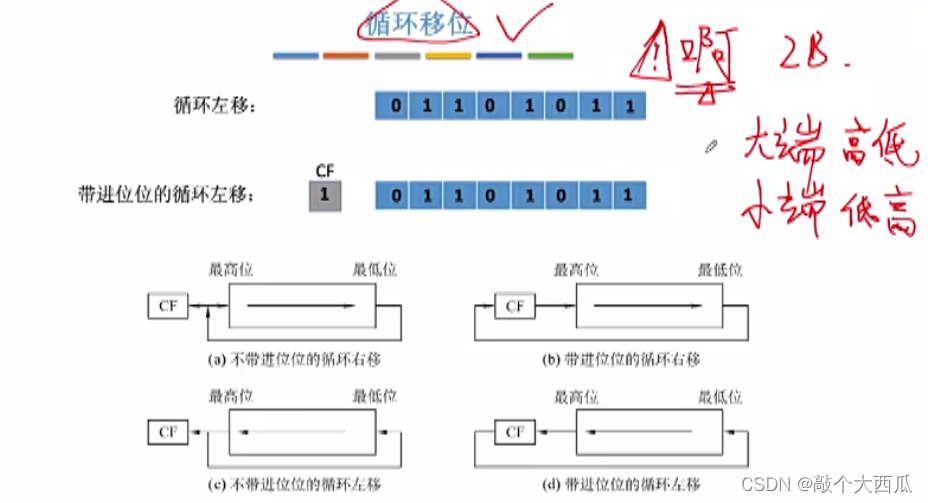

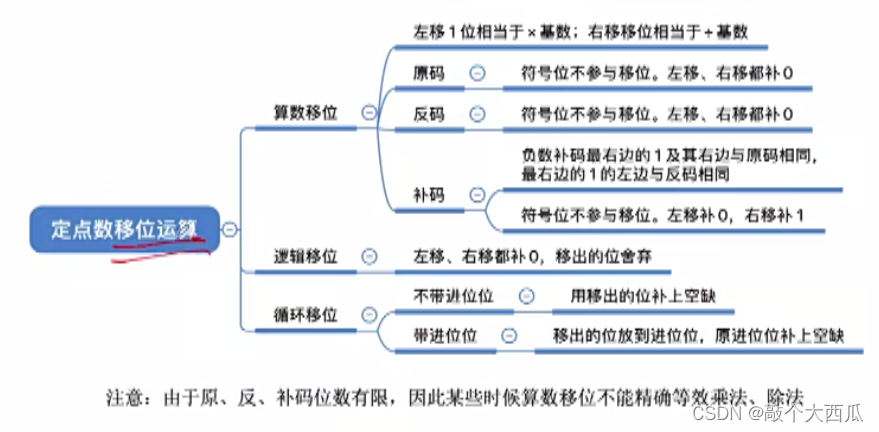

移位运算

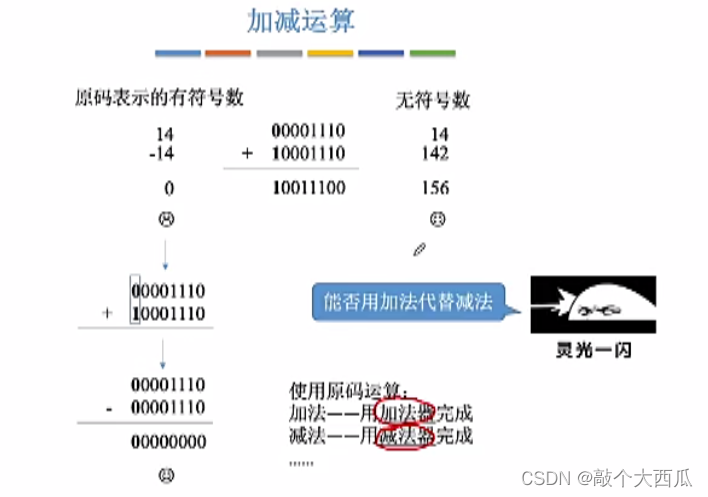

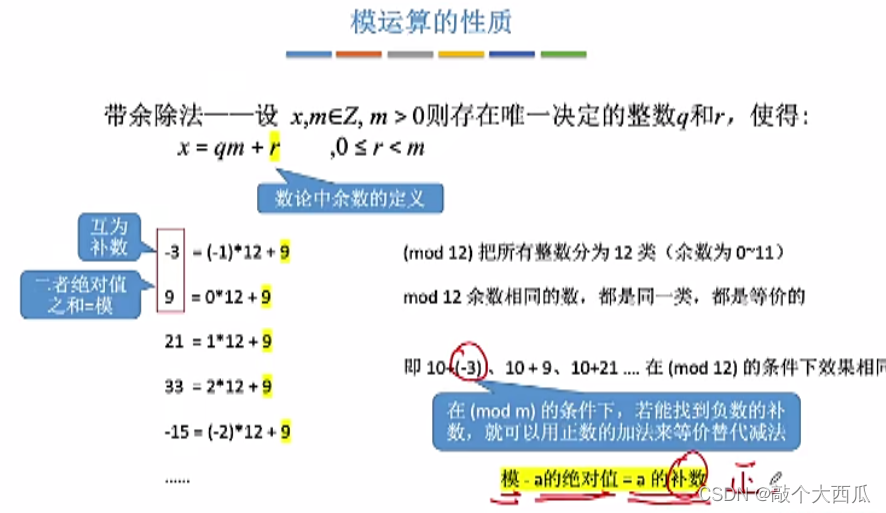

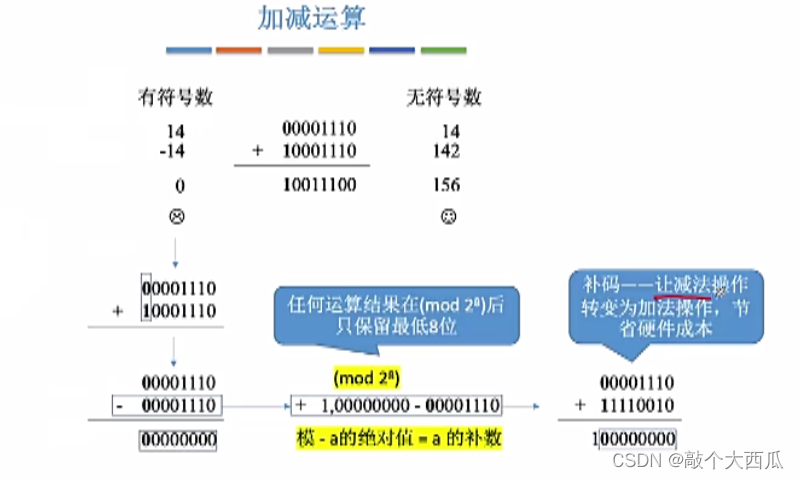

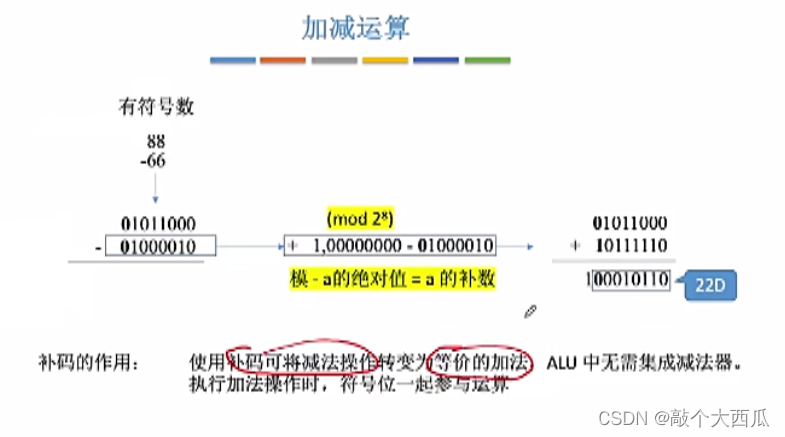

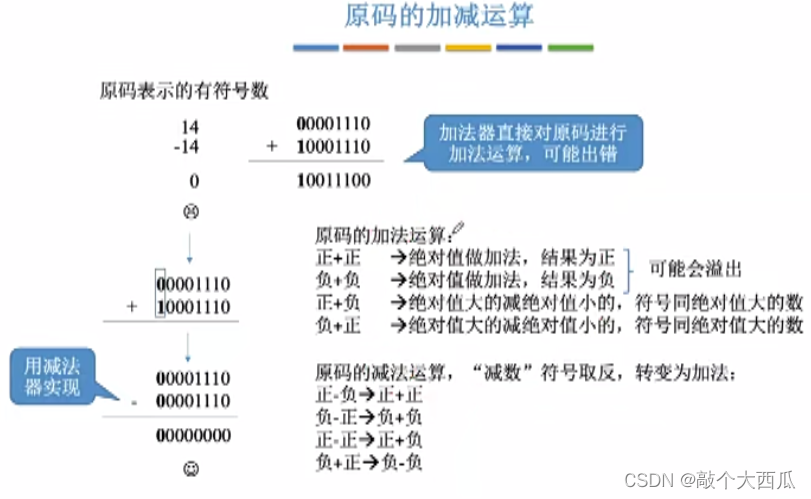

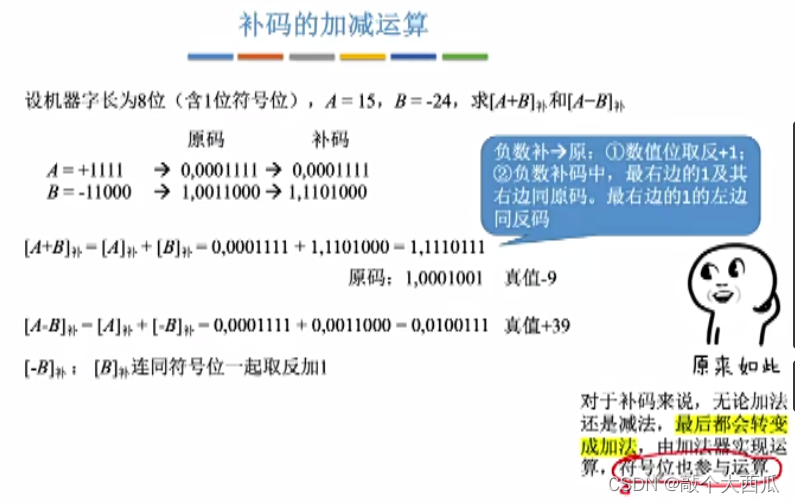

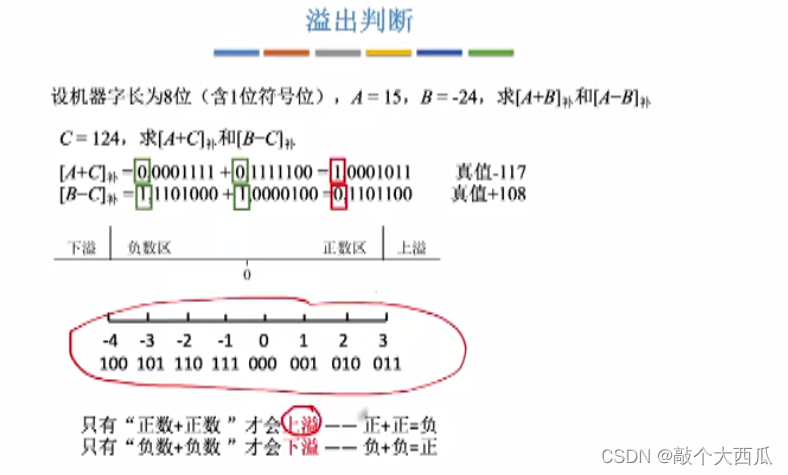

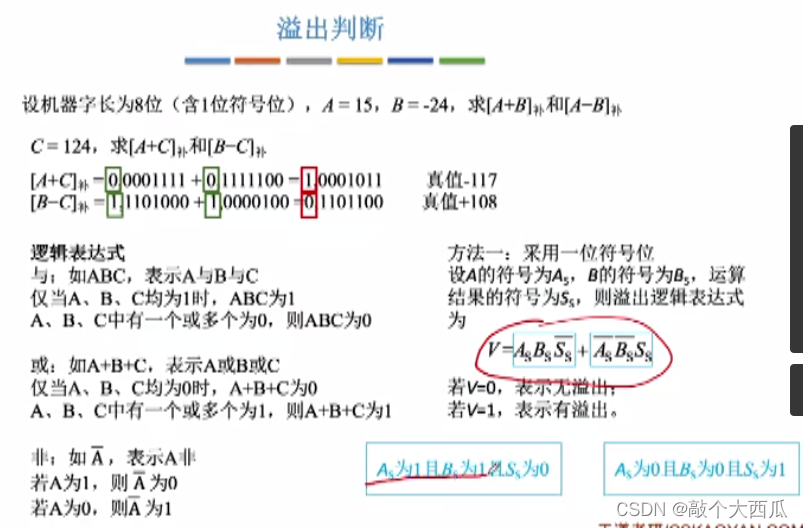

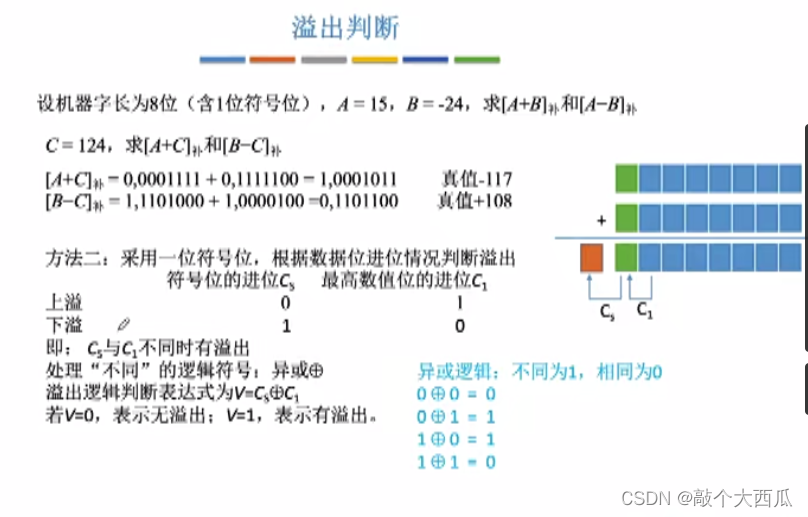

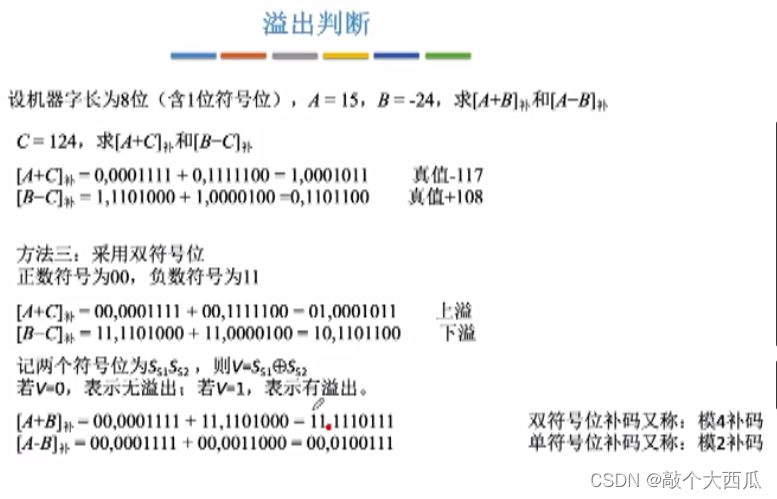

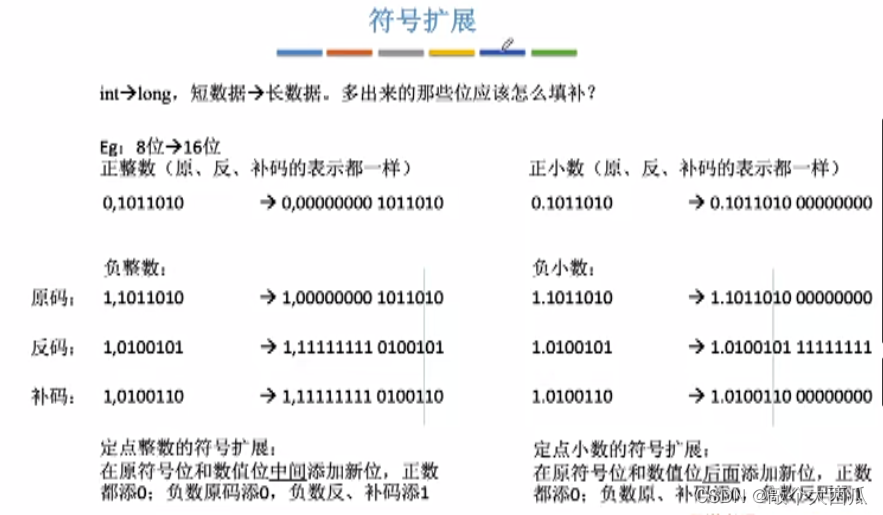

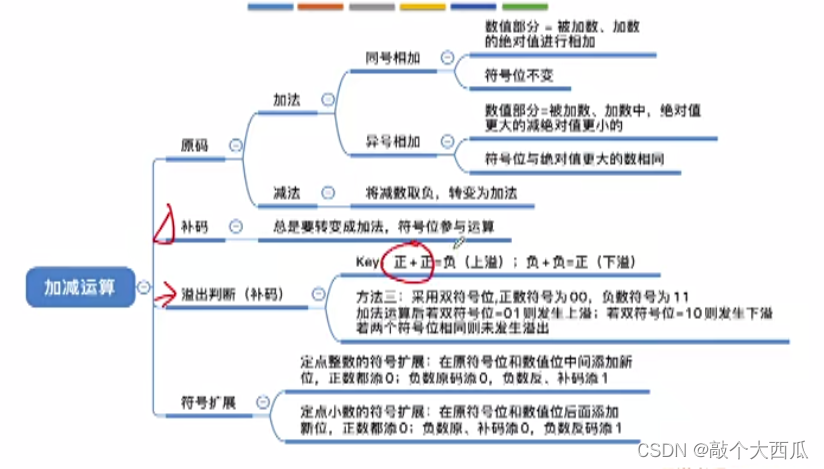

加减运算和溢出判断

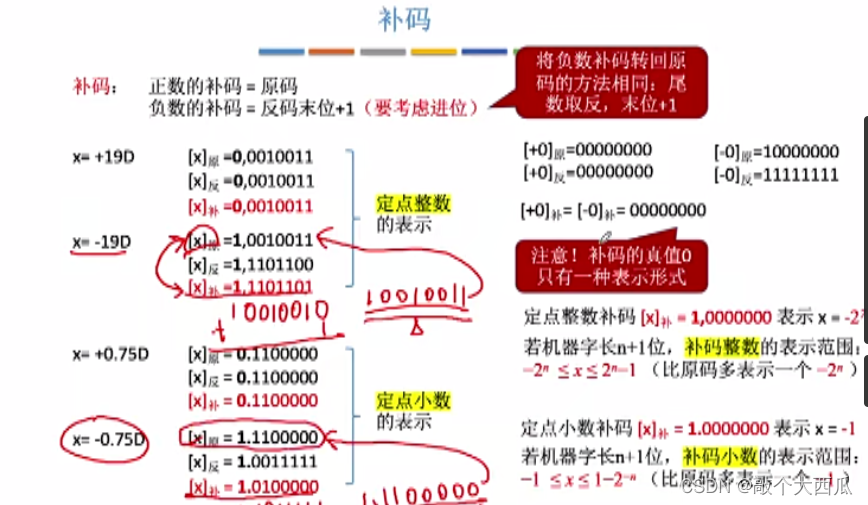

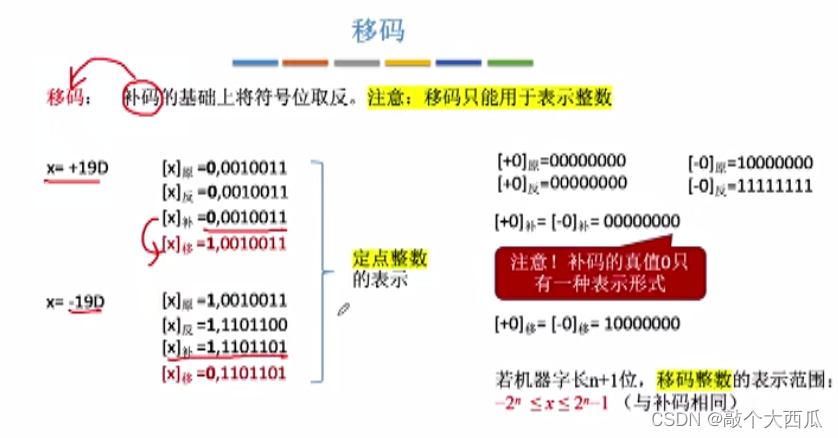

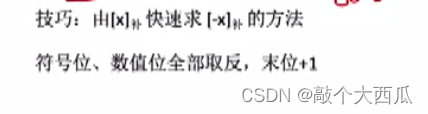

不要只记得取反加一,正数的原码,反码,补码都是本身

定点数

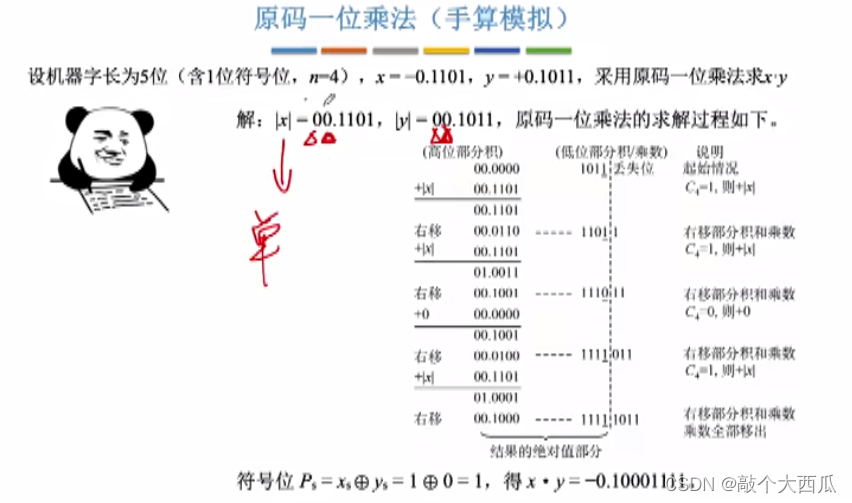

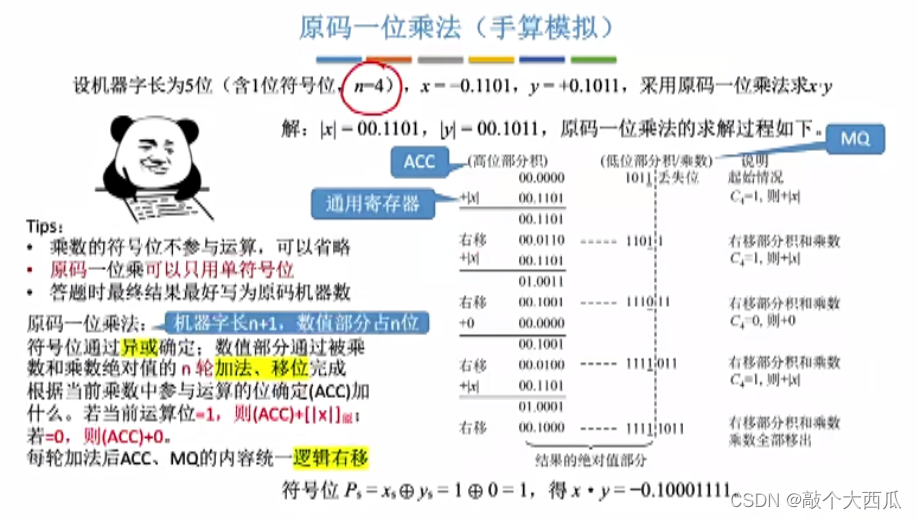

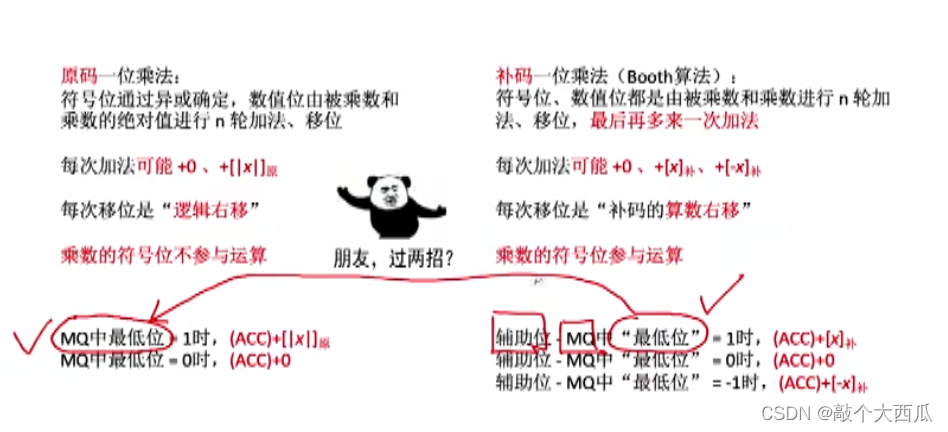

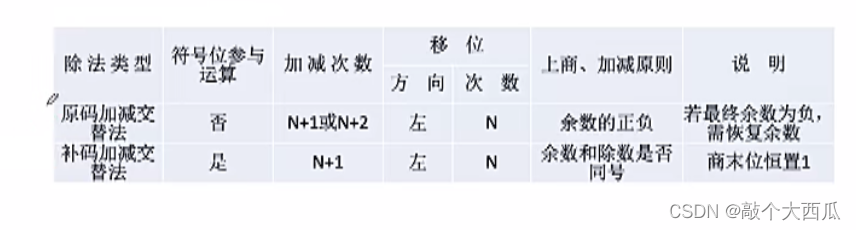

原码乘法运算

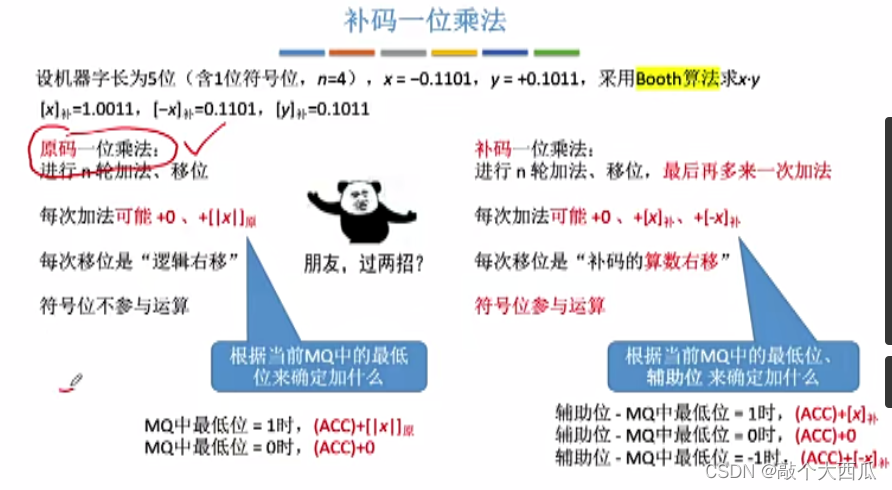

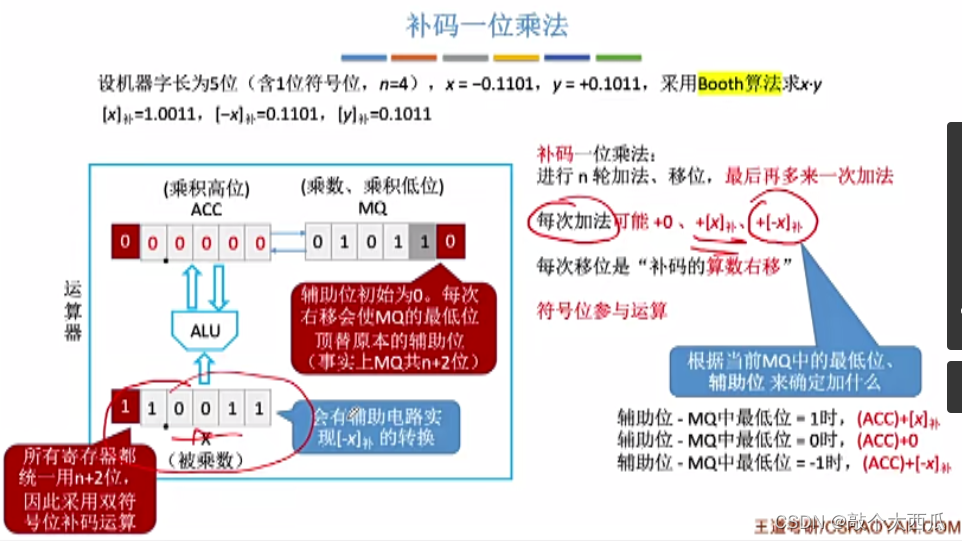

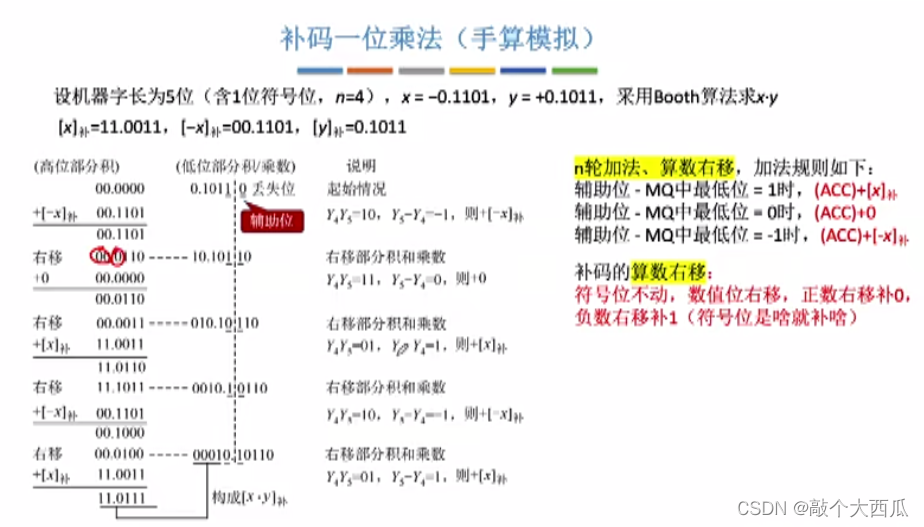

补码乘法运算

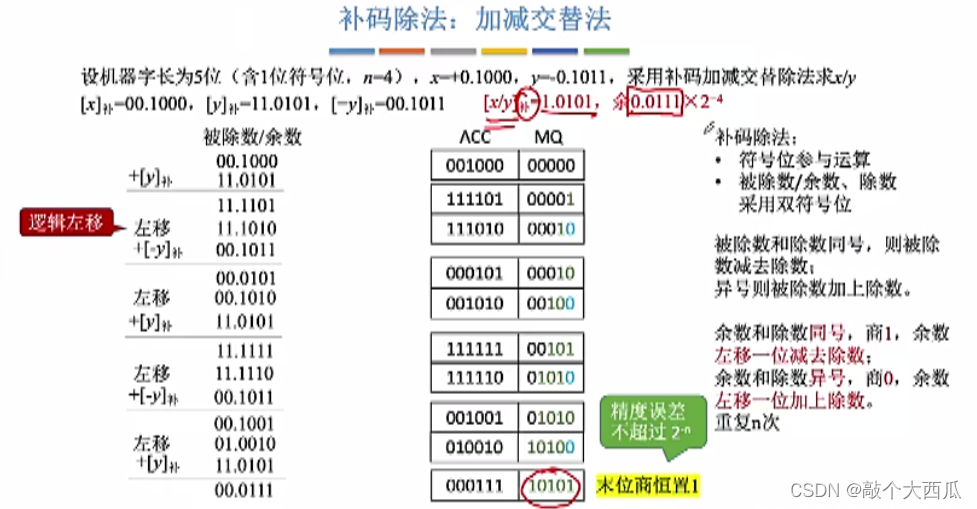

补码一位乘法难以理解,需要是手动实现,难点,难点

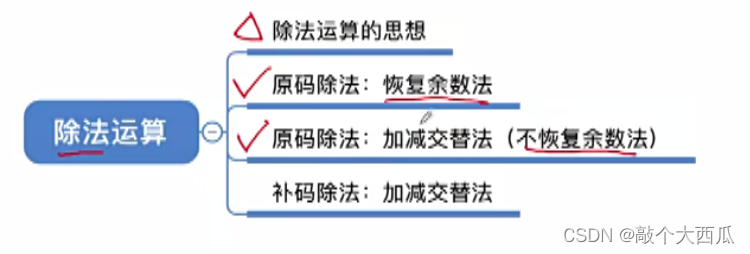

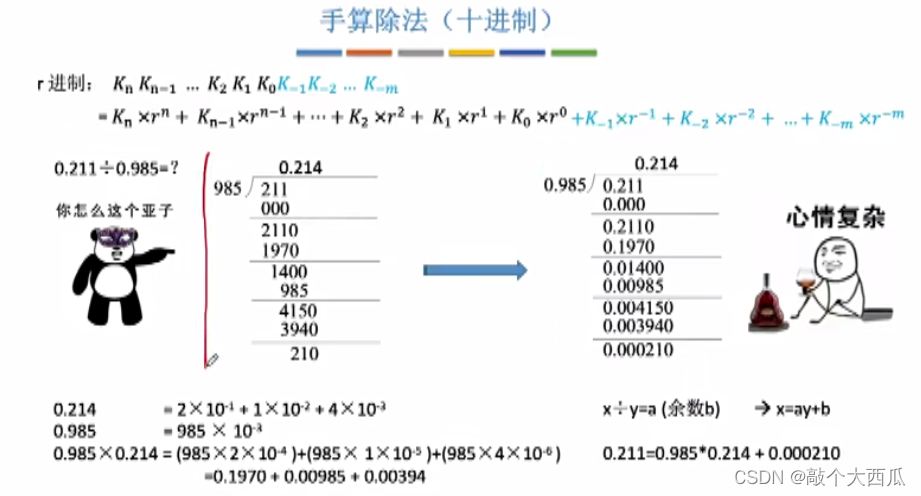

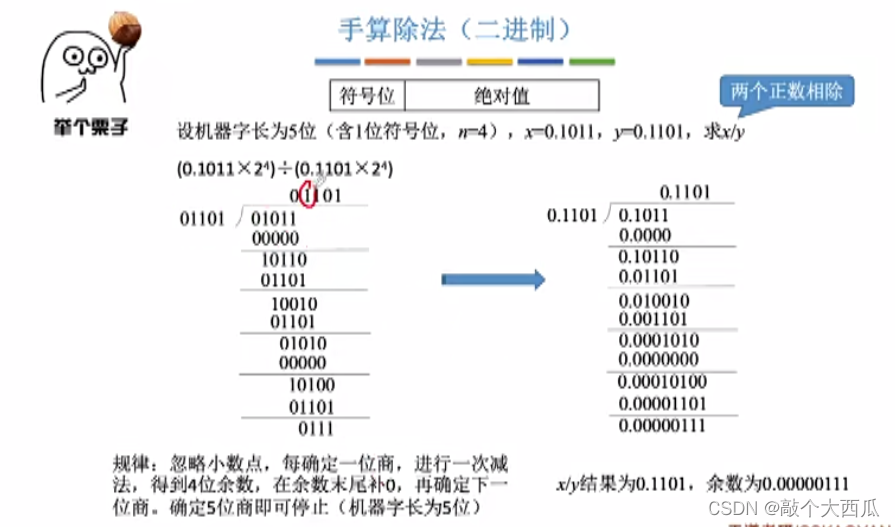

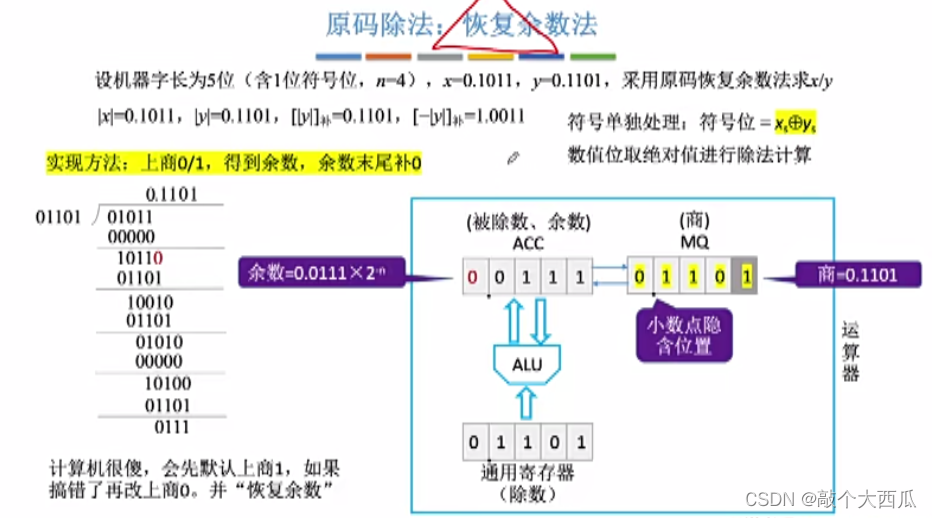

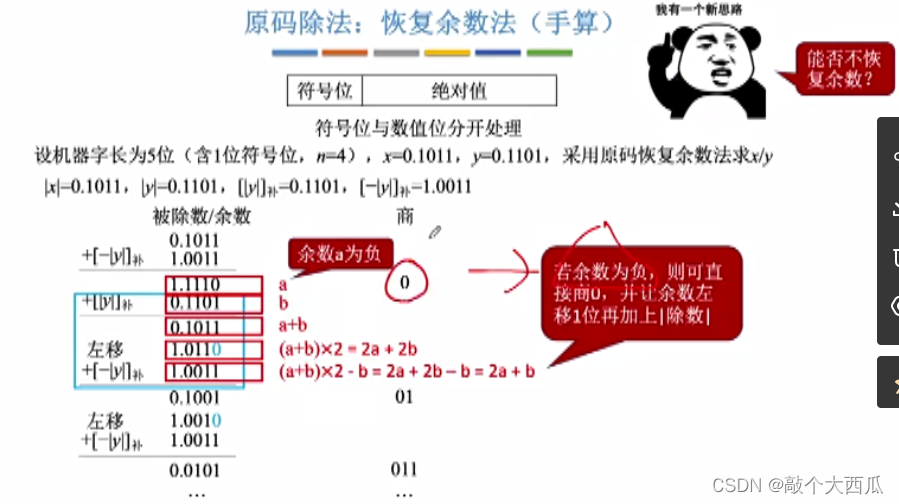

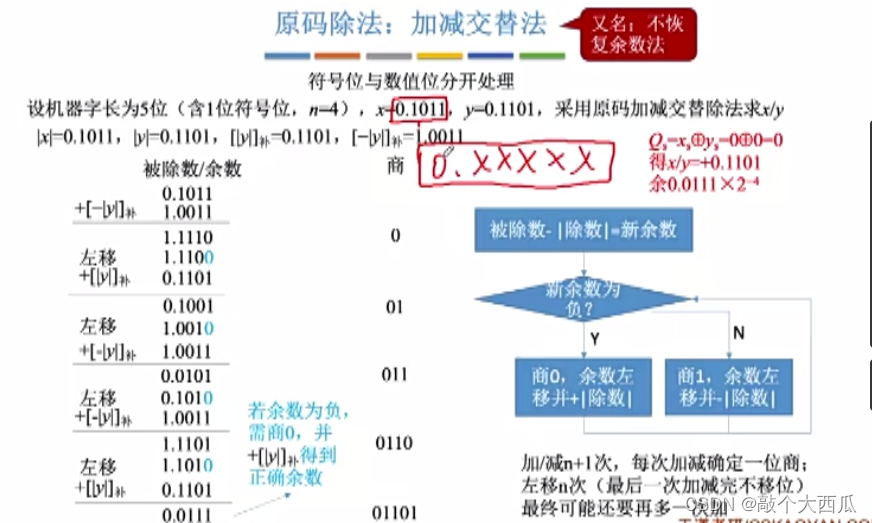

定点数 原码除法

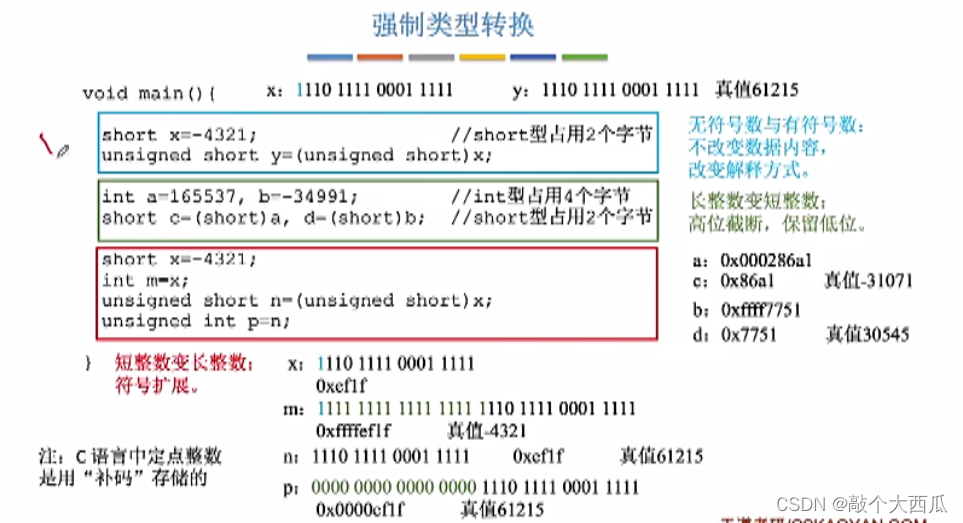

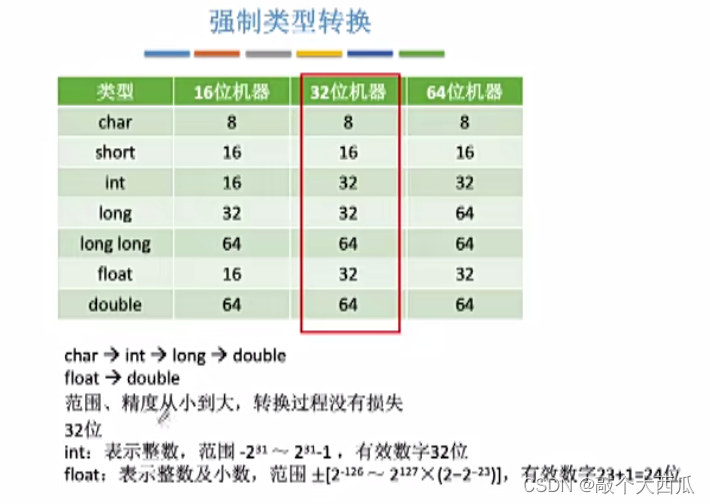

强制类型转换

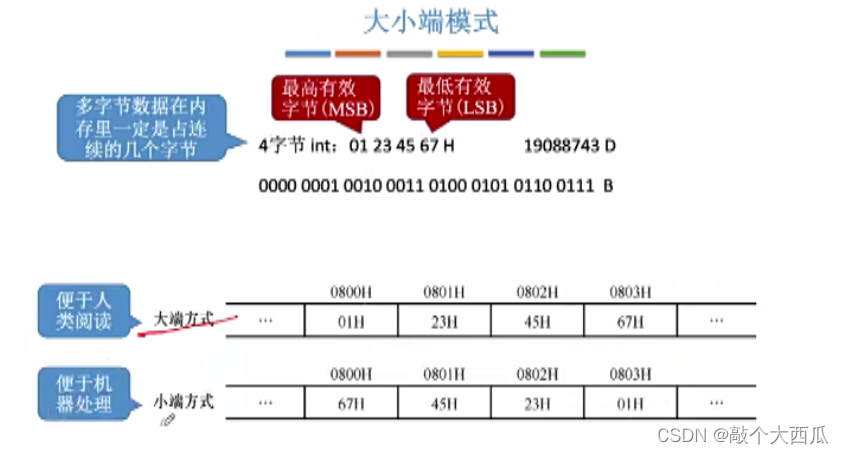

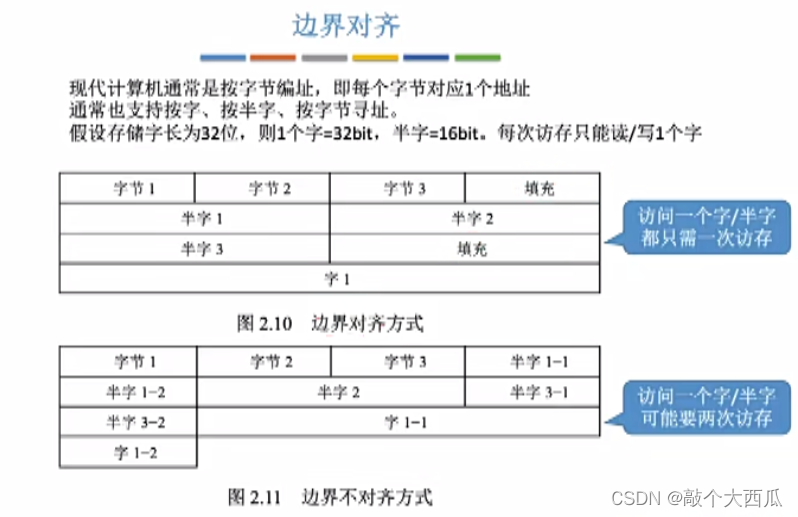

数据的存储和排列

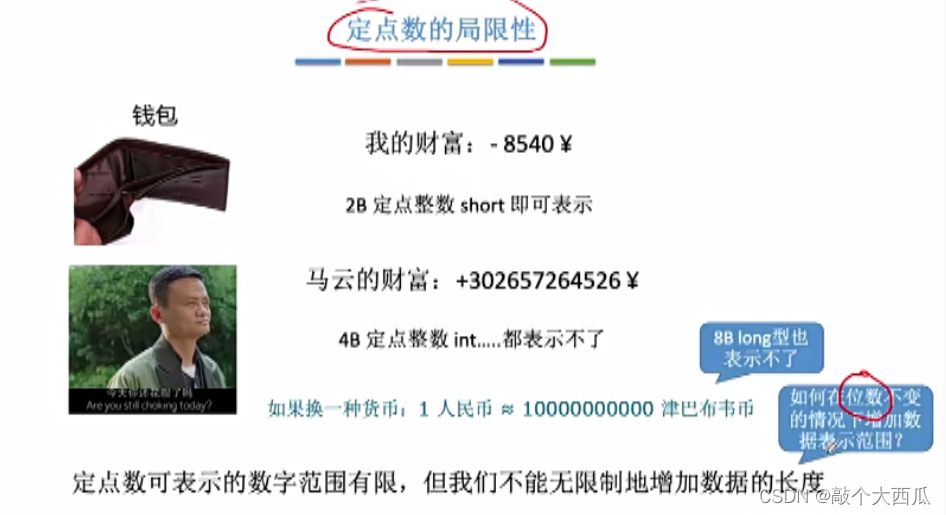

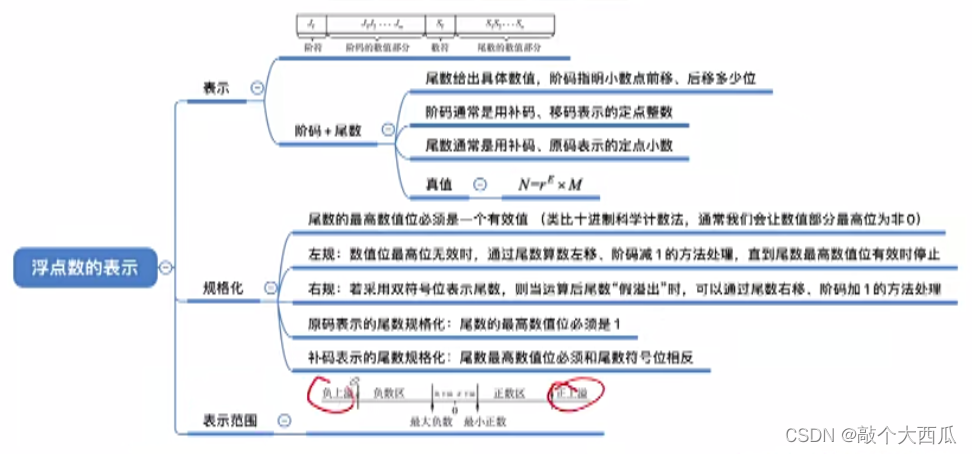

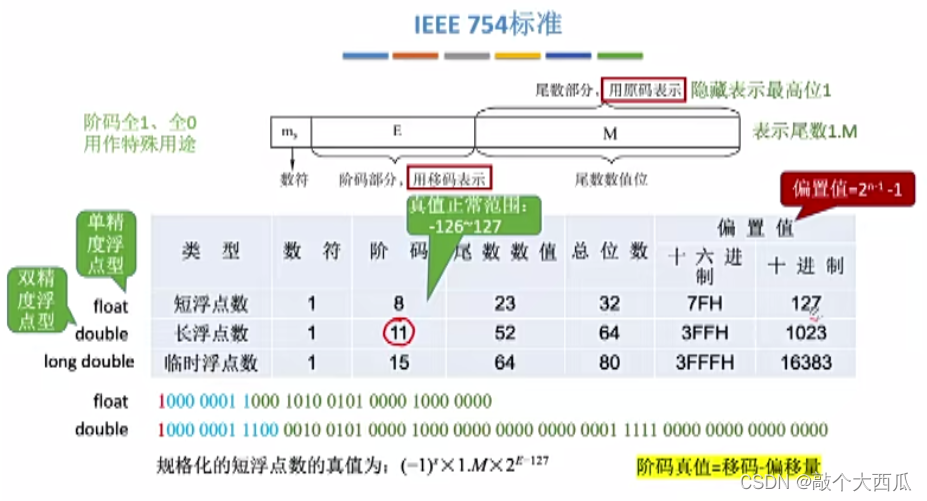

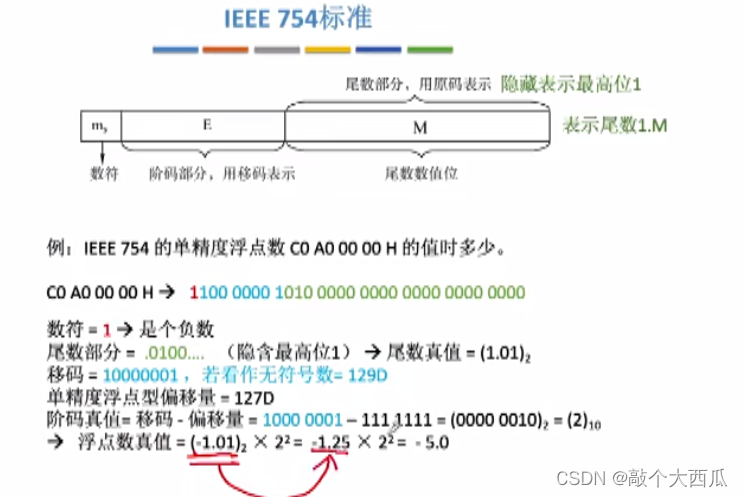

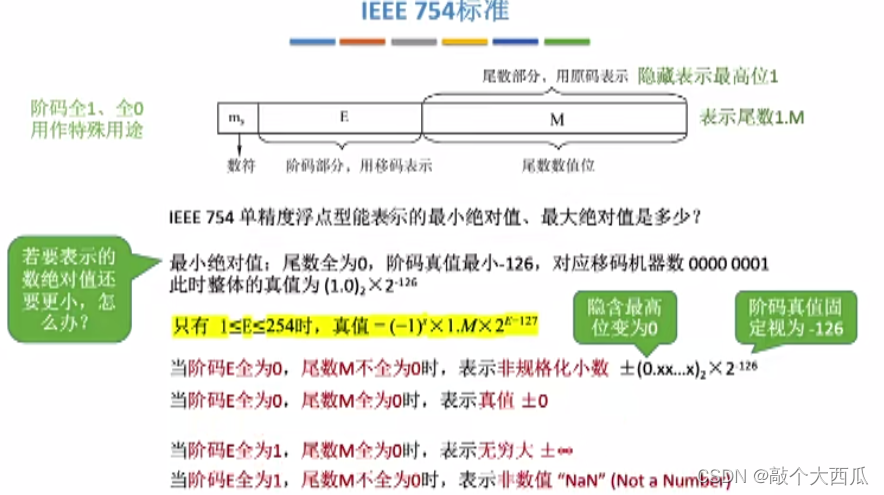

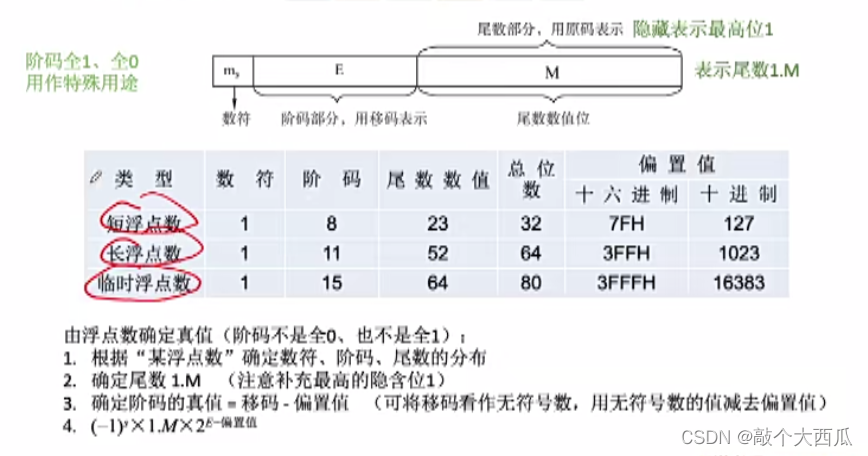

浮点数表示

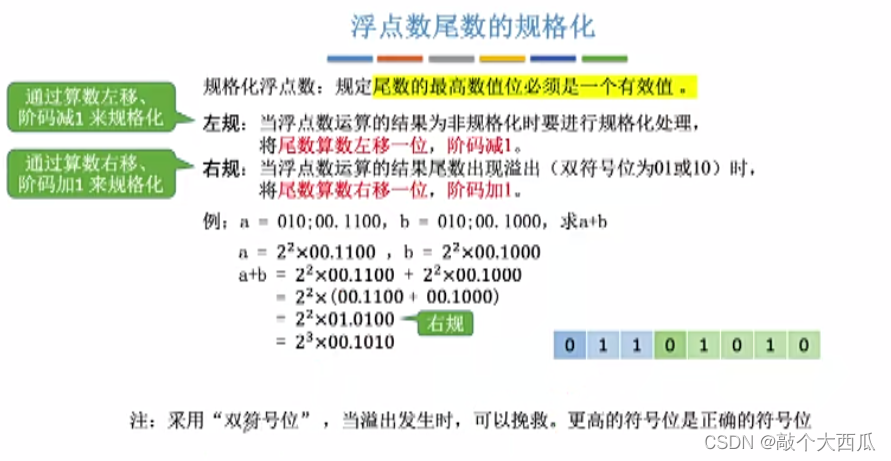

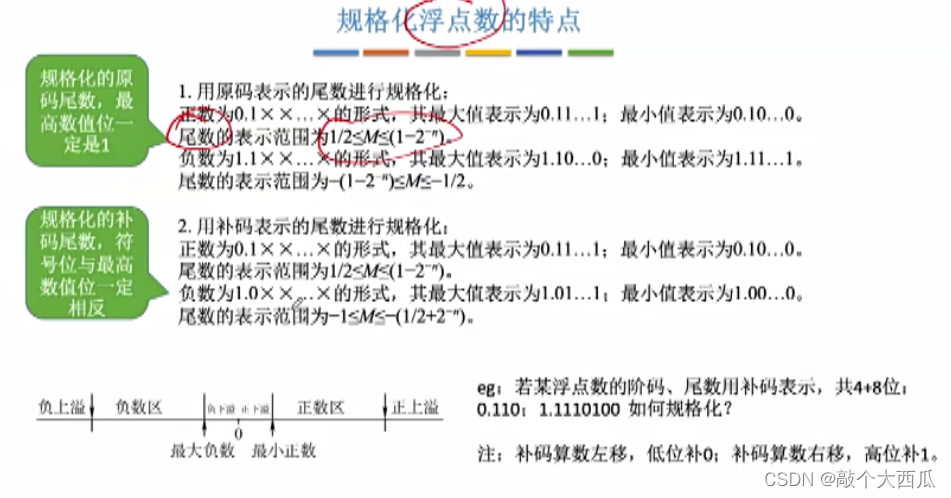

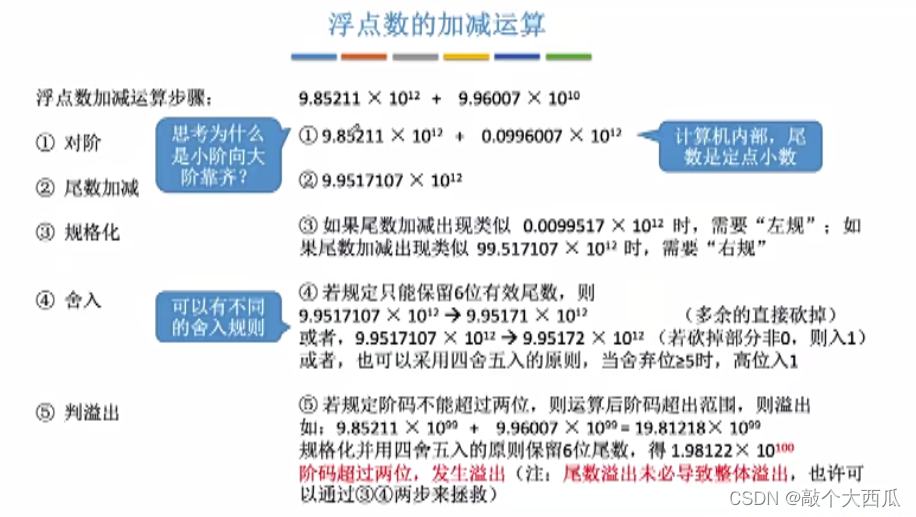

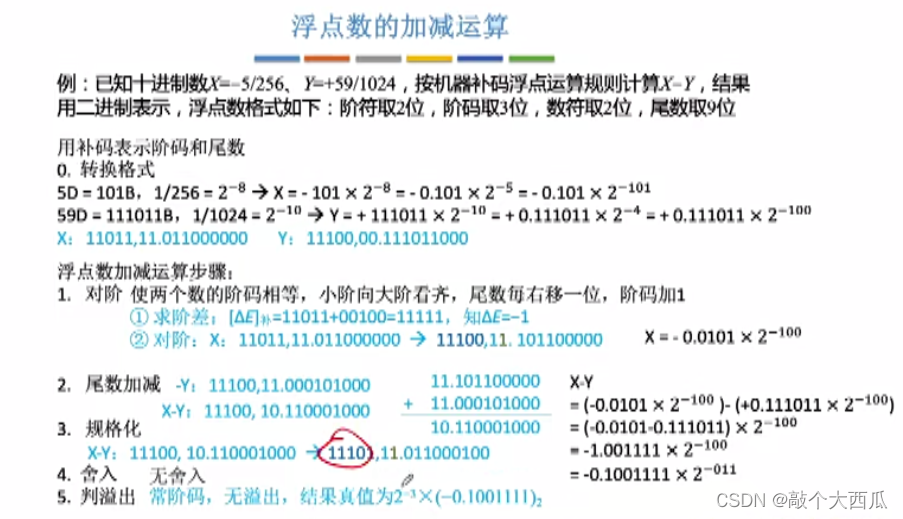

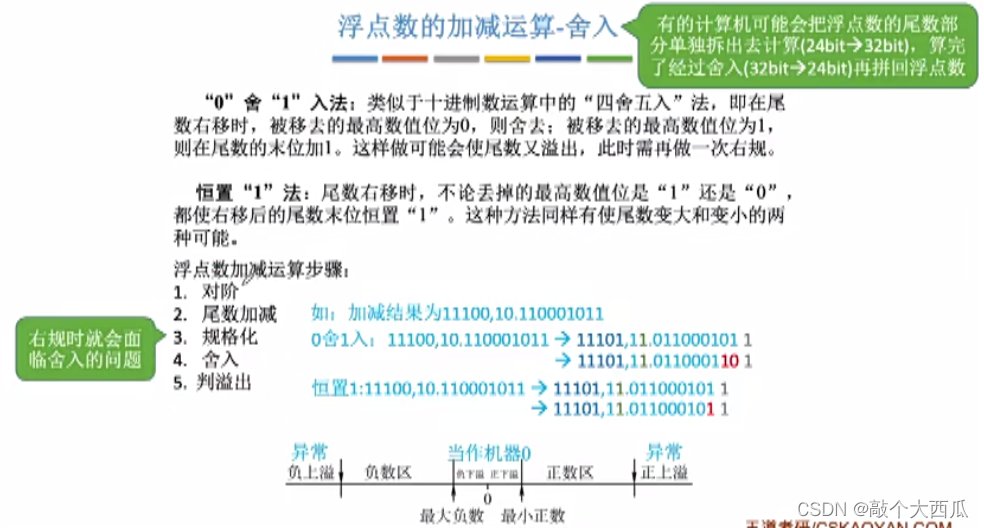

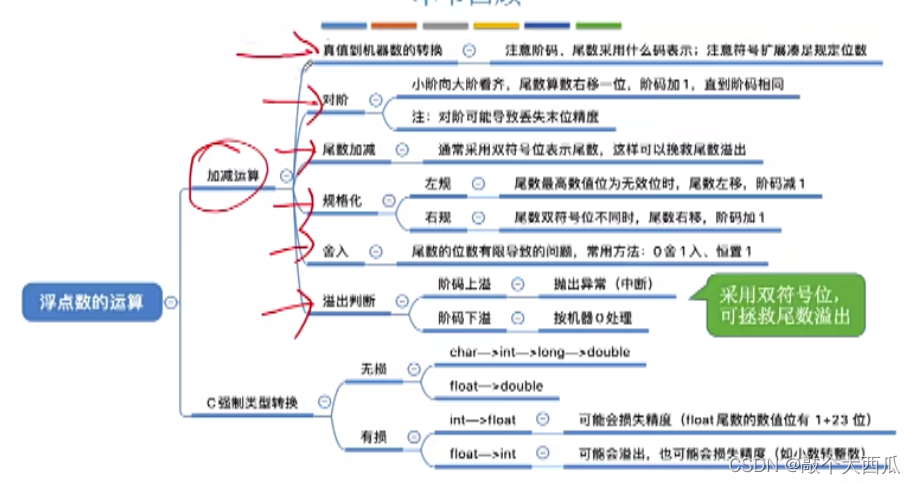

浮点数的运算

此处要注意格式转换时5D表示十进制下的5,101B表示二进制下的5,同时本题中的浮点数格式要注意,此题中阶符取两位,浮点数标准IEEE754

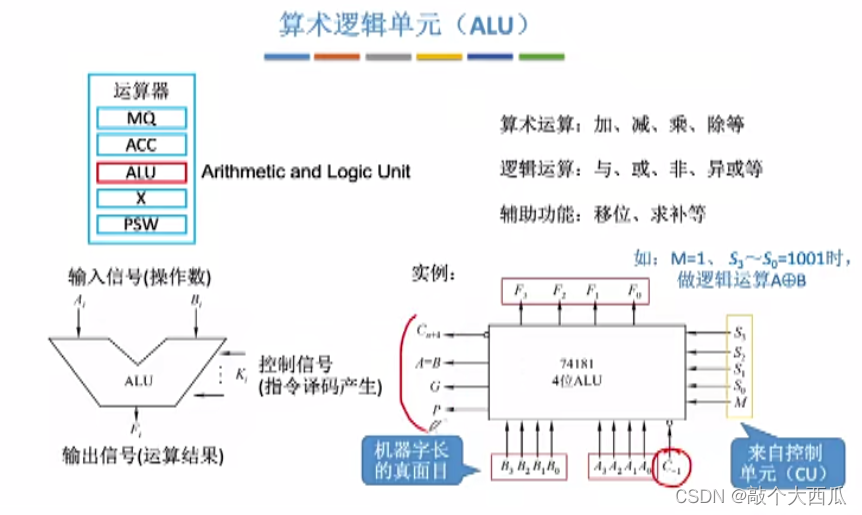

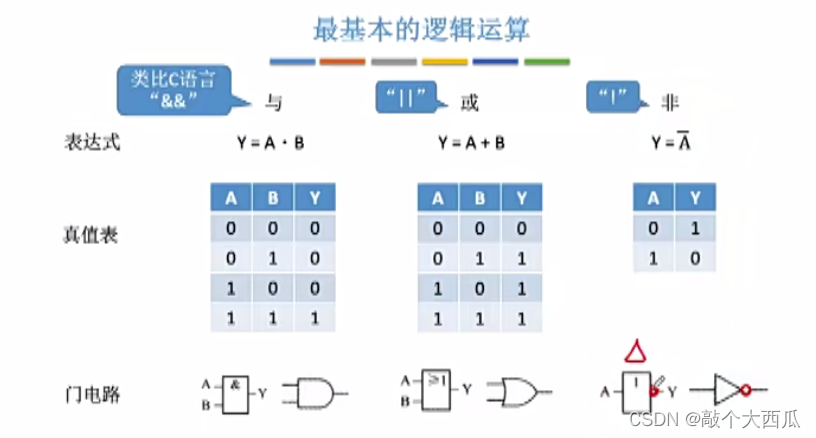

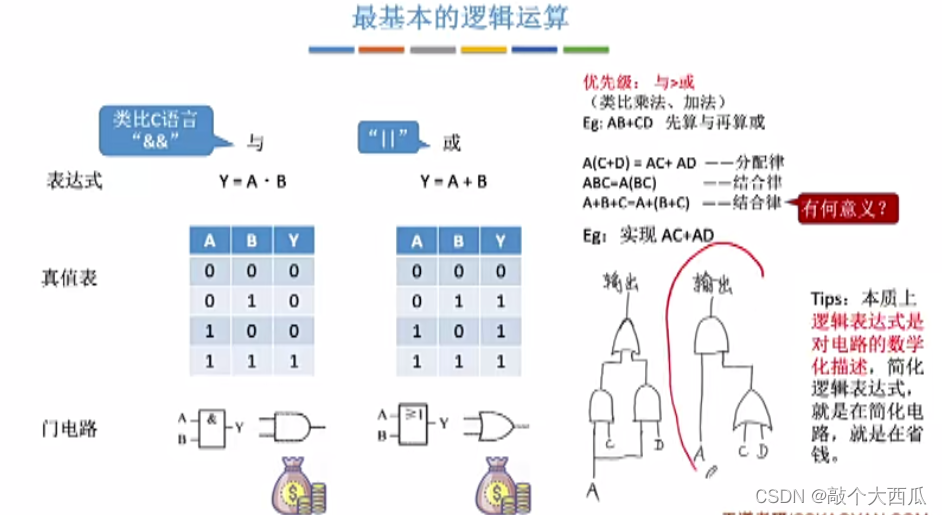

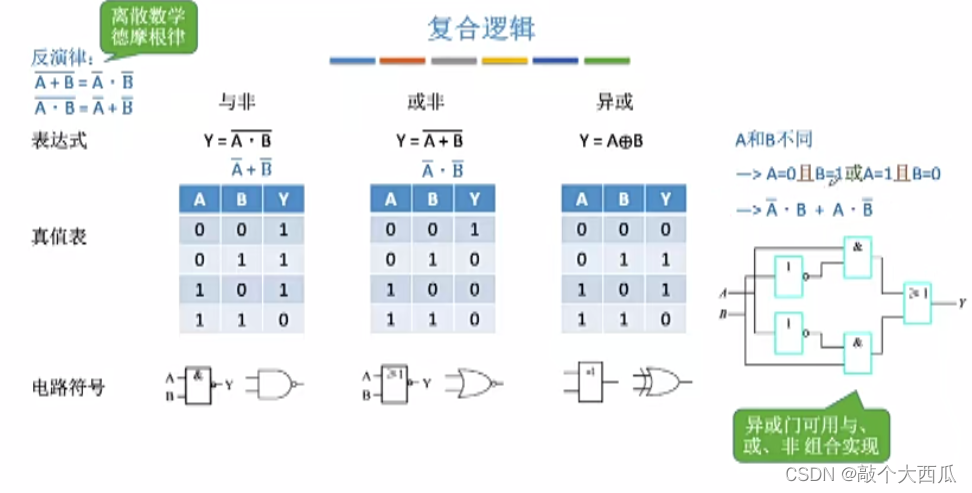

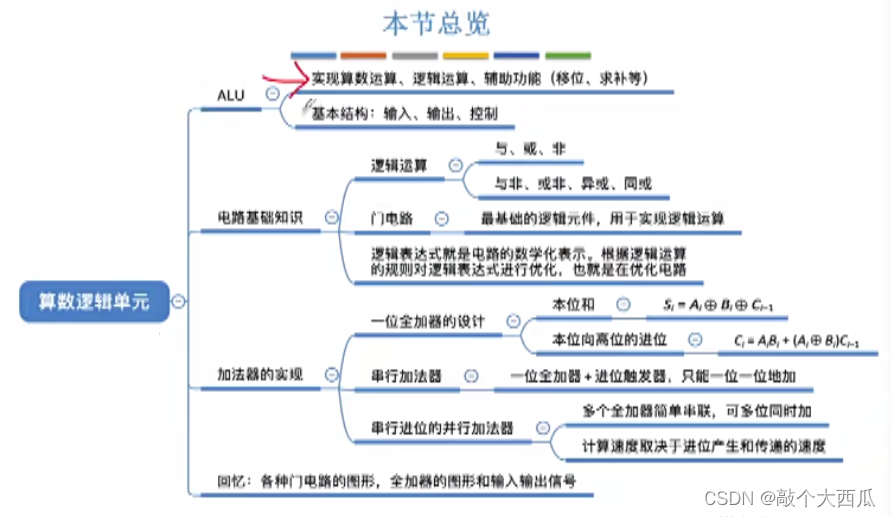

算数逻辑单元

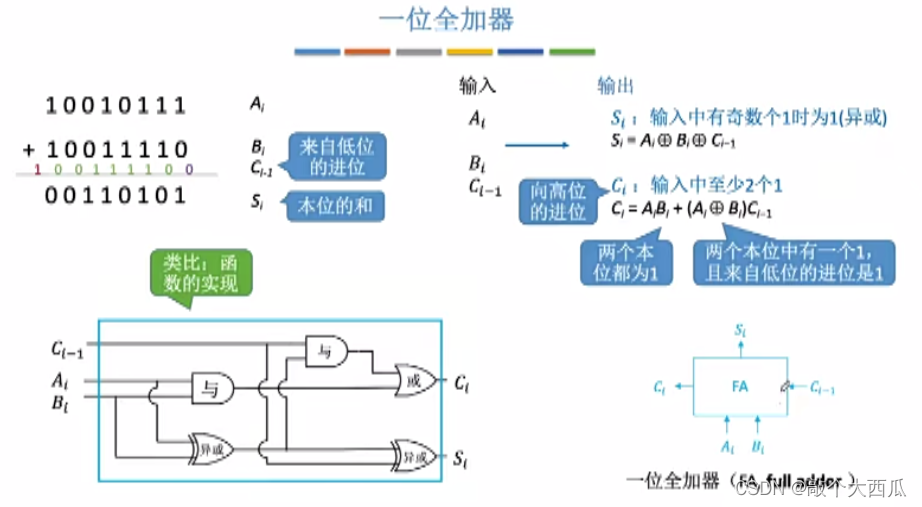

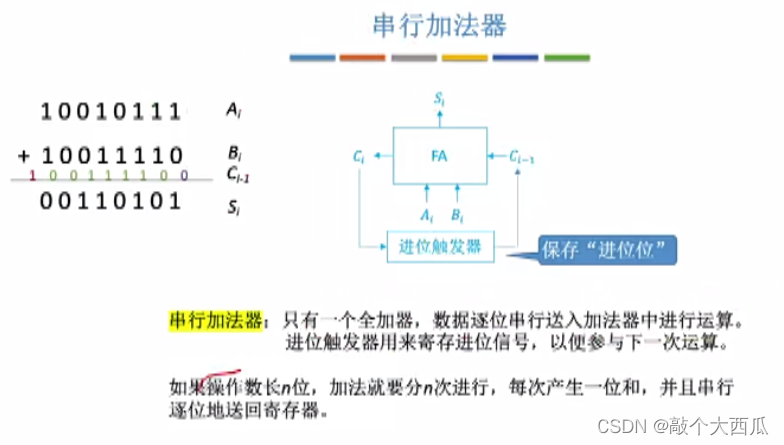

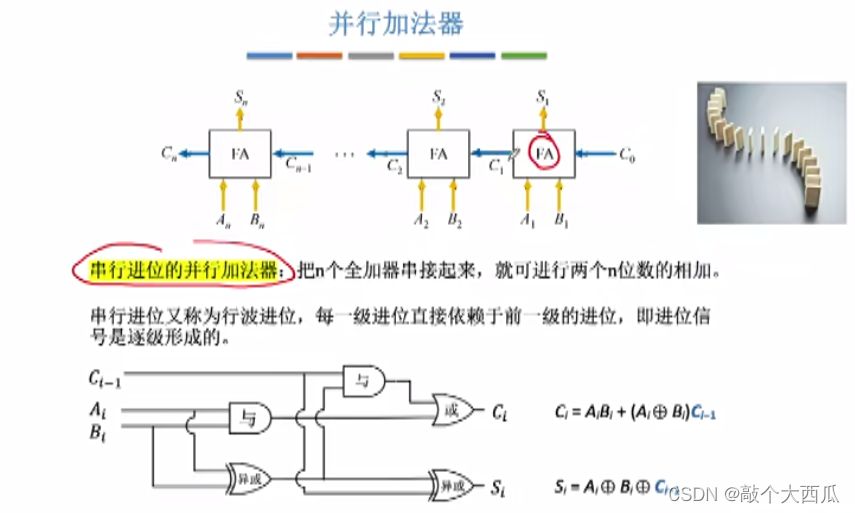

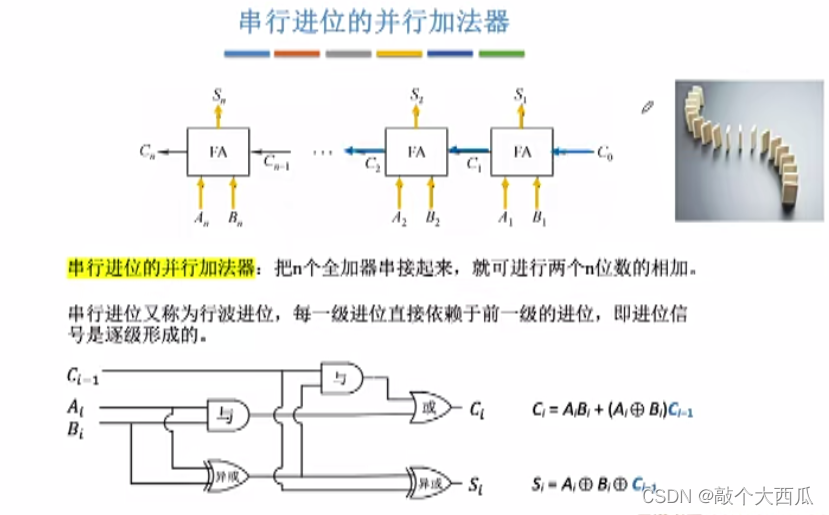

电路基本原理,加法器设计

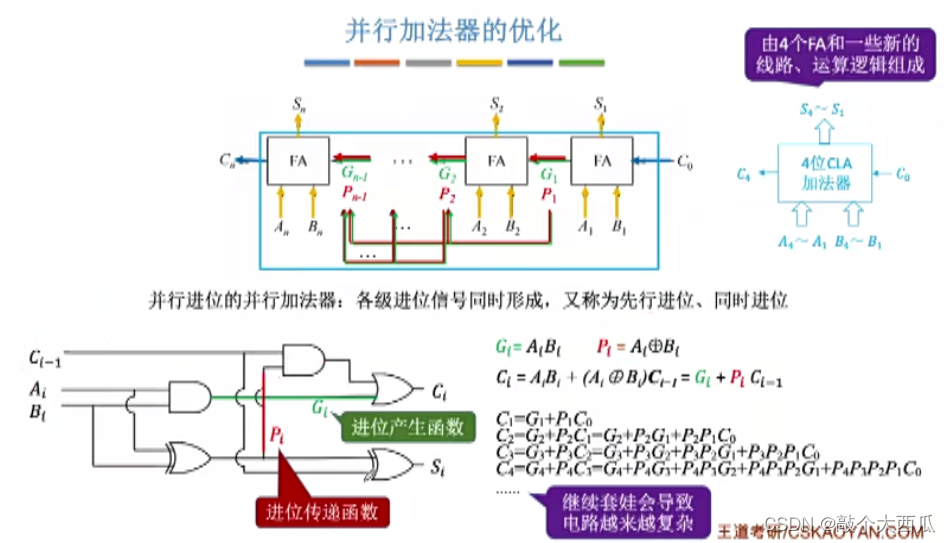

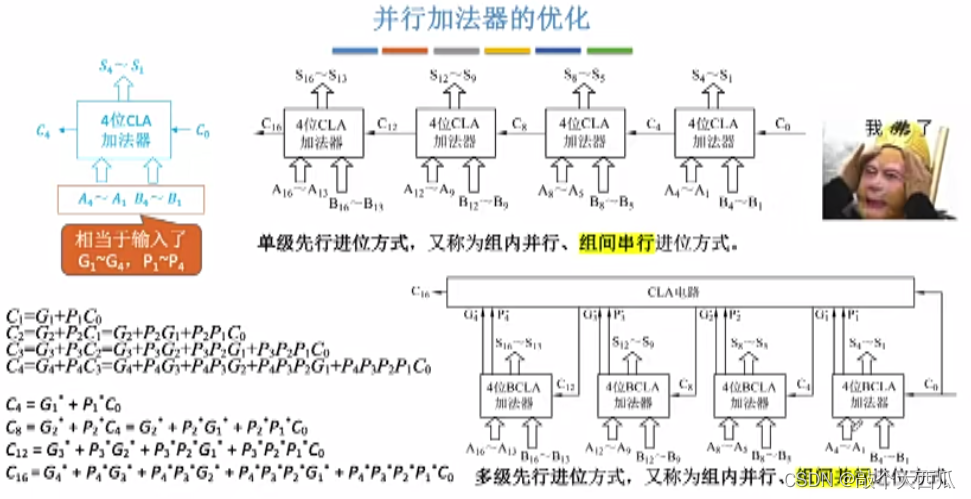

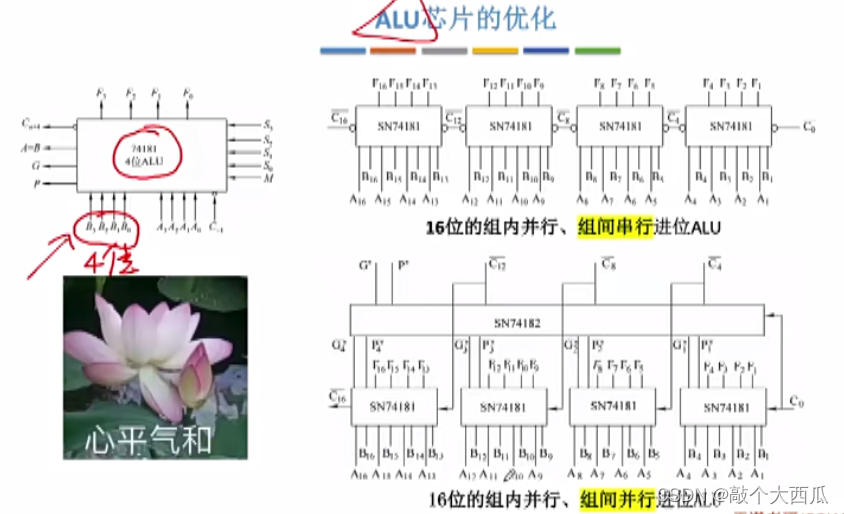

加法器,ALU的改进

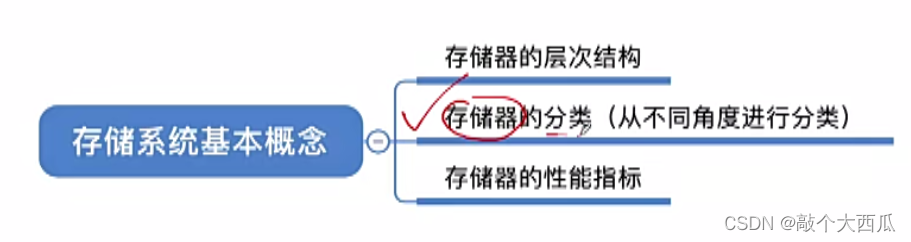

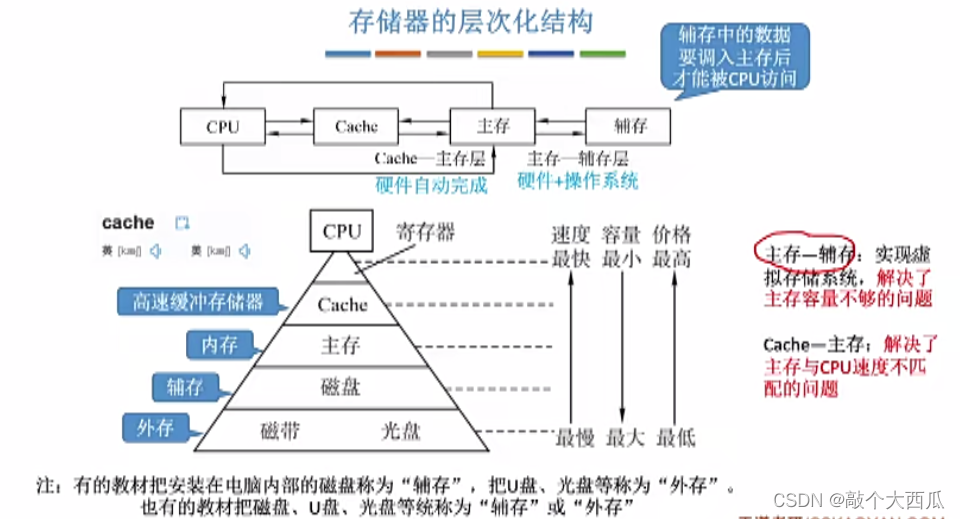

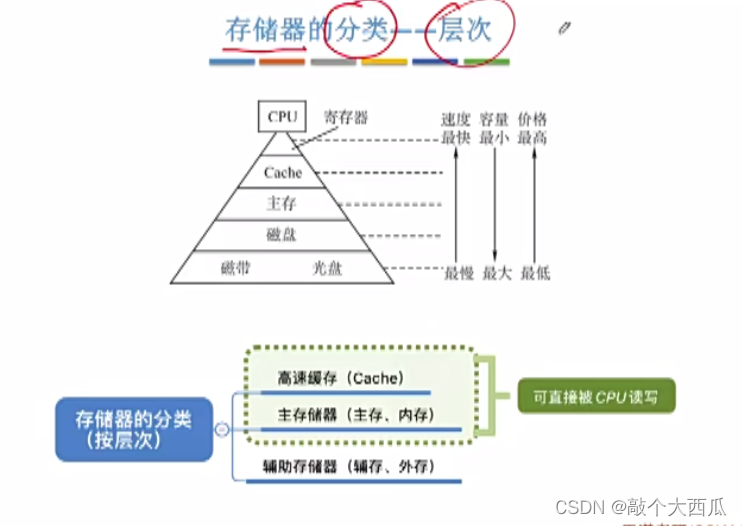

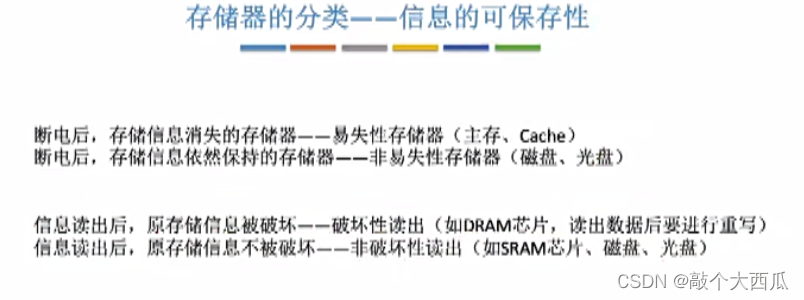

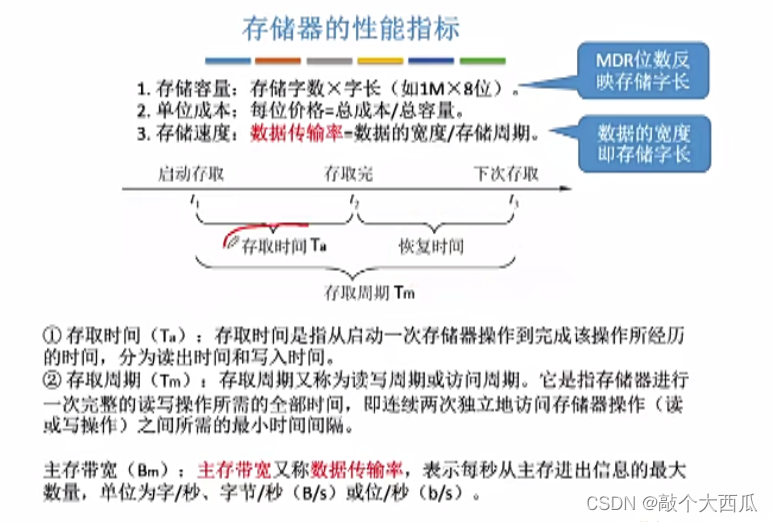

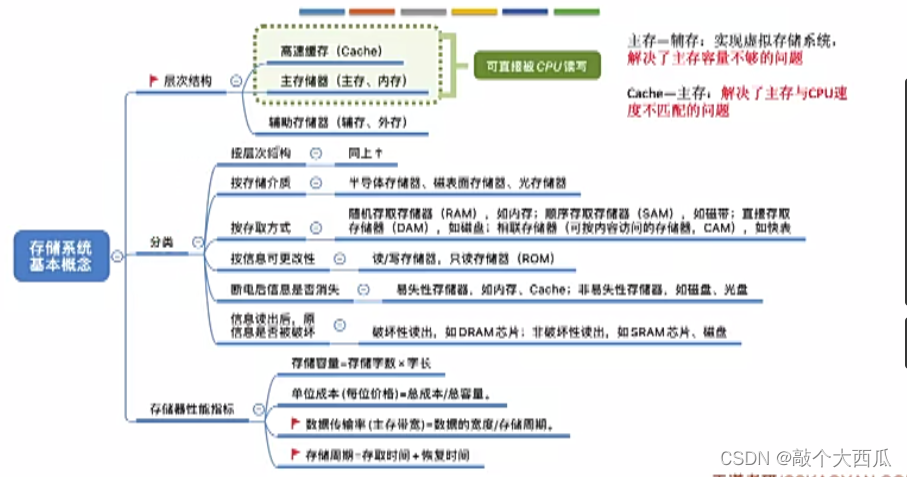

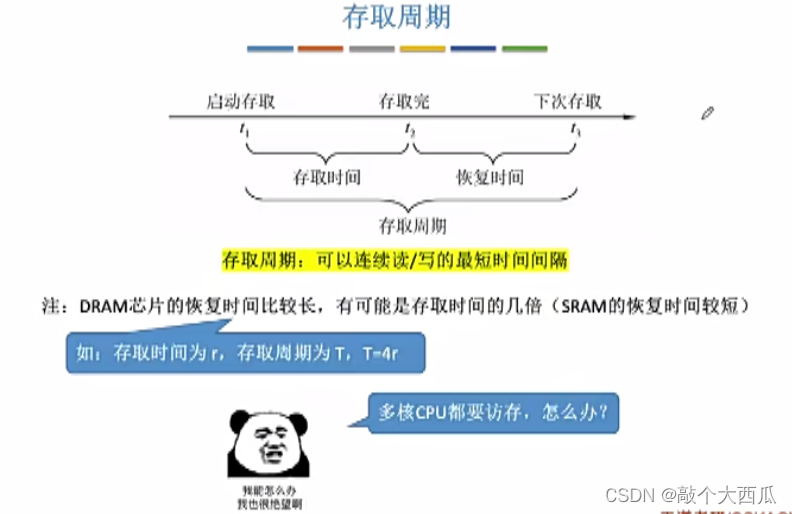

第三章存储系统

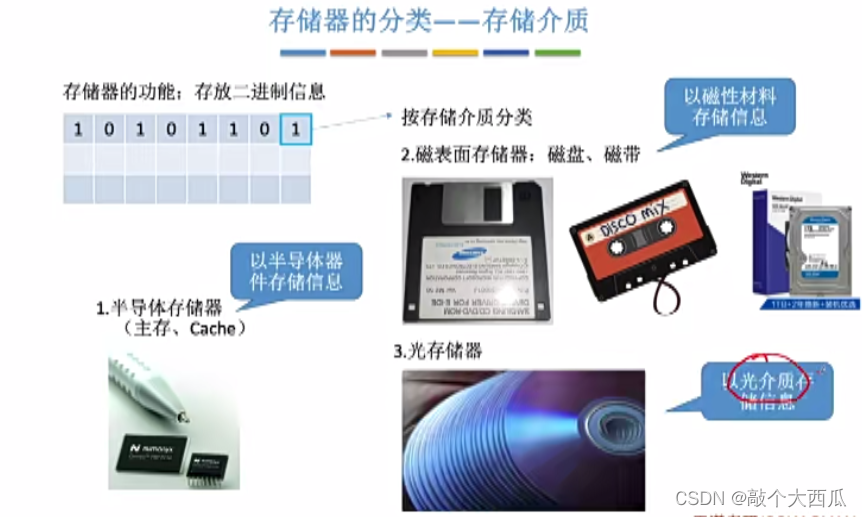

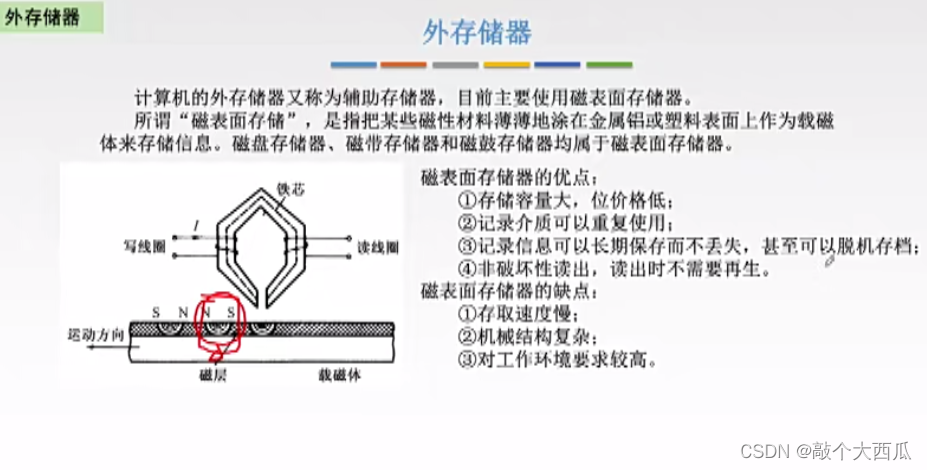

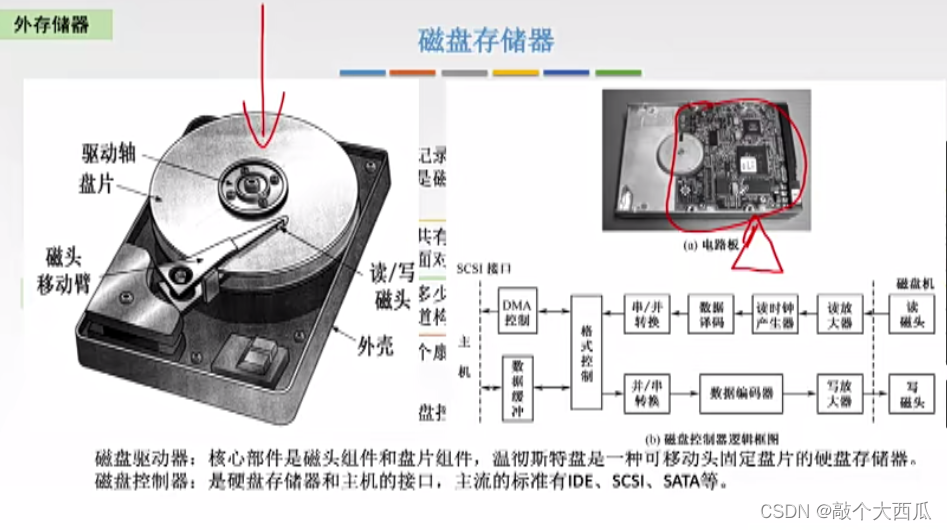

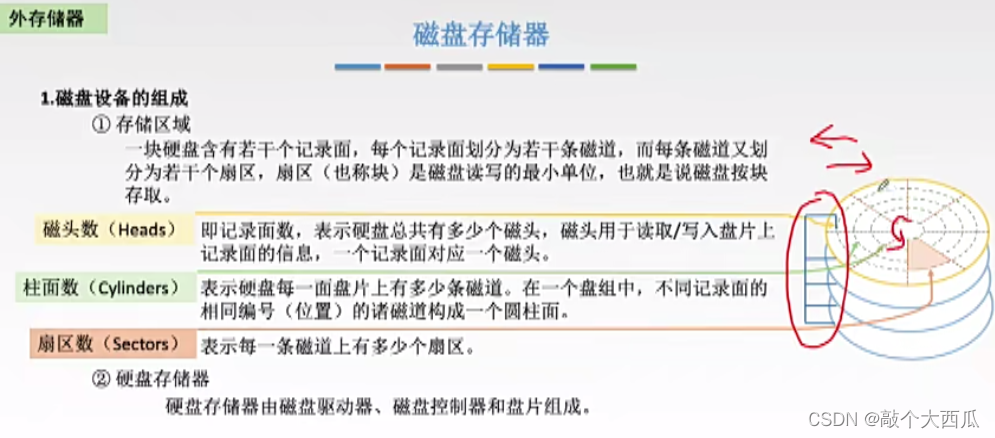

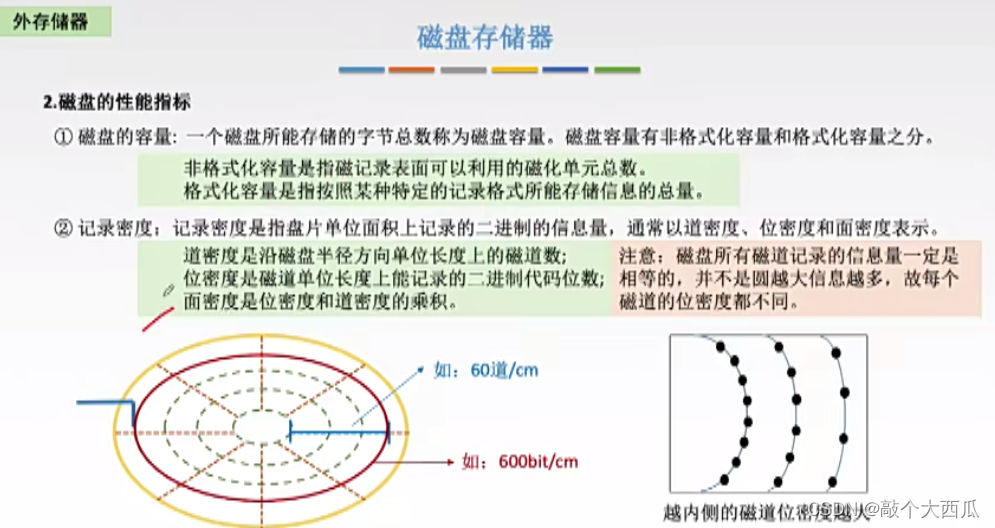

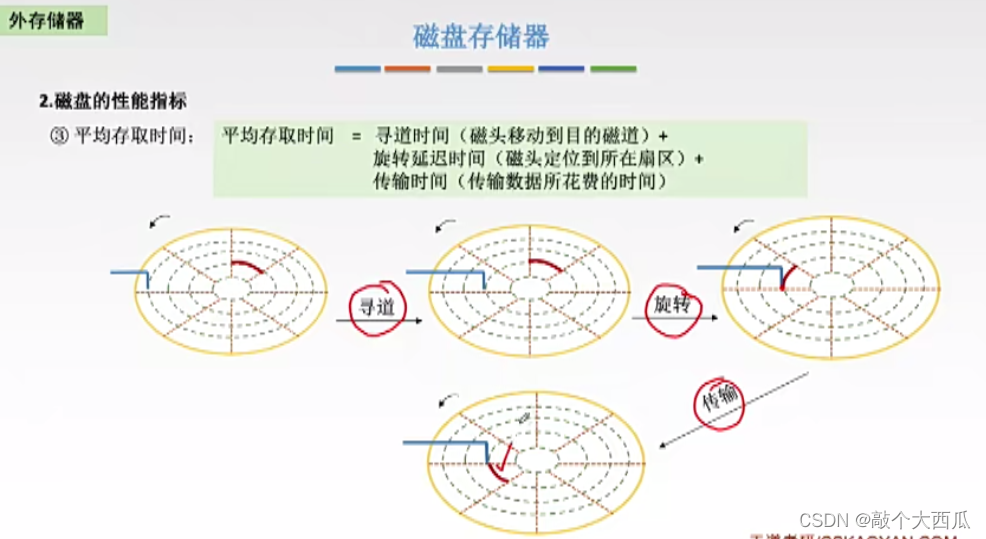

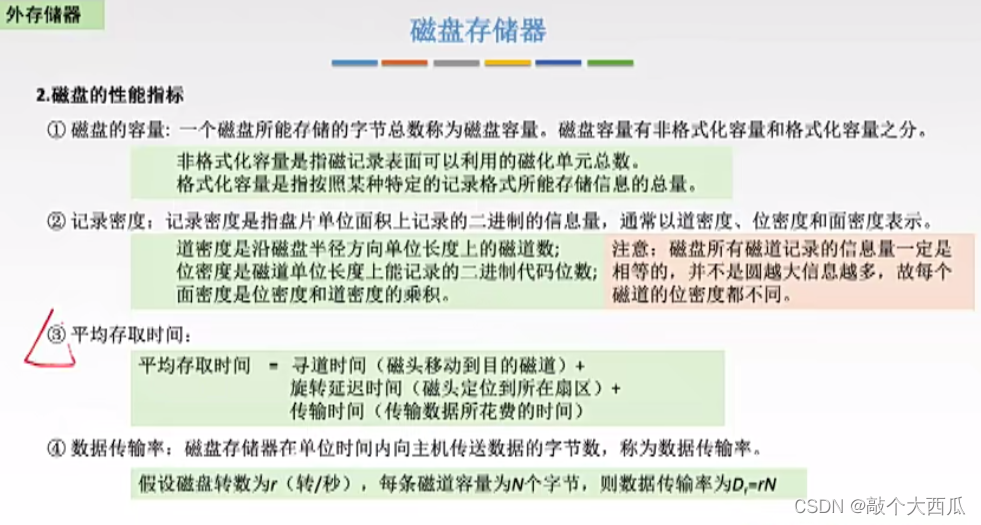

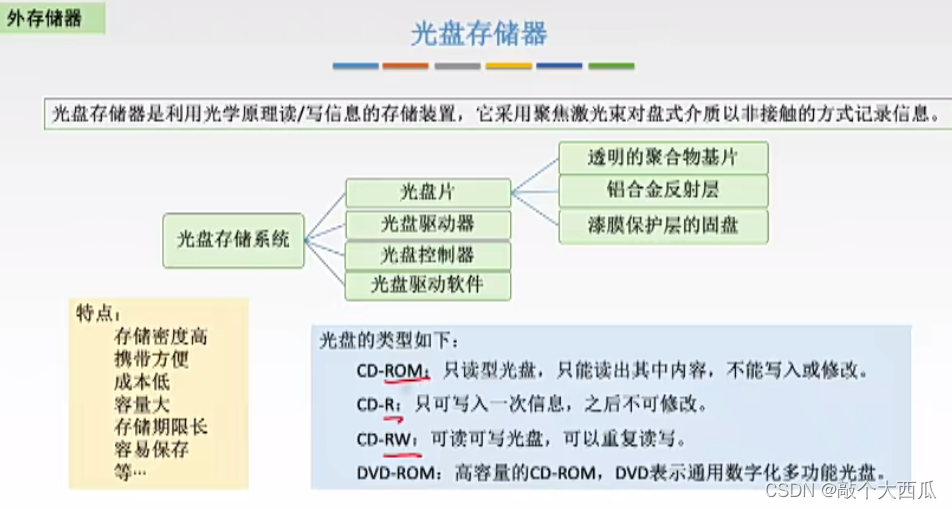

1.半导体存储器,2.磁表面存储器,3.光存储器

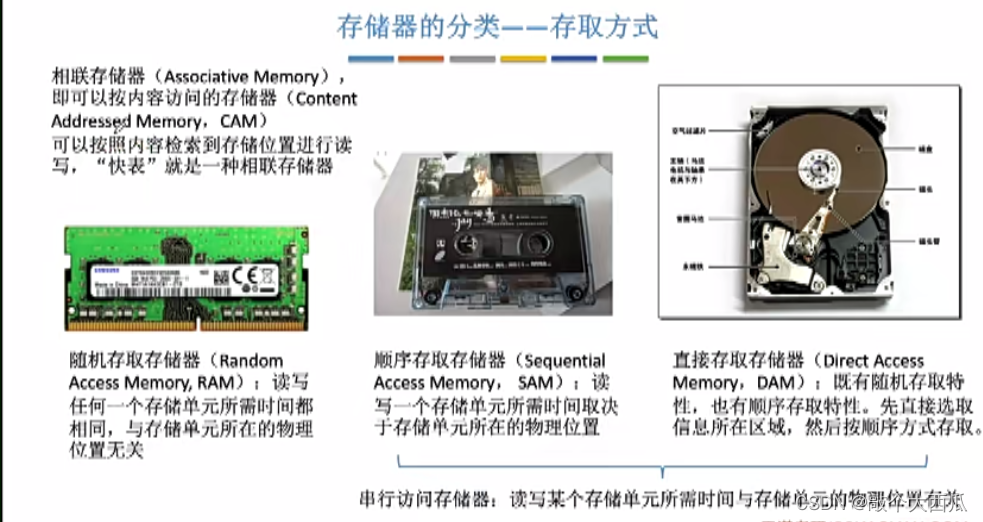

1.RAM,2.SAM,3.DAM

主存储器的基本组成

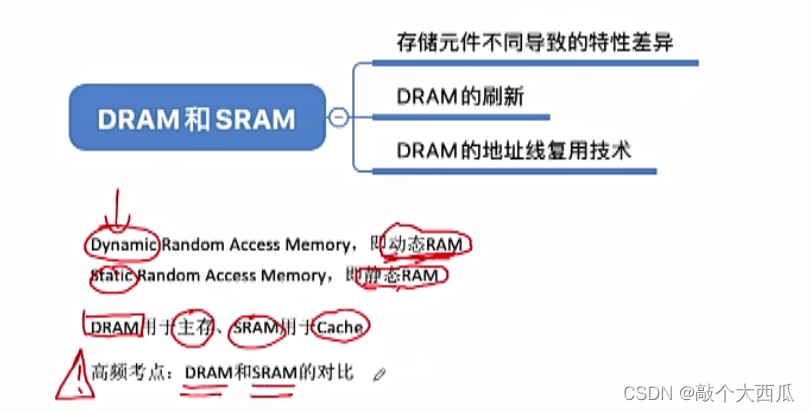

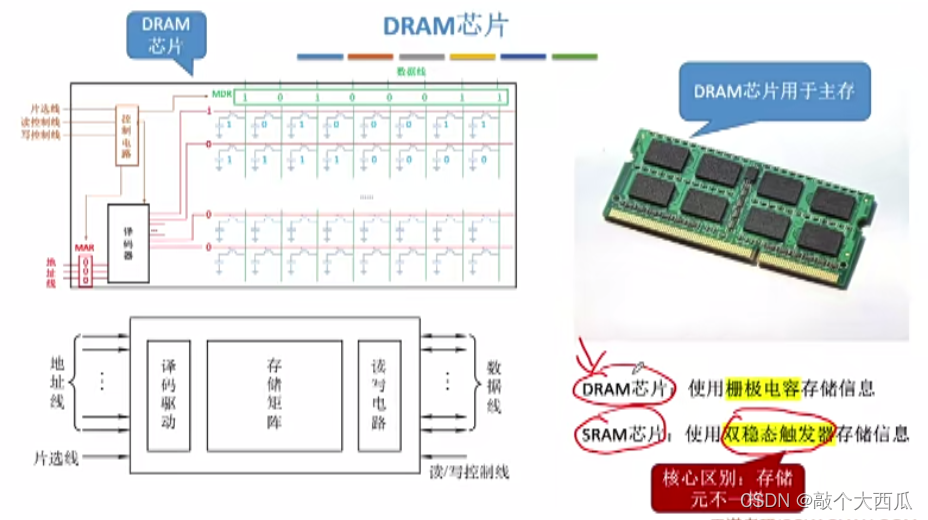

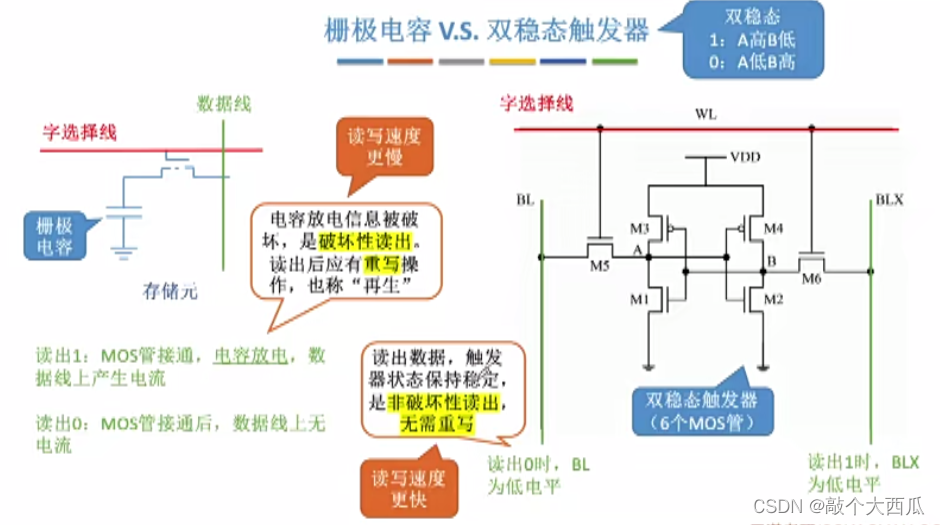

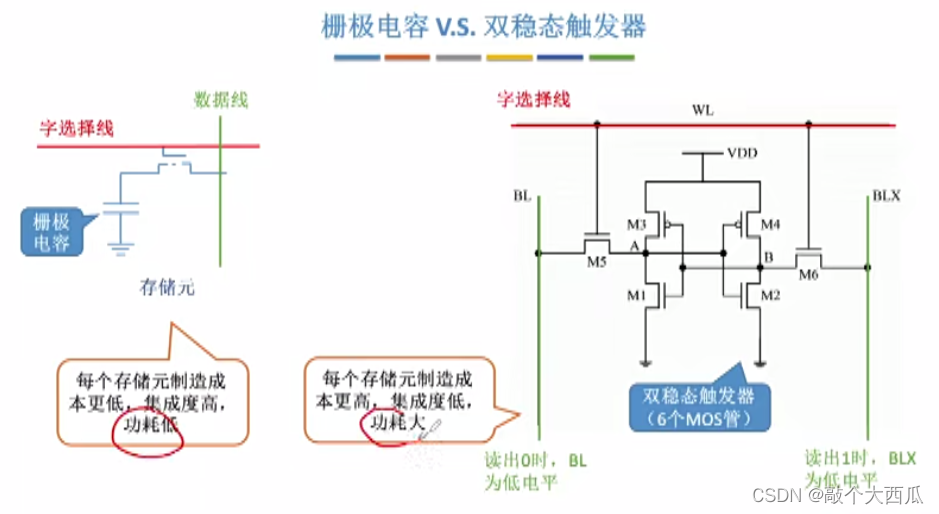

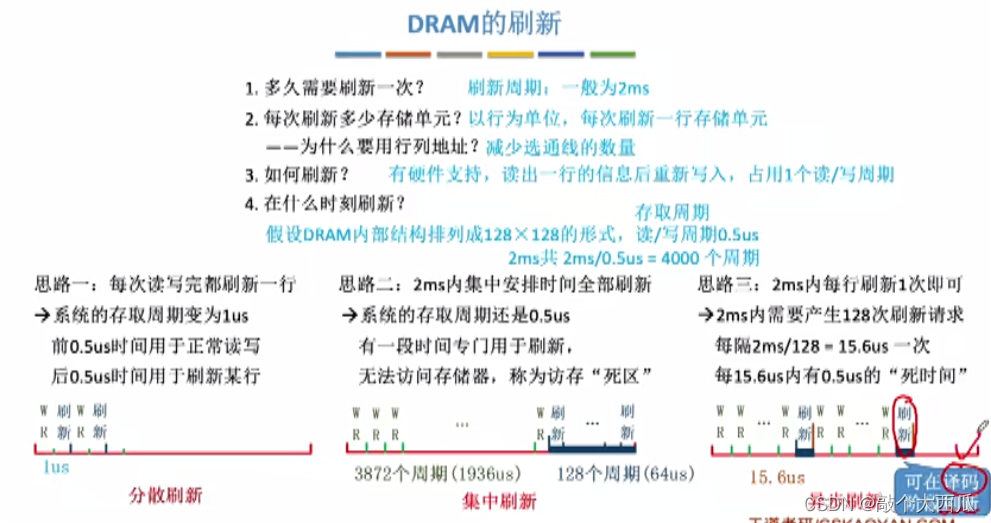

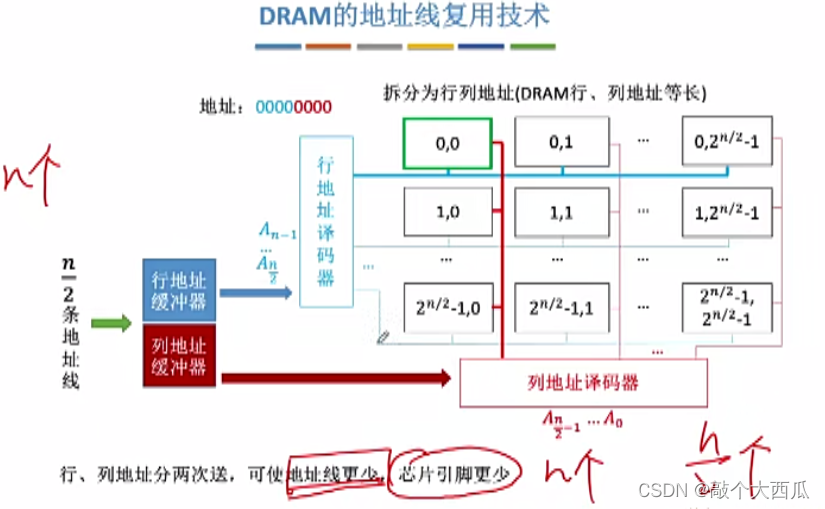

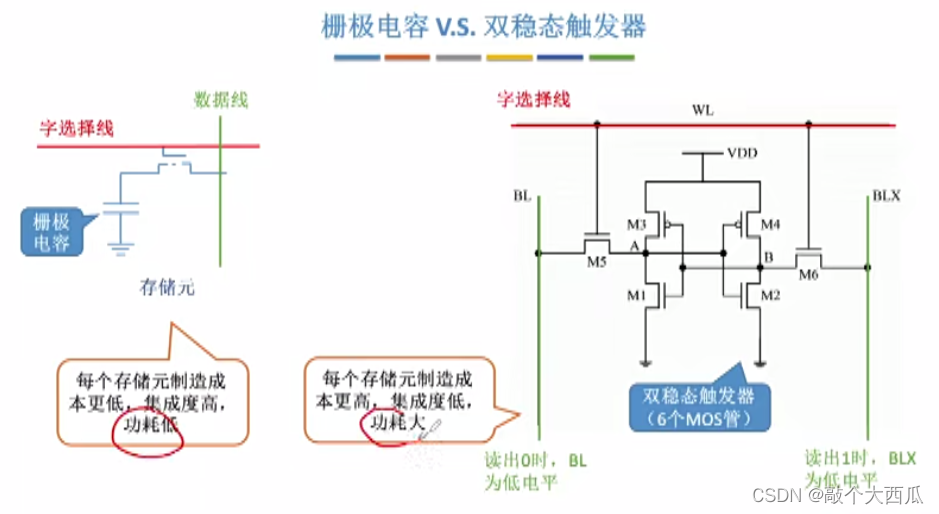

DRAM

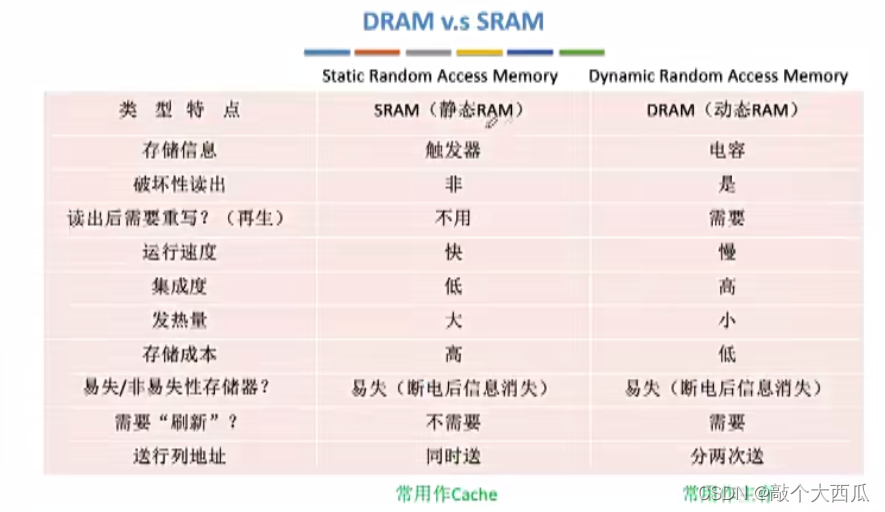

DRAM和SRAM

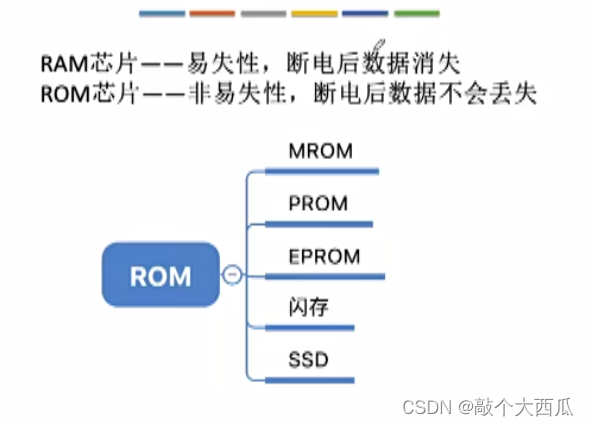

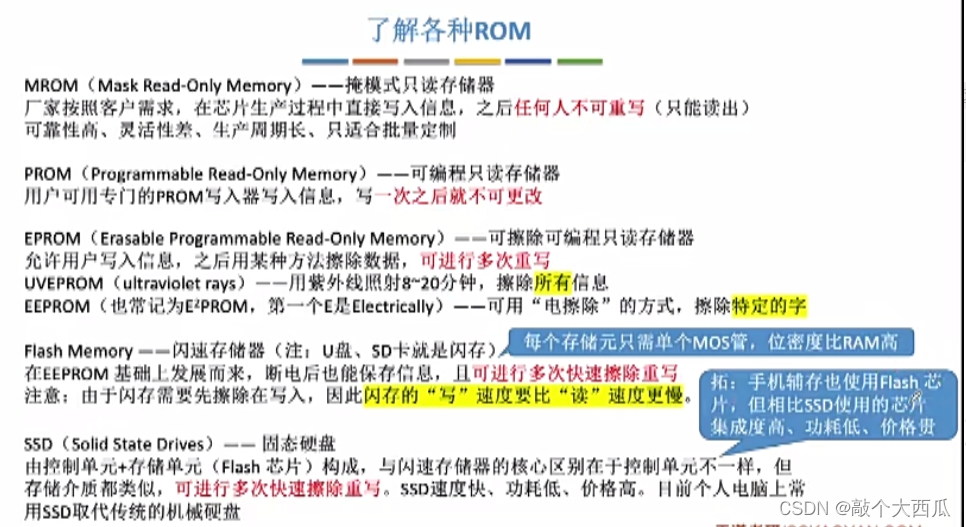

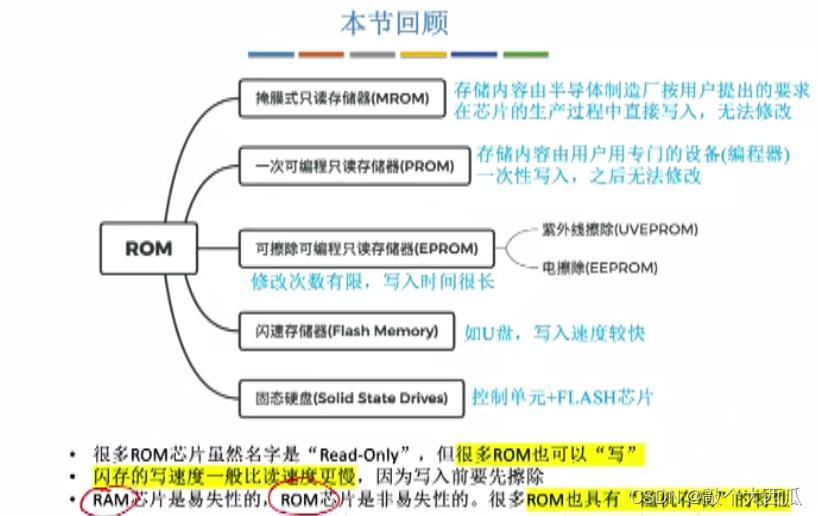

只读存储器ROM

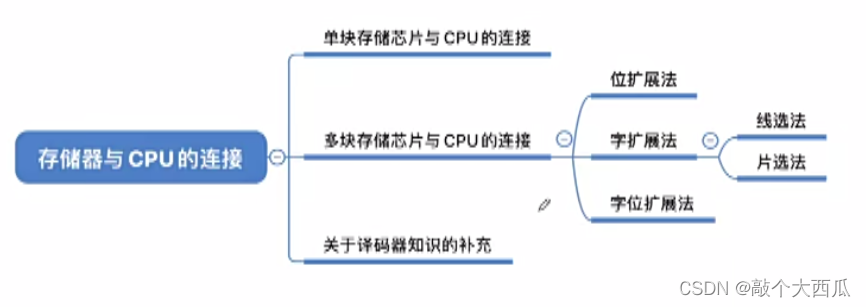

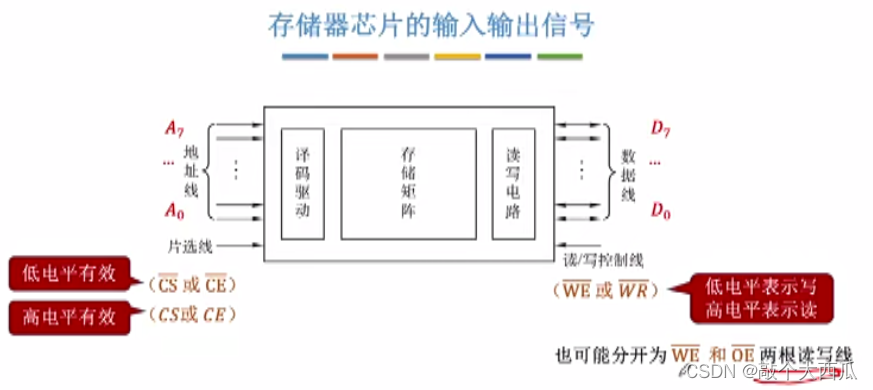

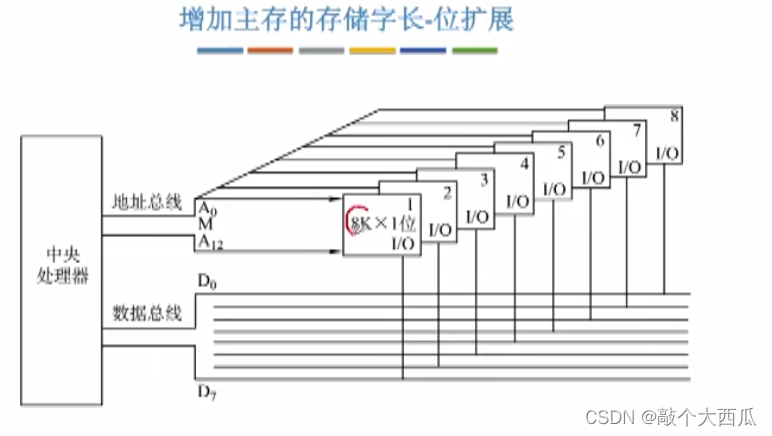

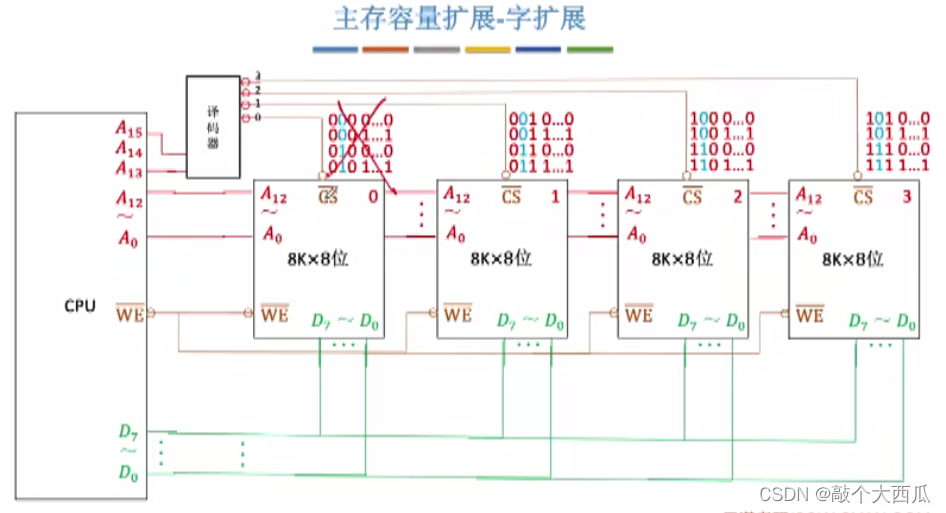

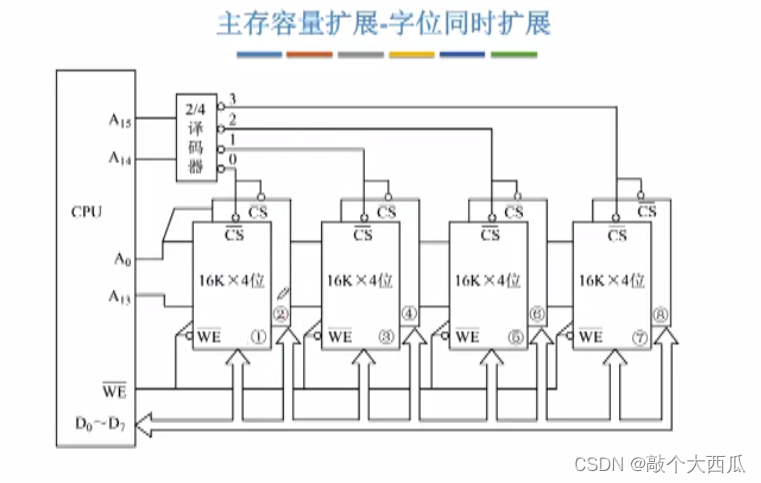

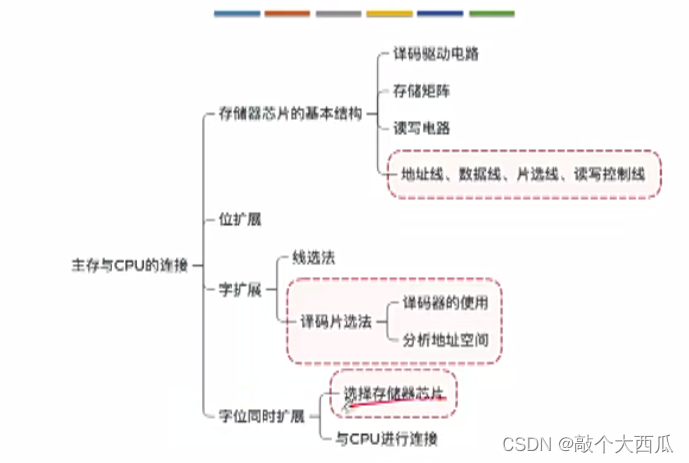

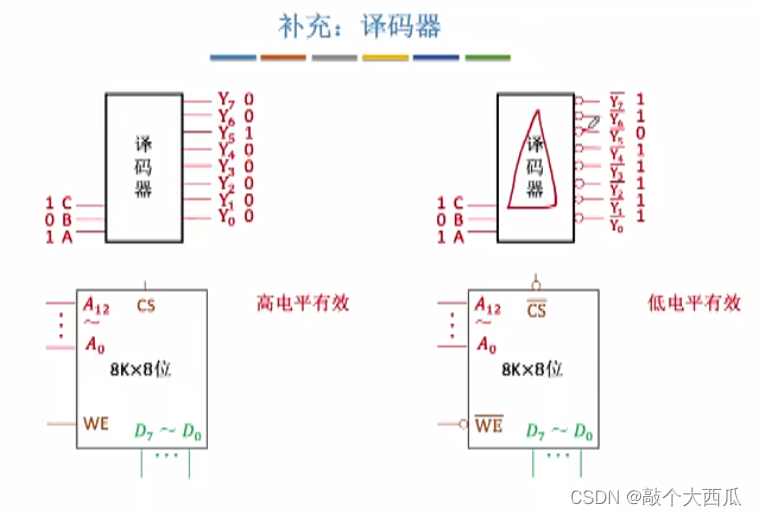

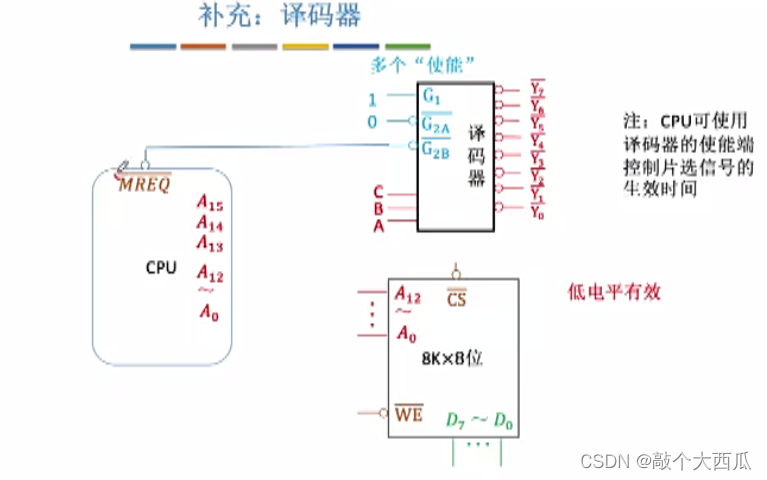

主存与CPU的连接

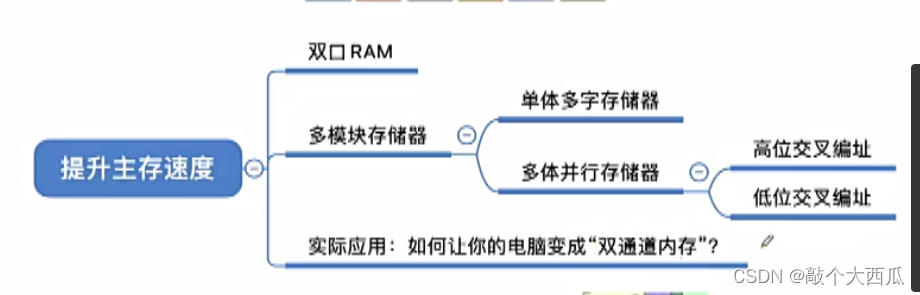

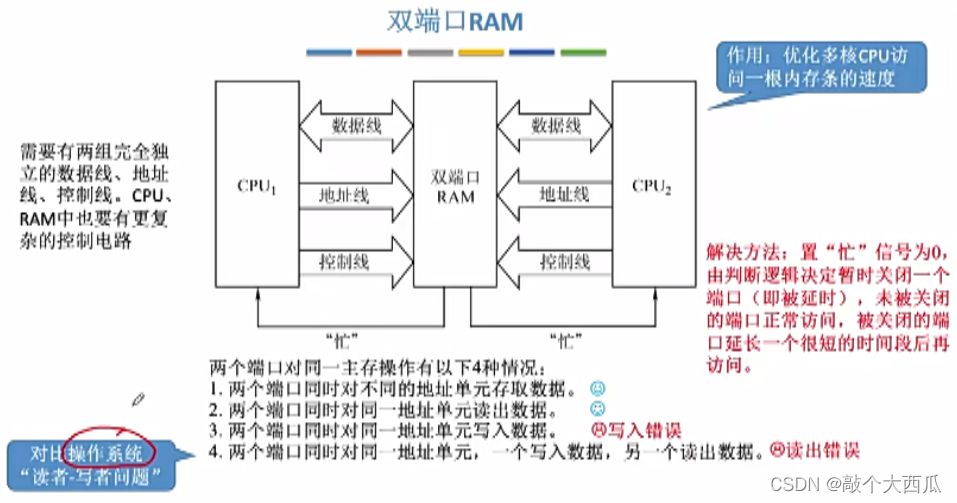

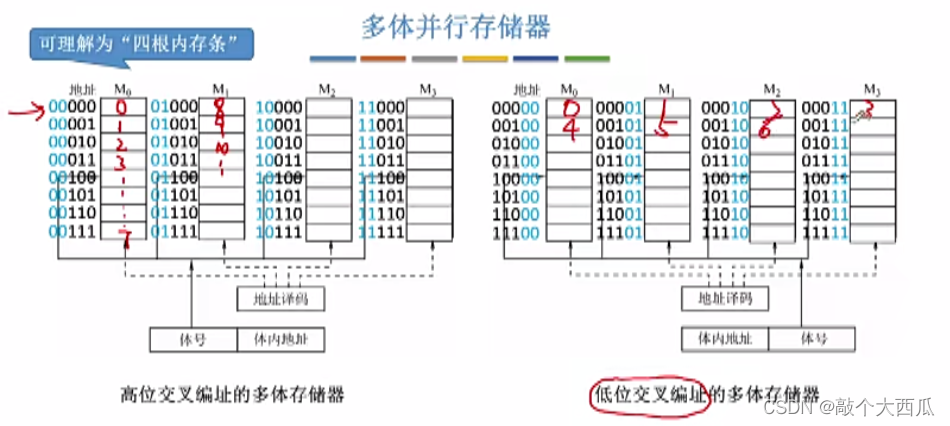

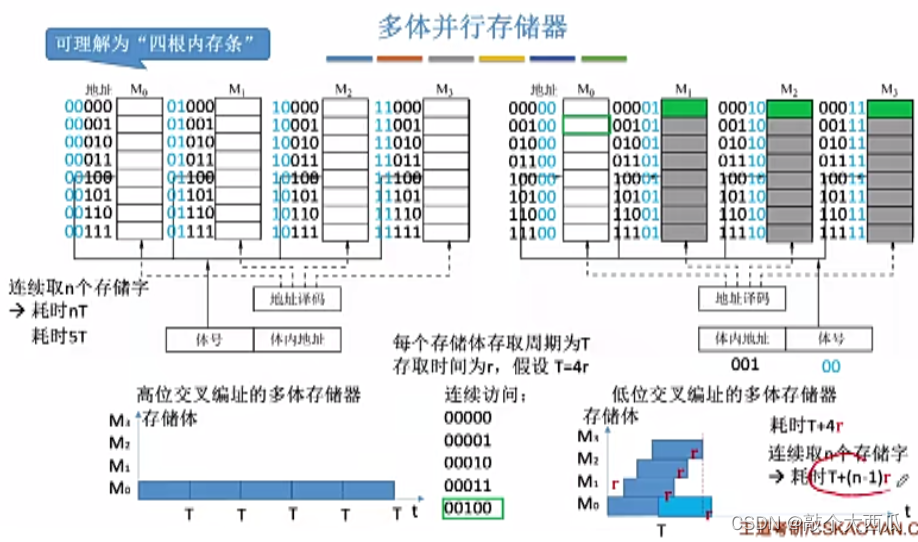

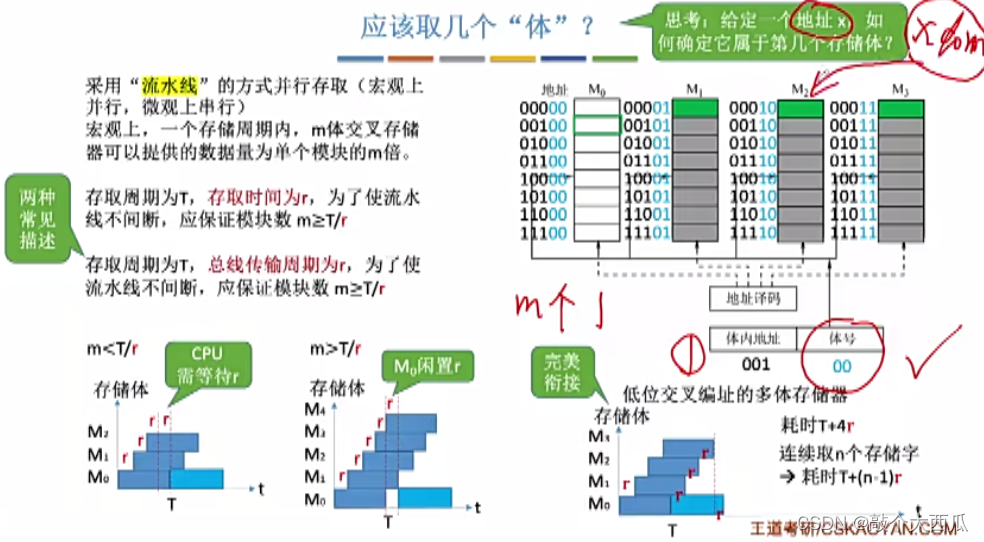

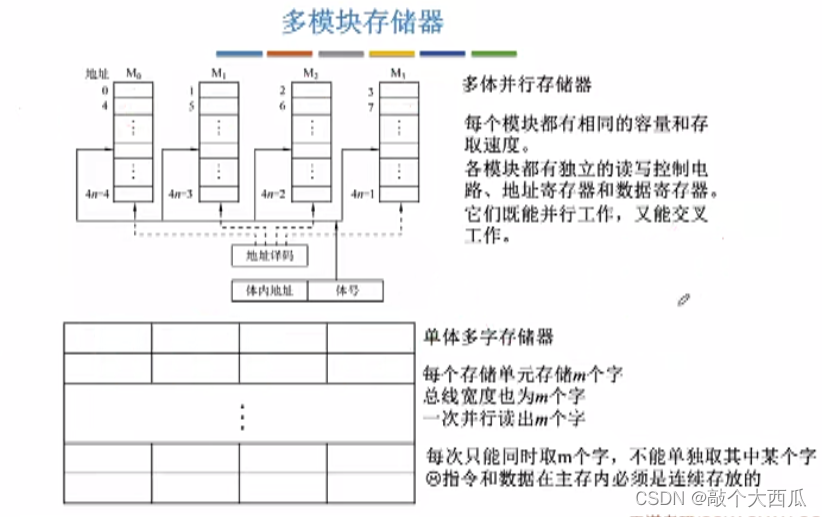

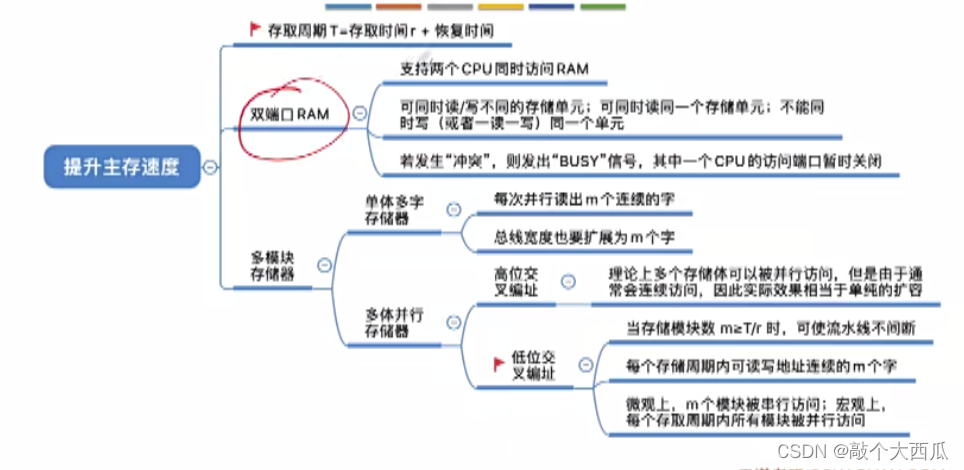

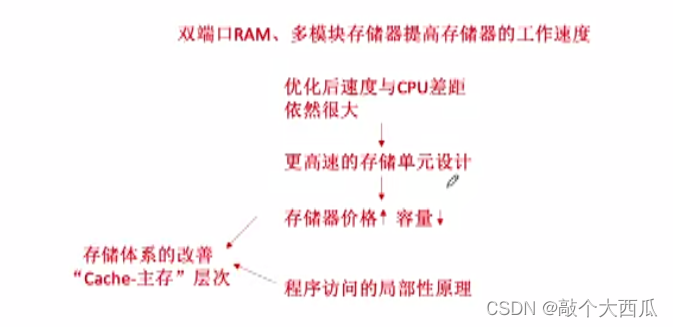

双端ROM和多模块存储器

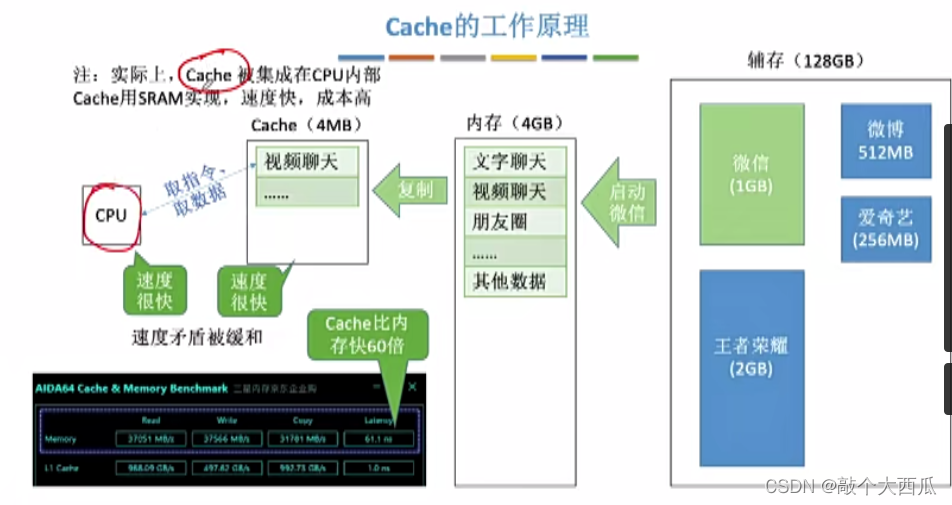

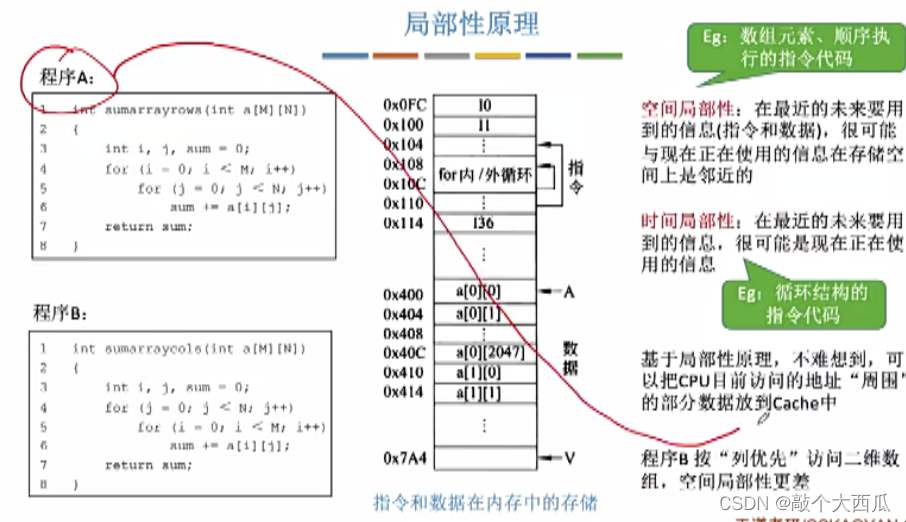

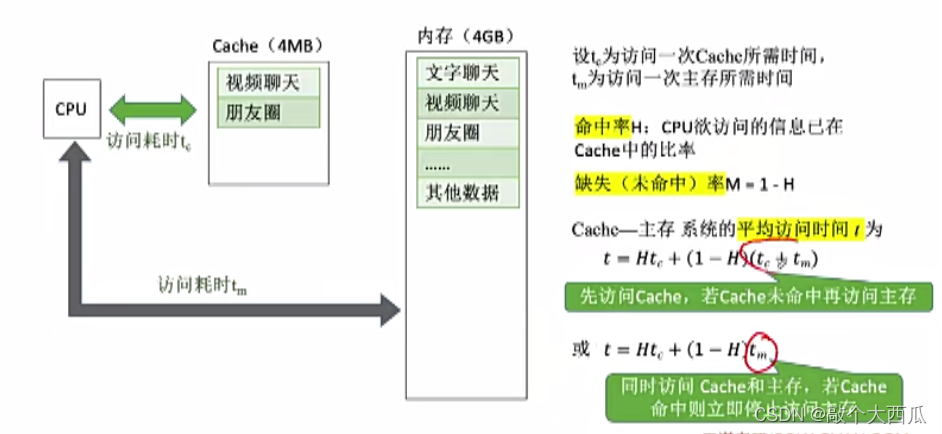

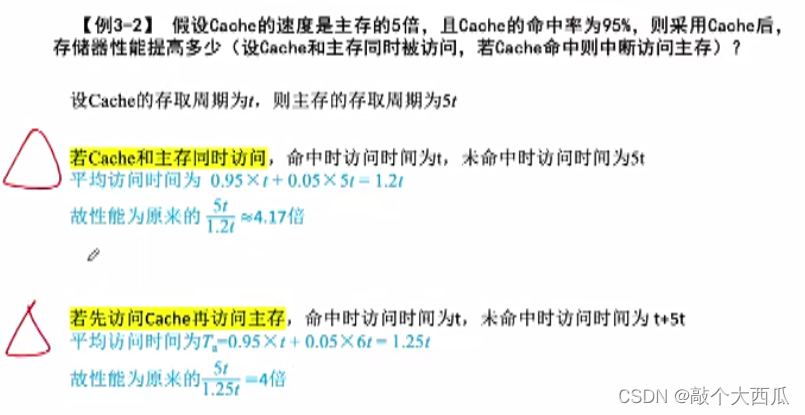

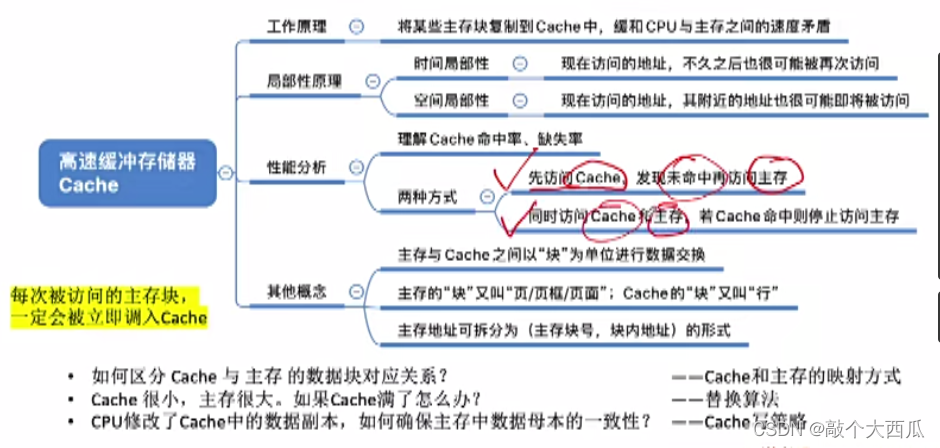

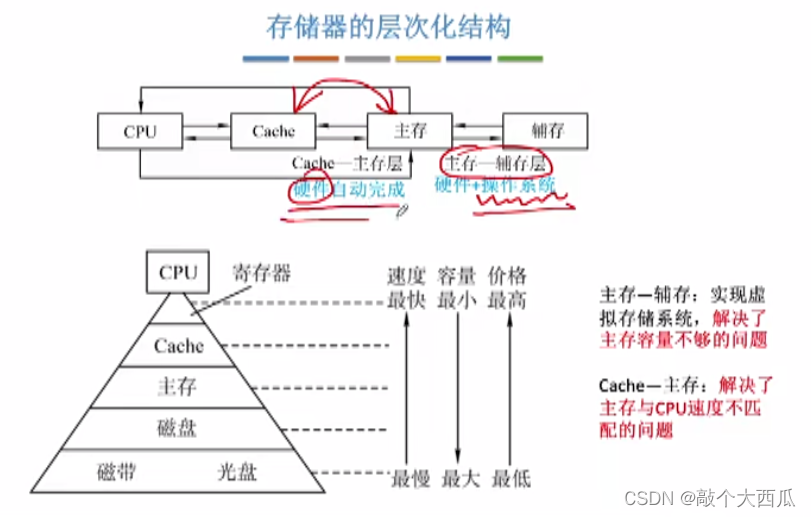

cache基本原理和基本概念

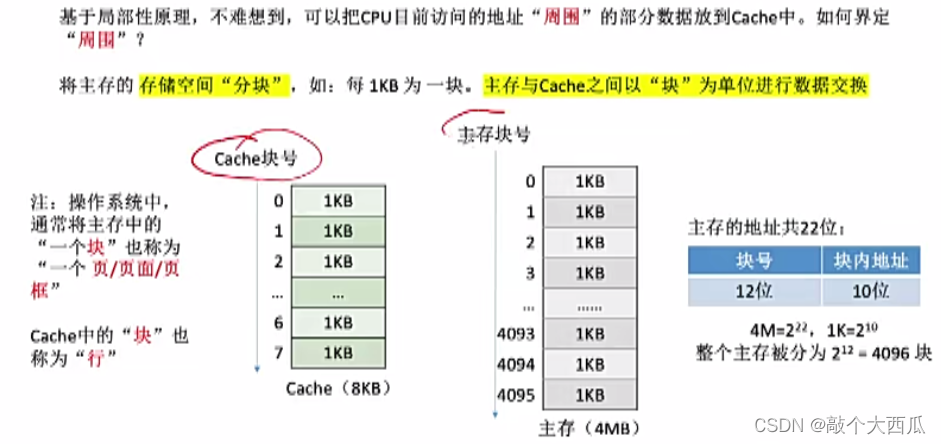

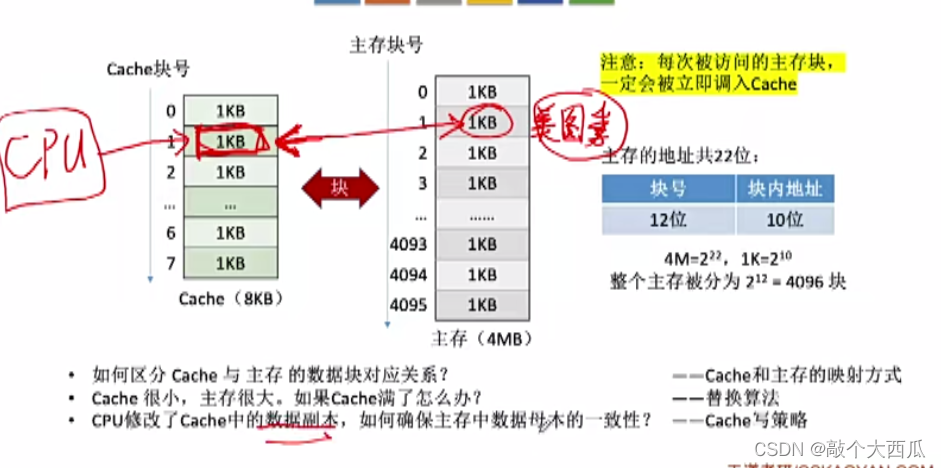

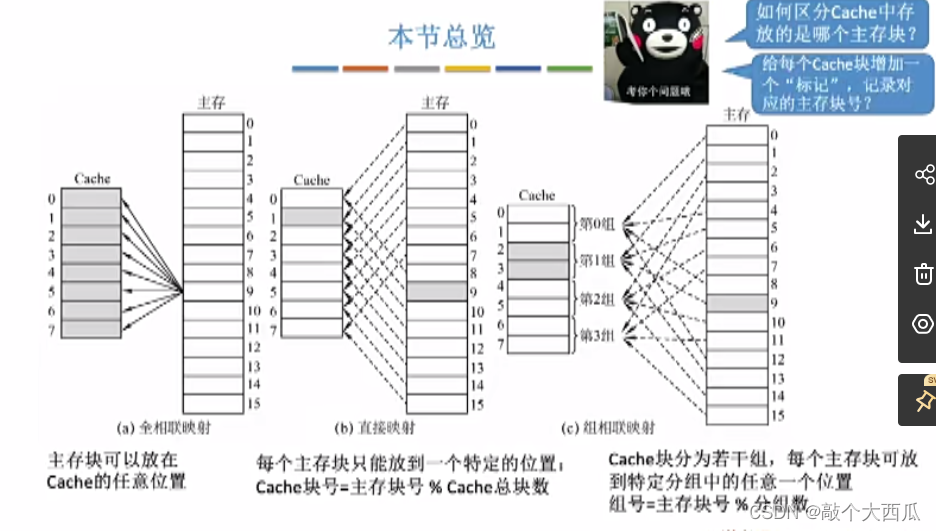

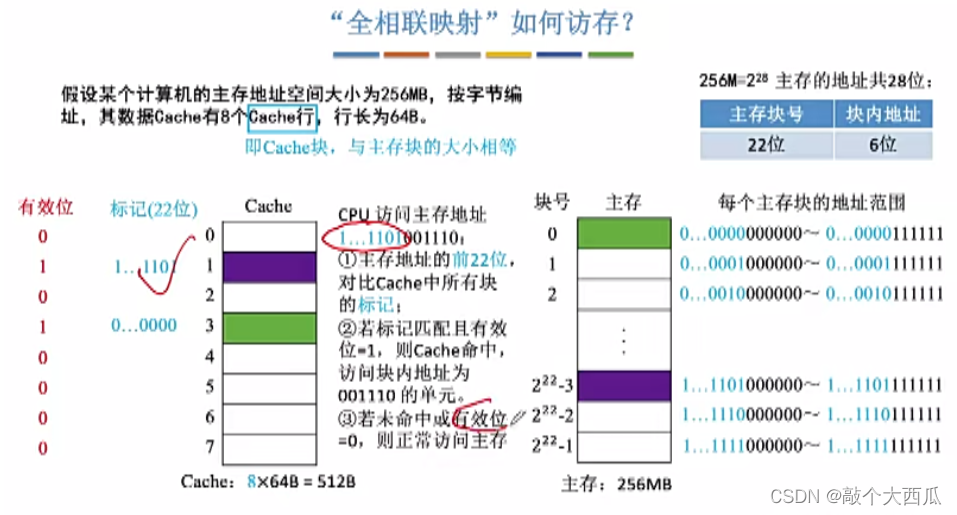

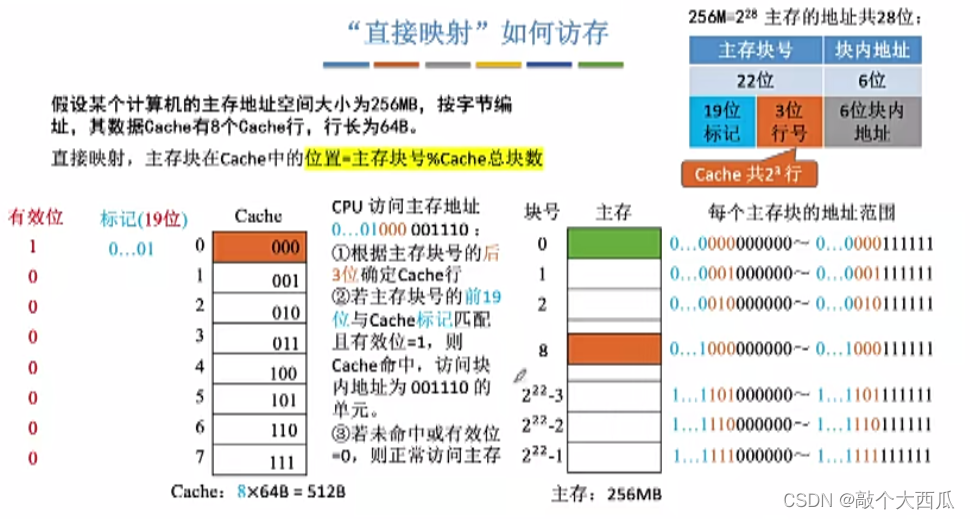

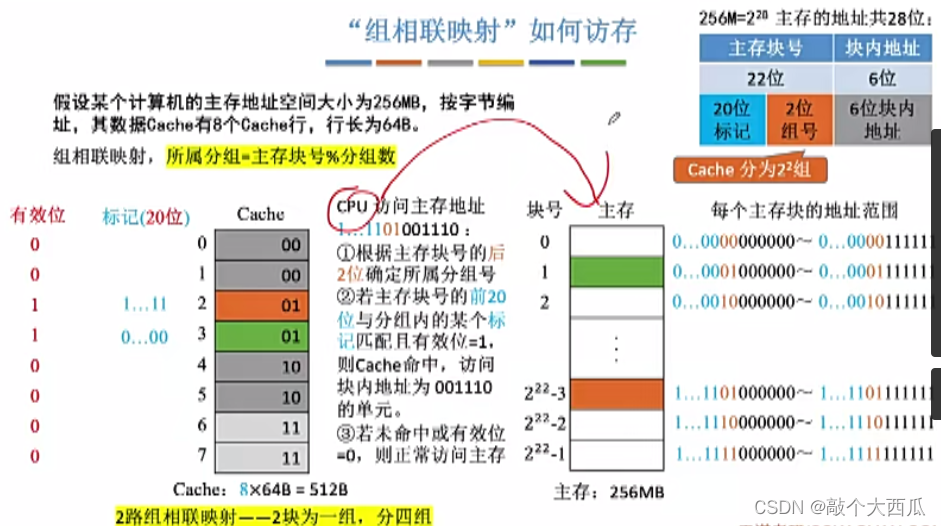

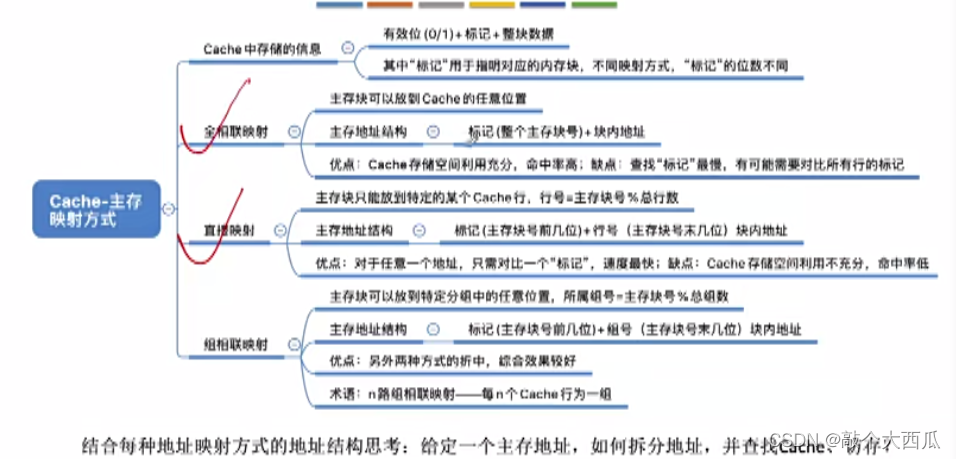

cache和主存的映射方式

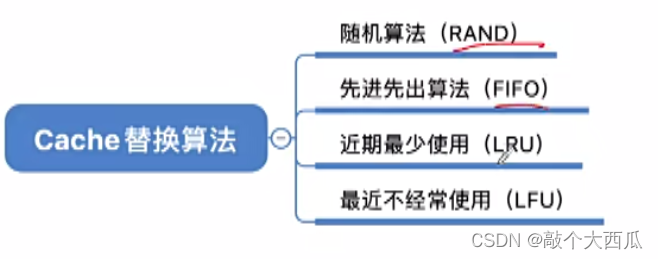

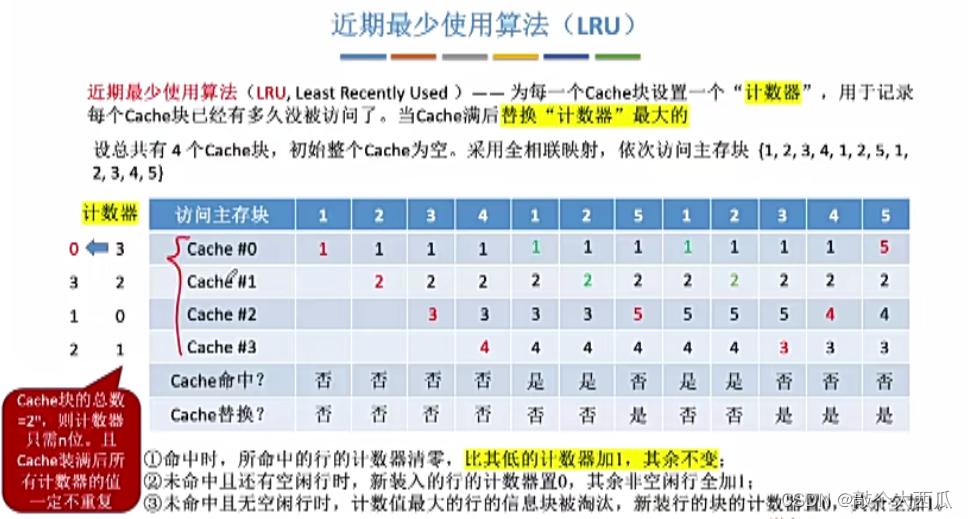

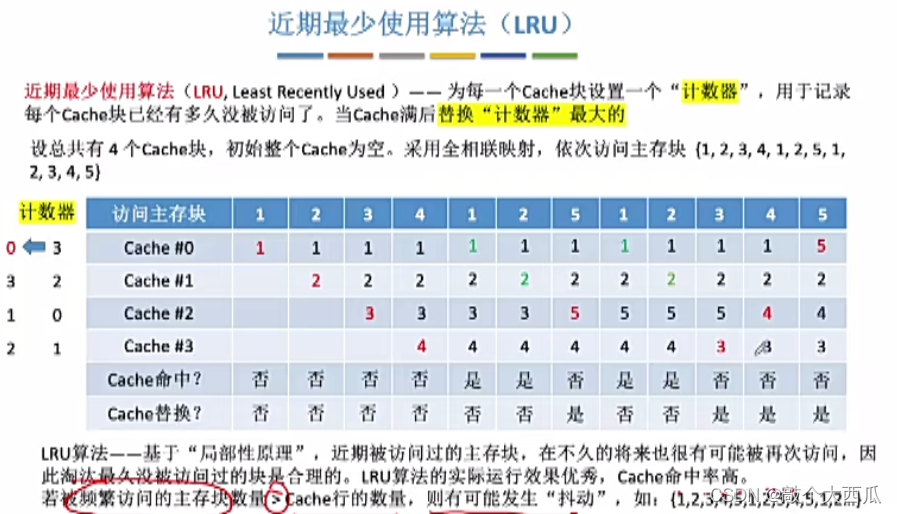

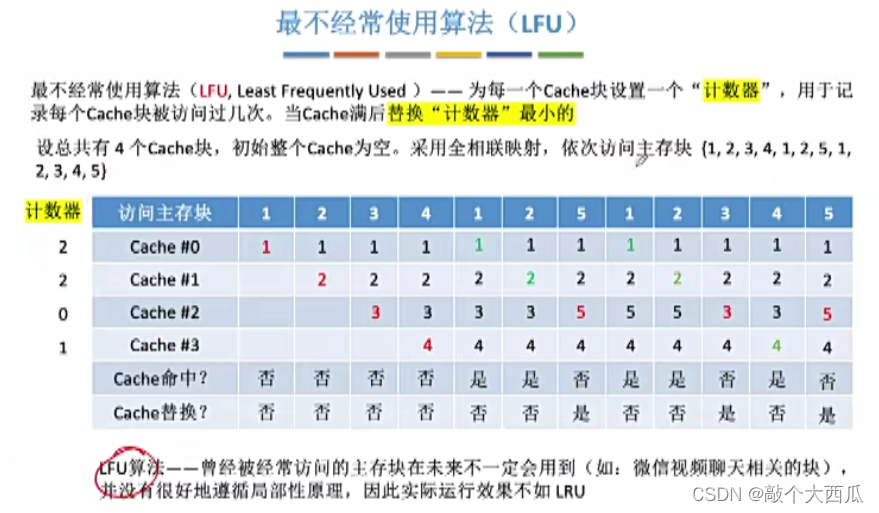

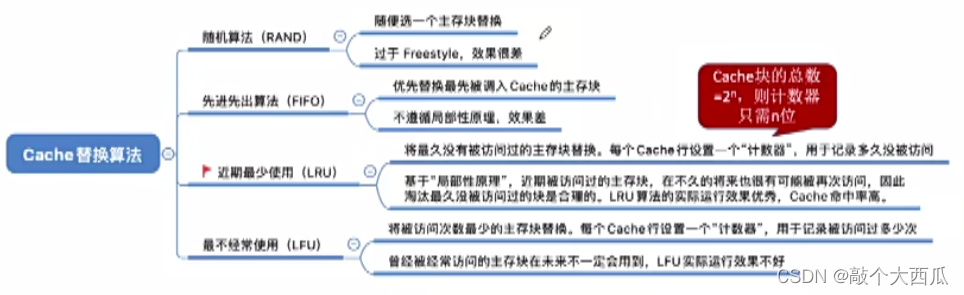

cache替换算法

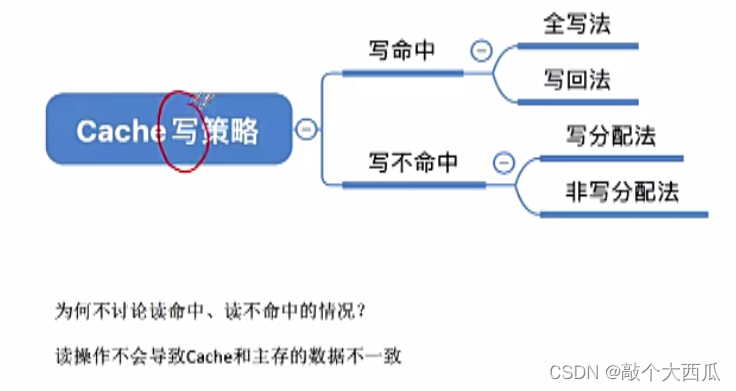

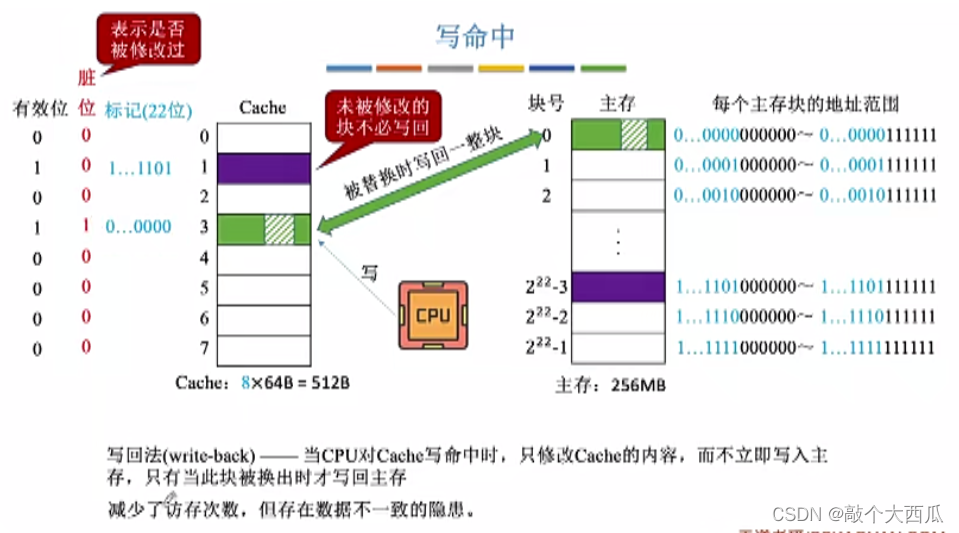

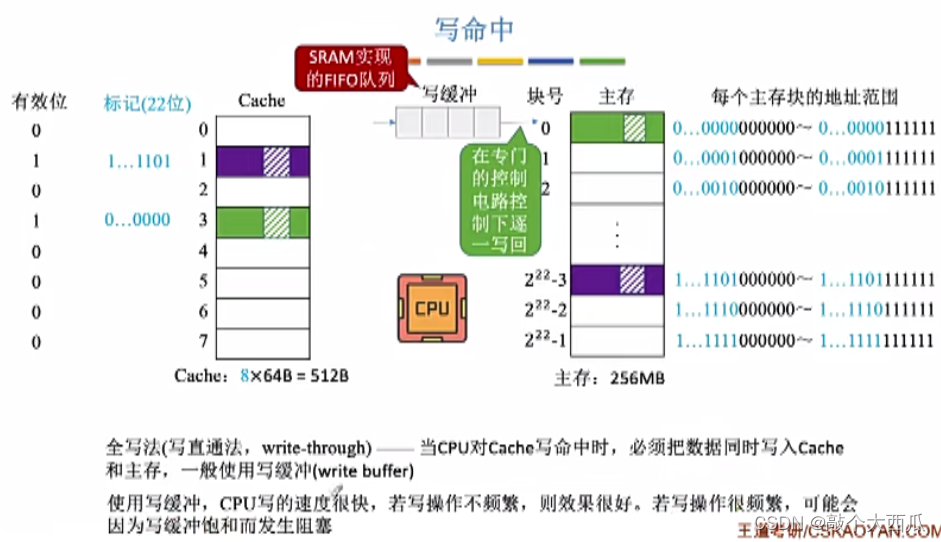

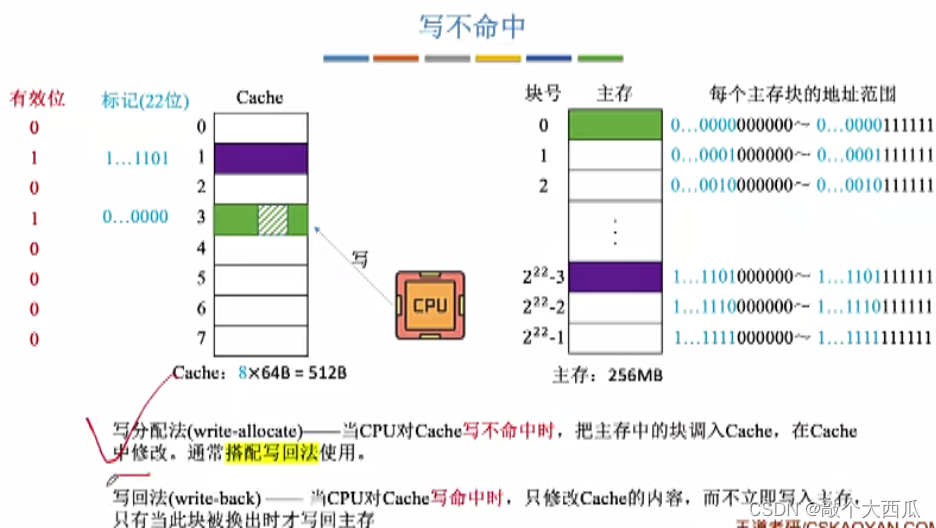

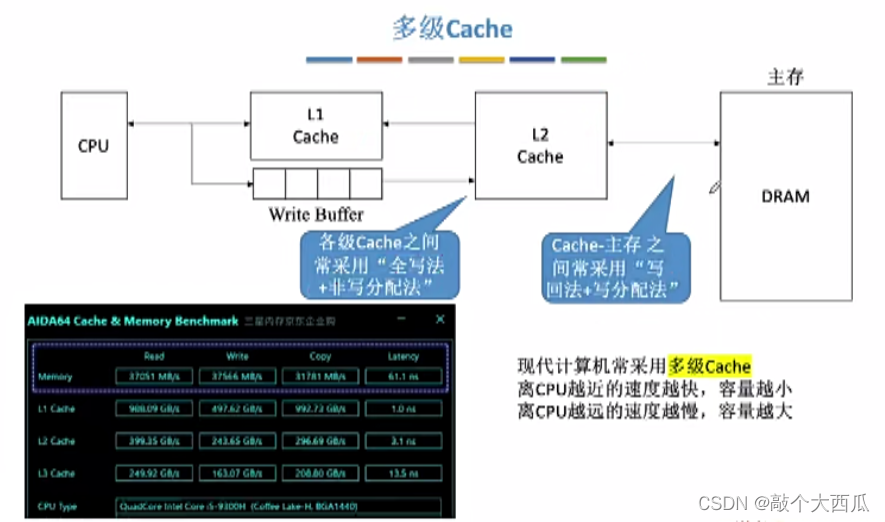

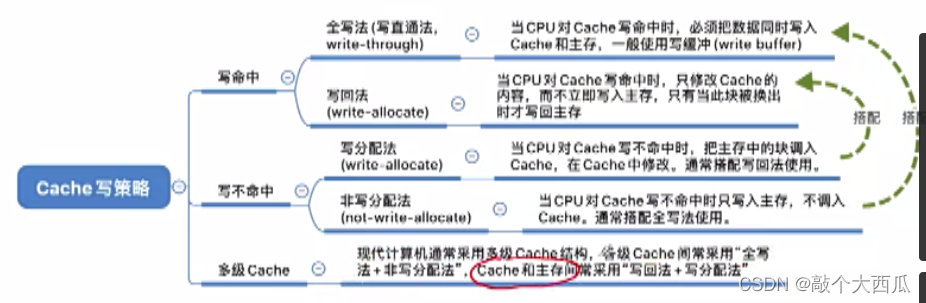

cache写策略

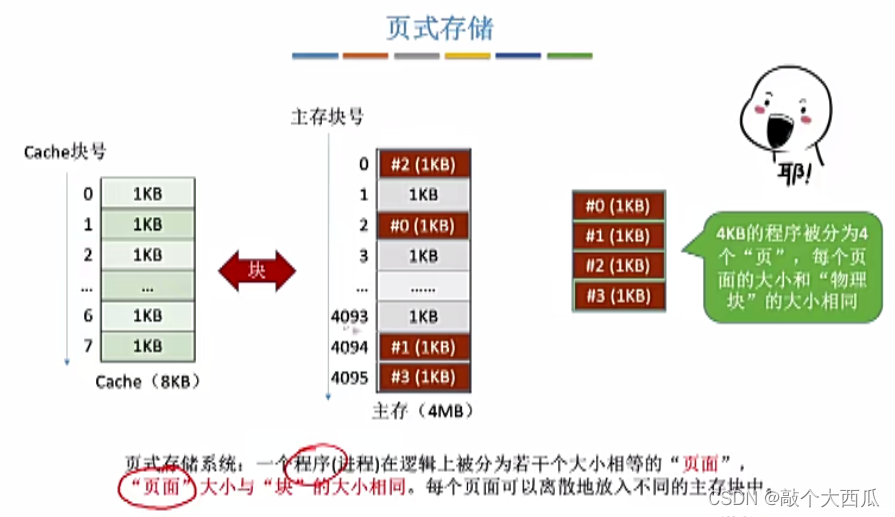

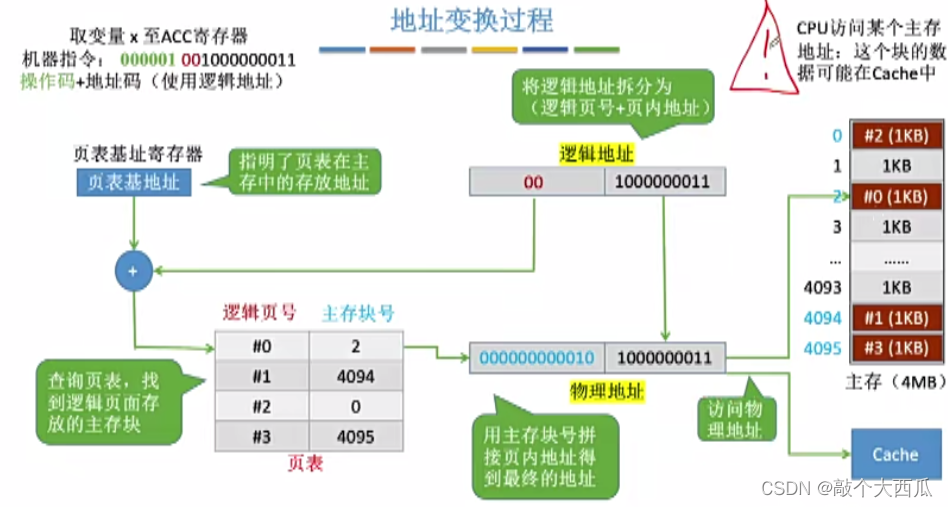

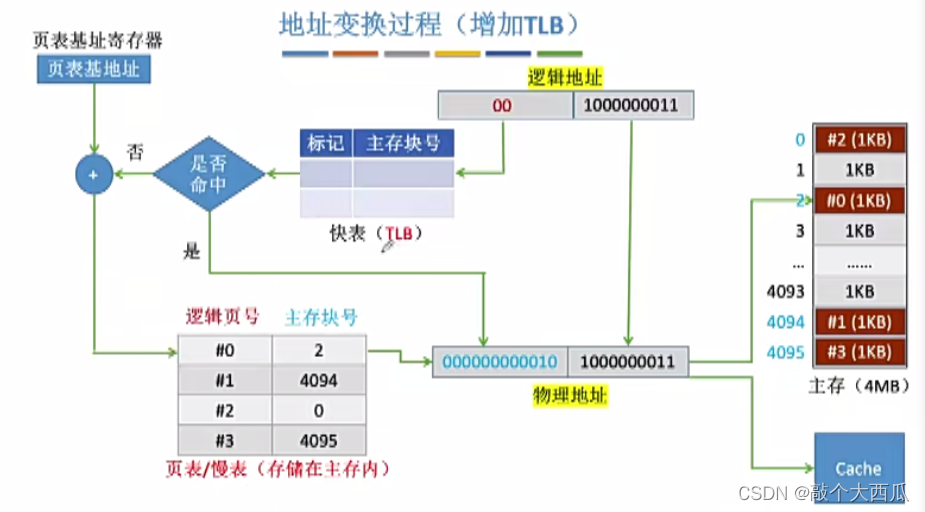

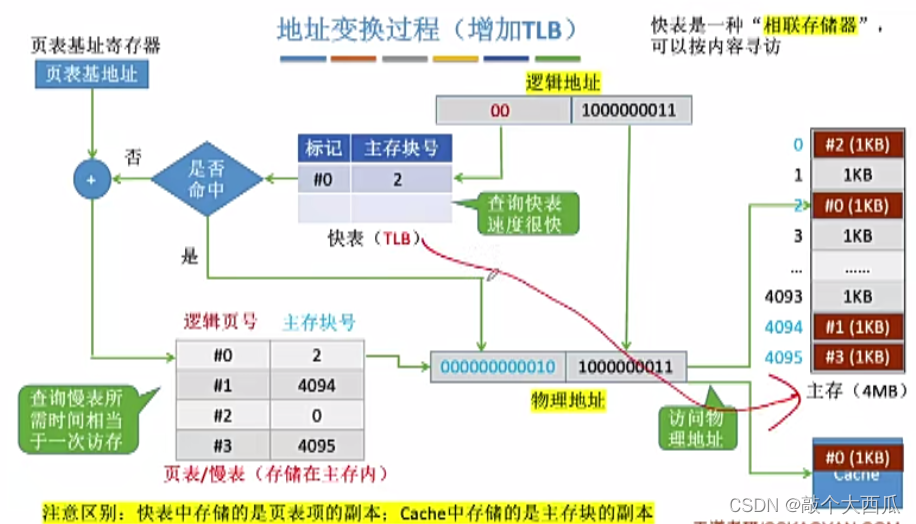

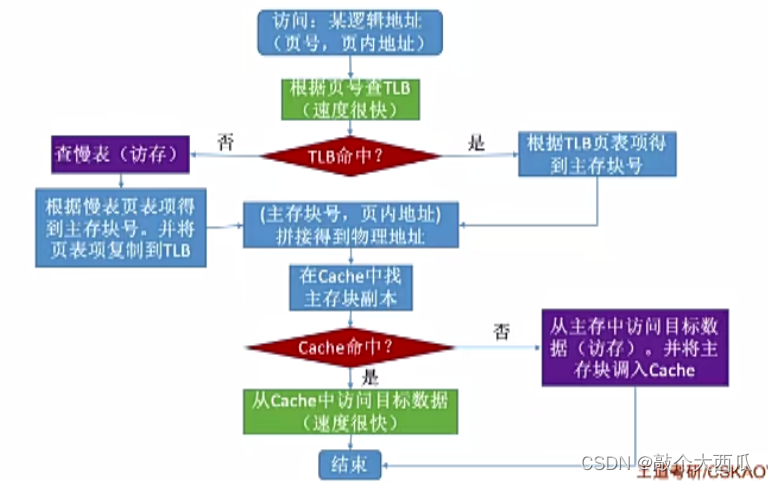

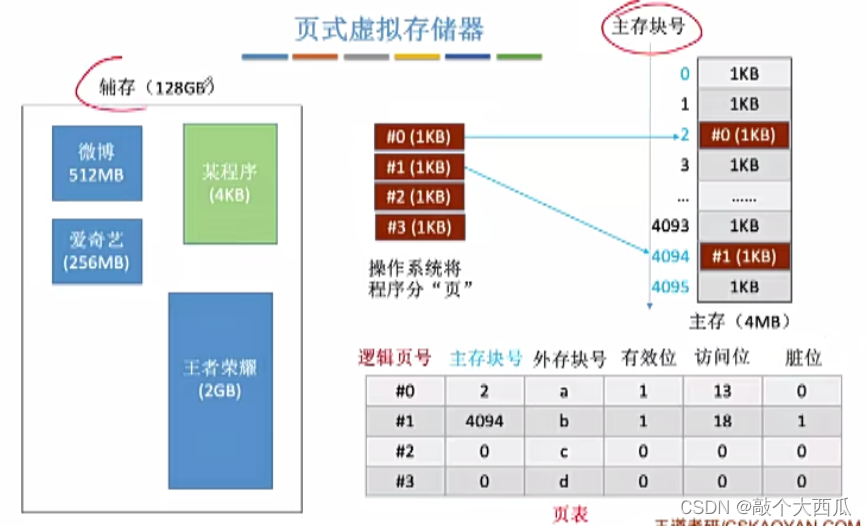

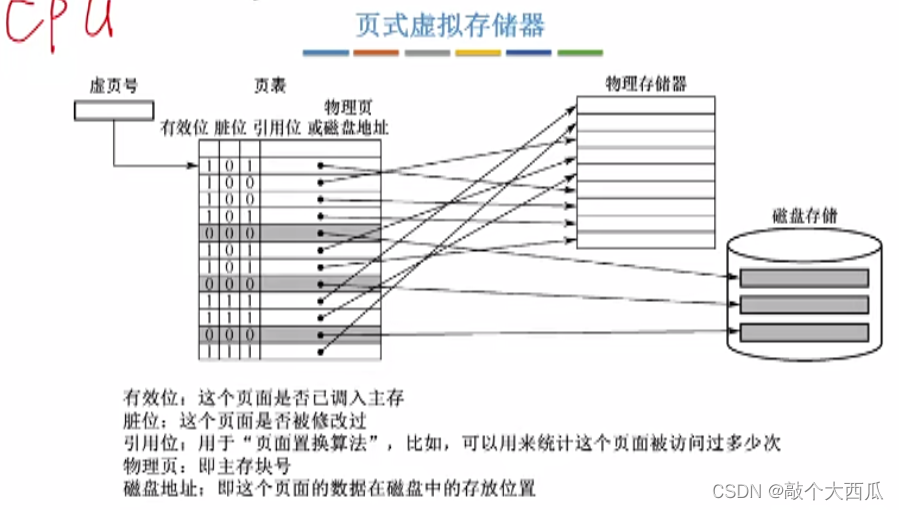

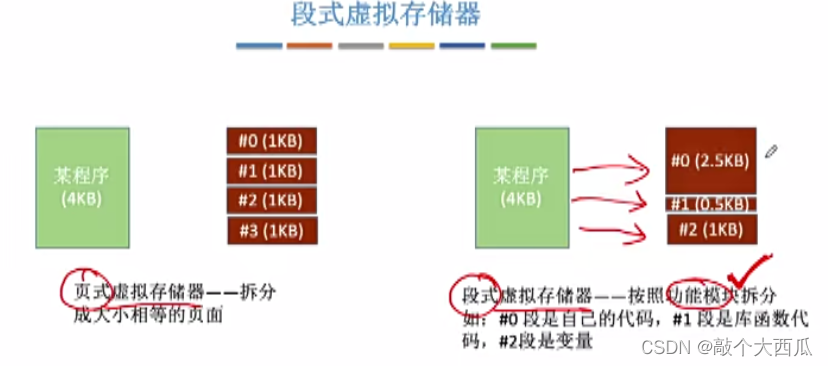

页式存储器

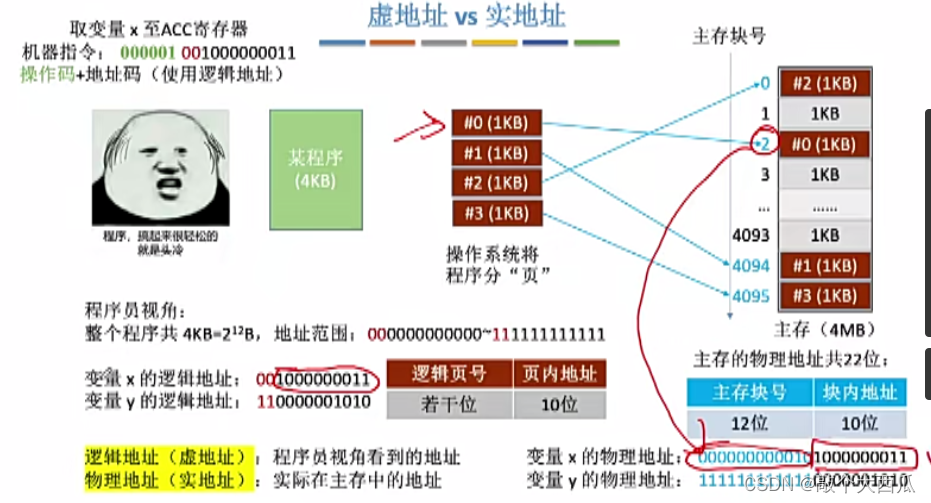

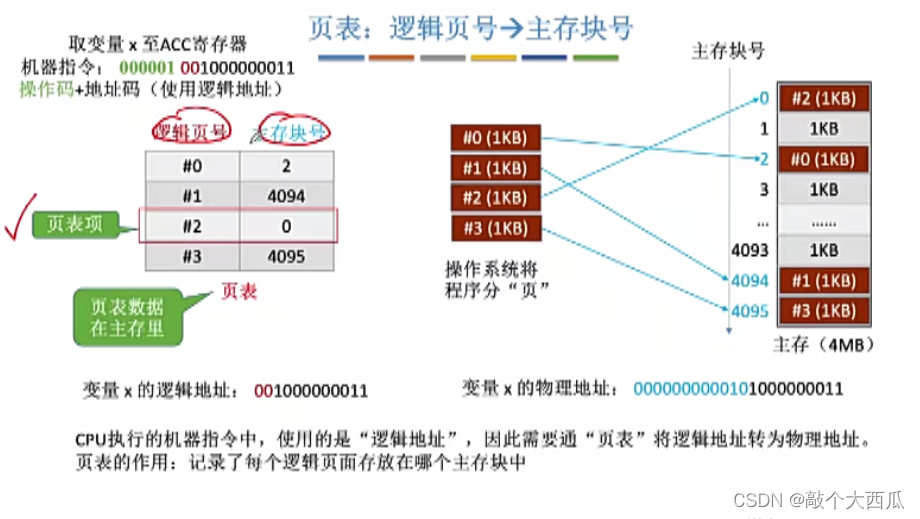

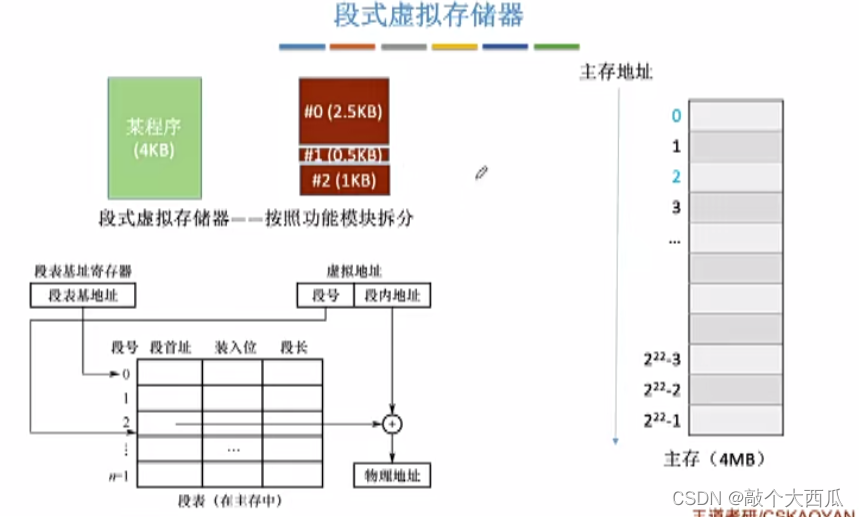

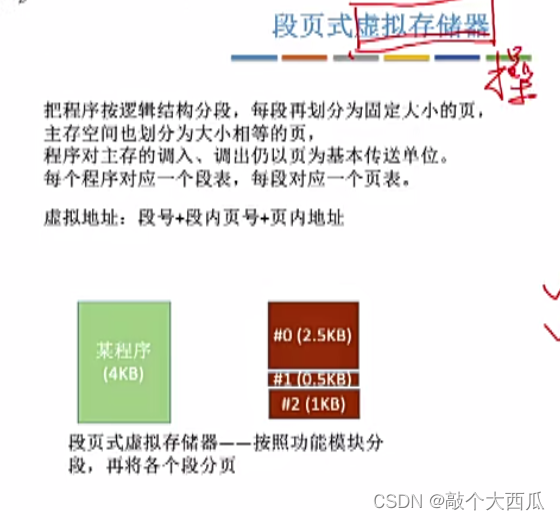

虚拟存储器

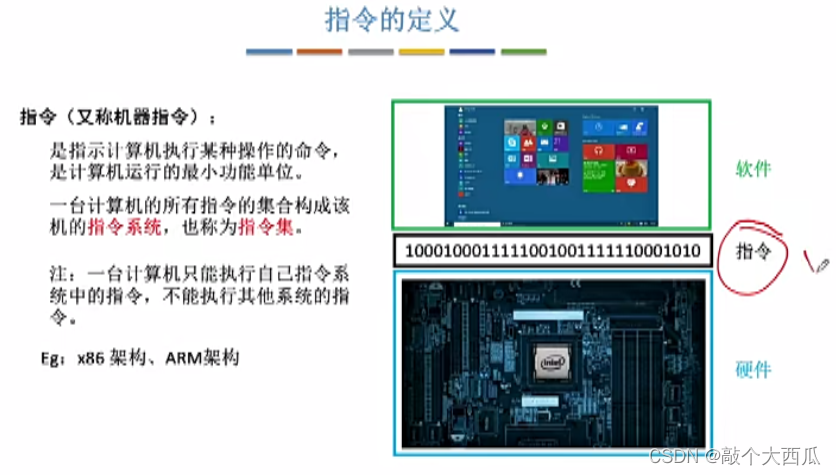

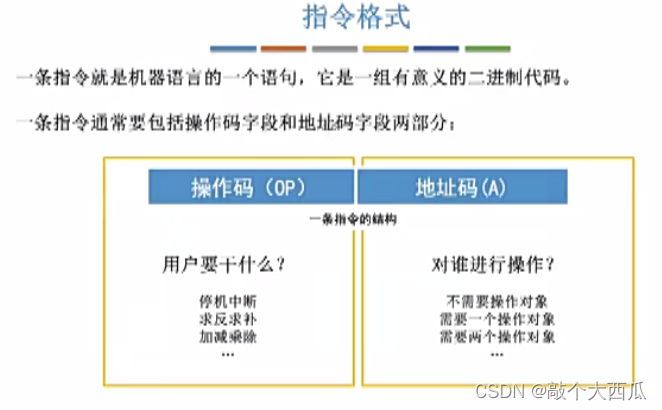

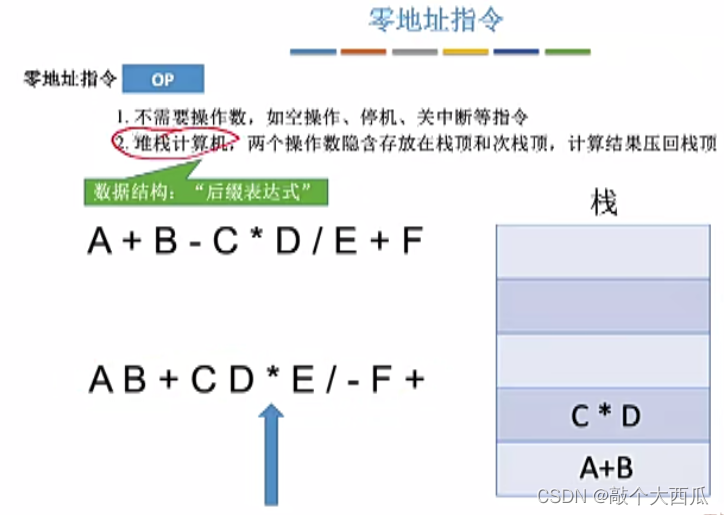

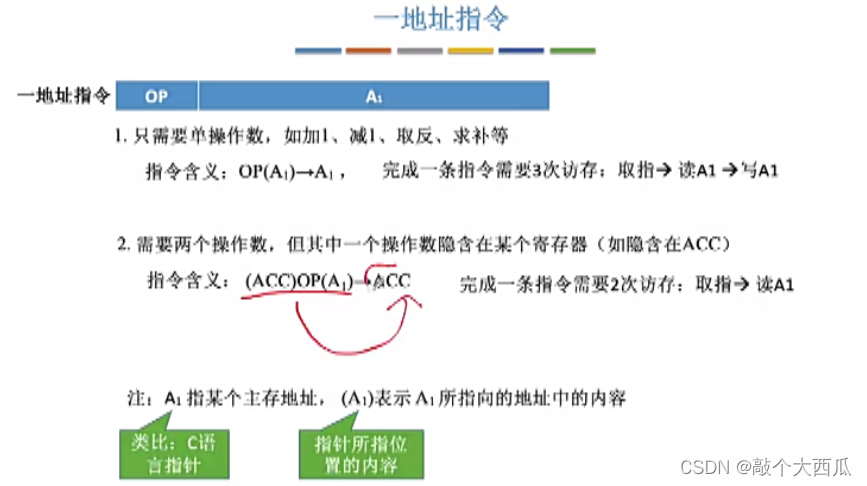

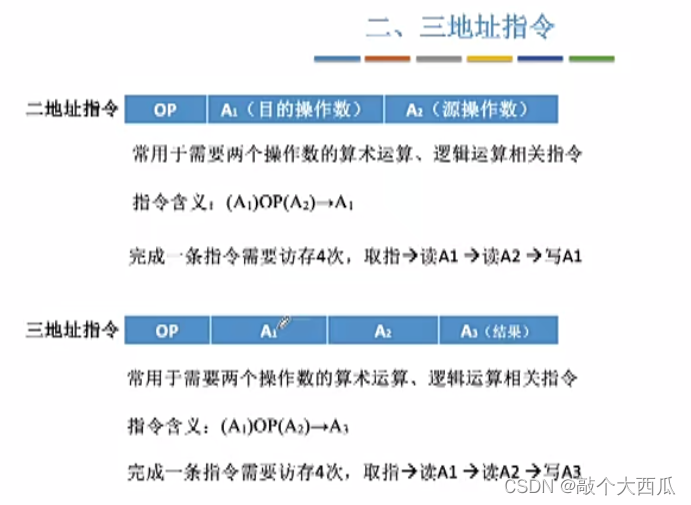

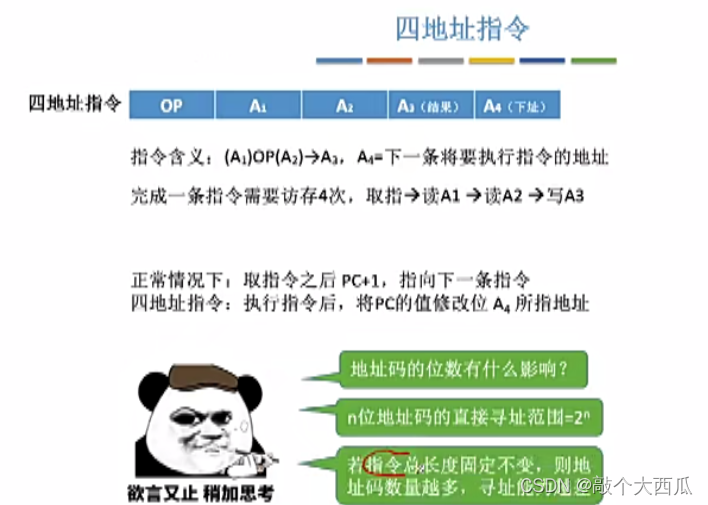

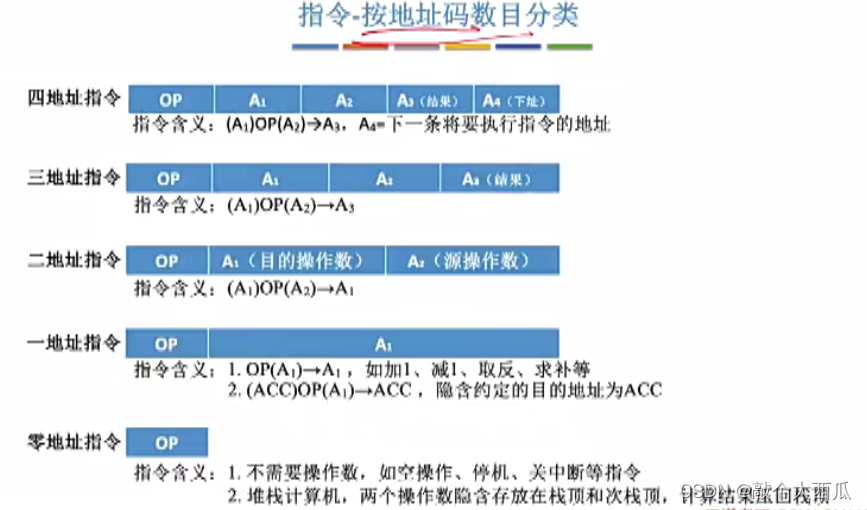

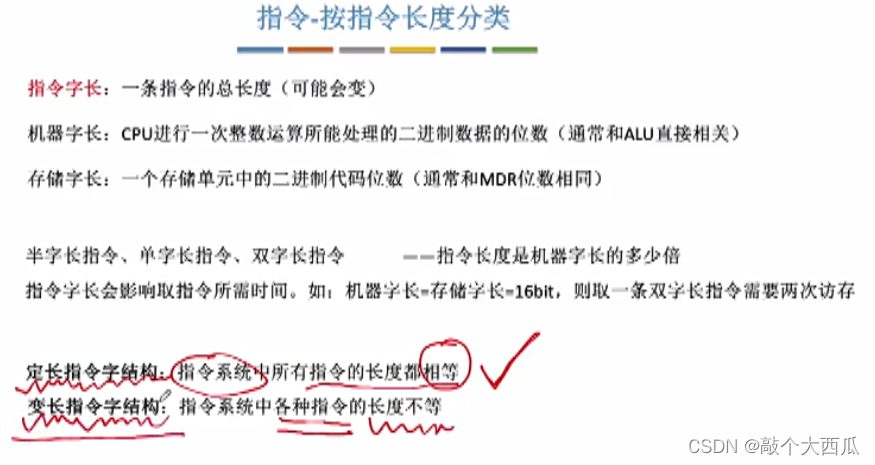

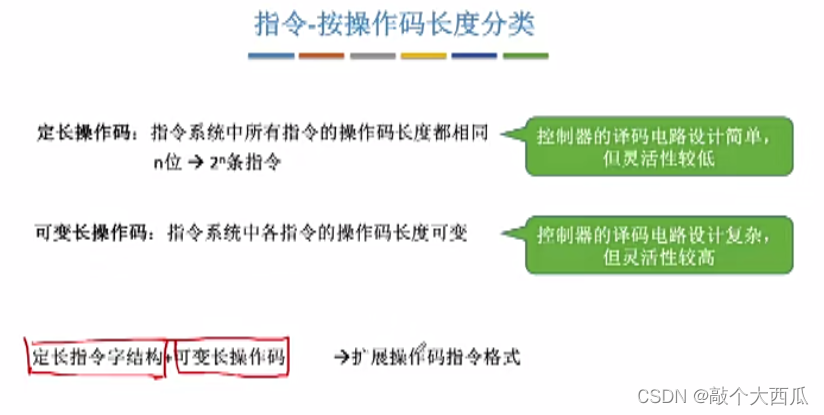

第四章 指令格式

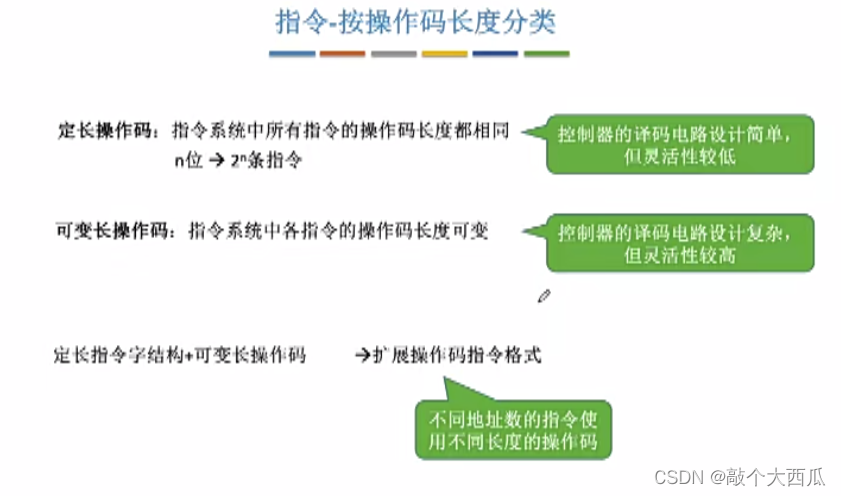

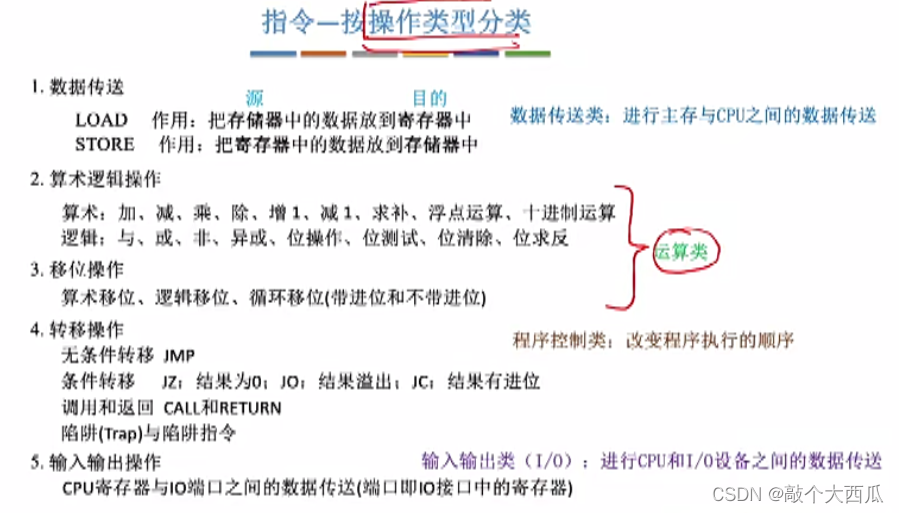

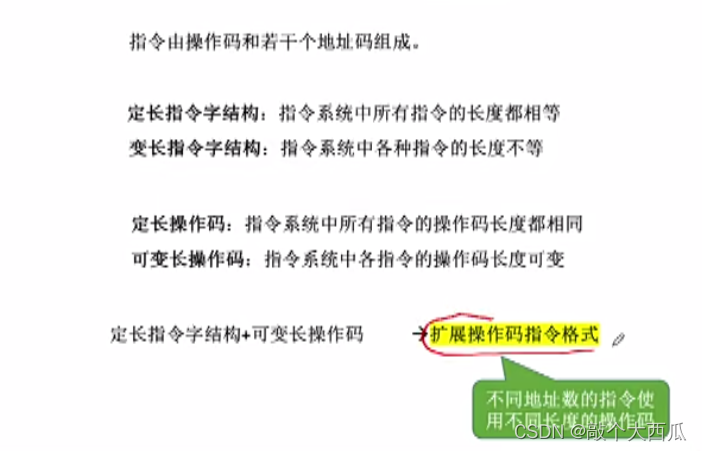

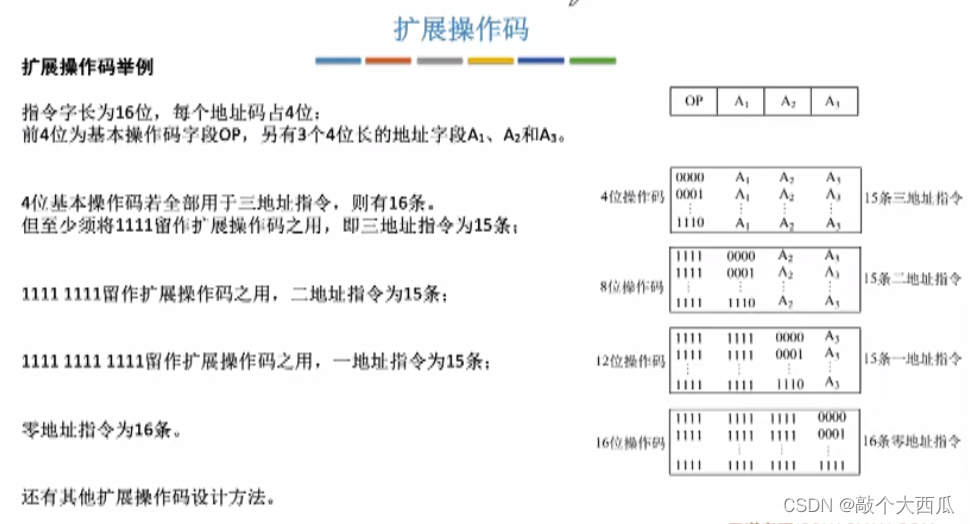

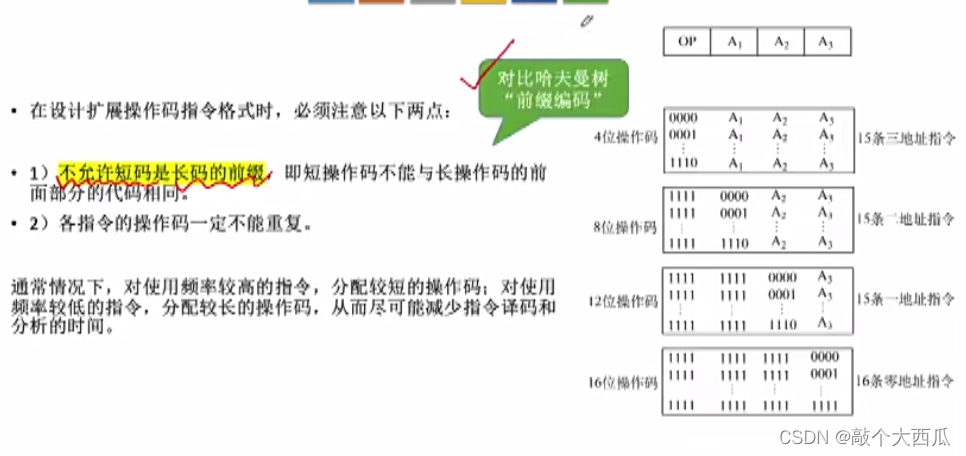

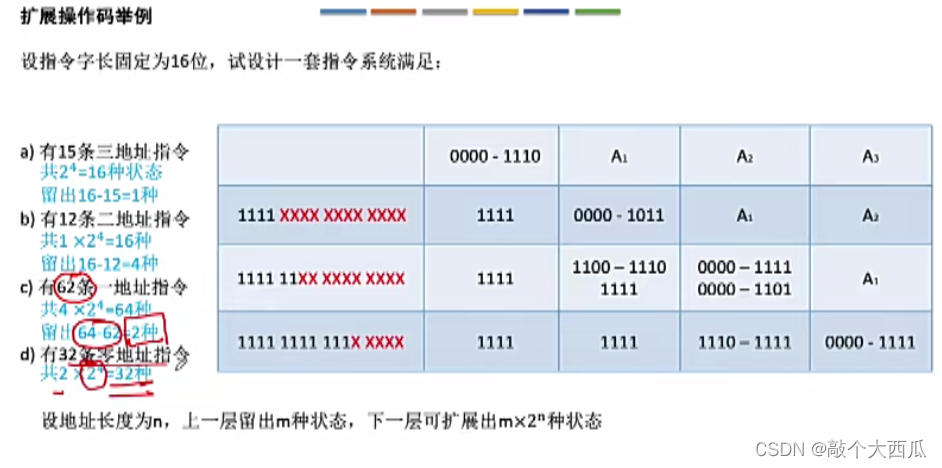

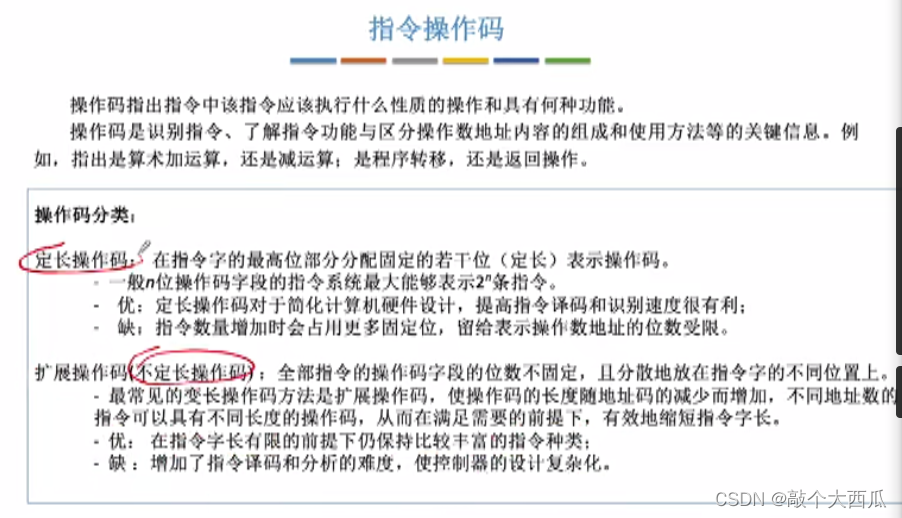

扩展操作吗指令格式

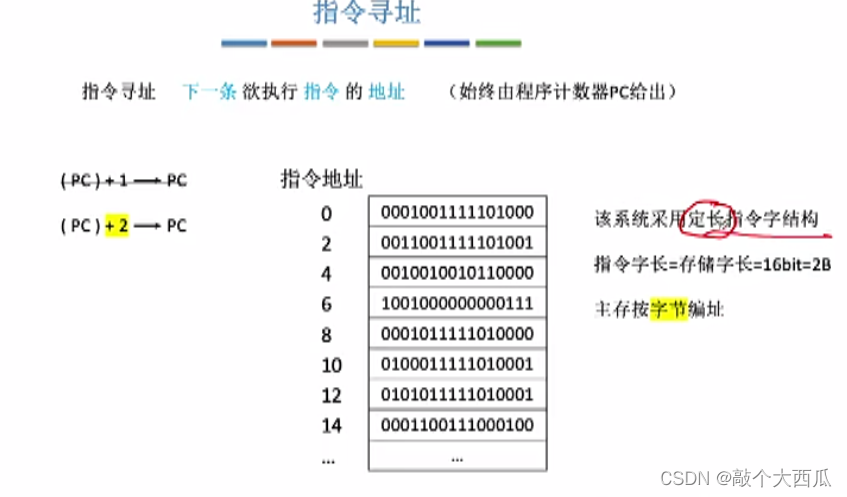

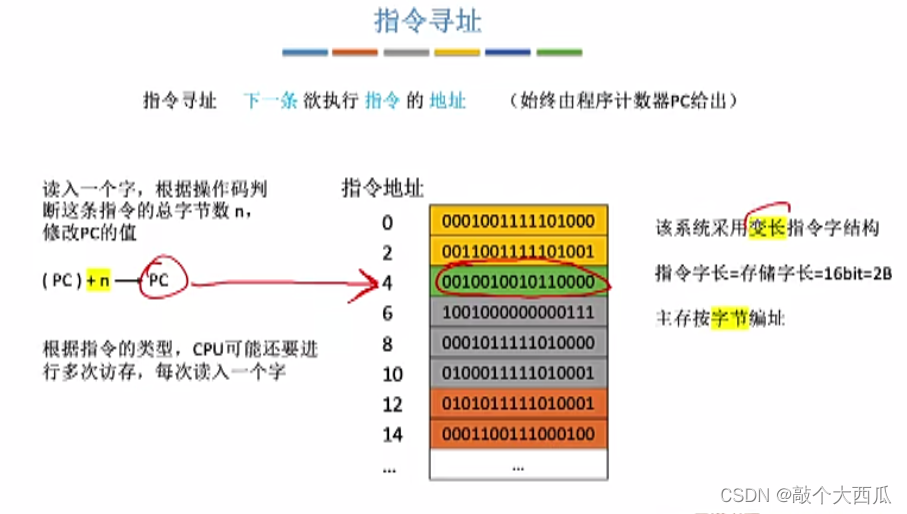

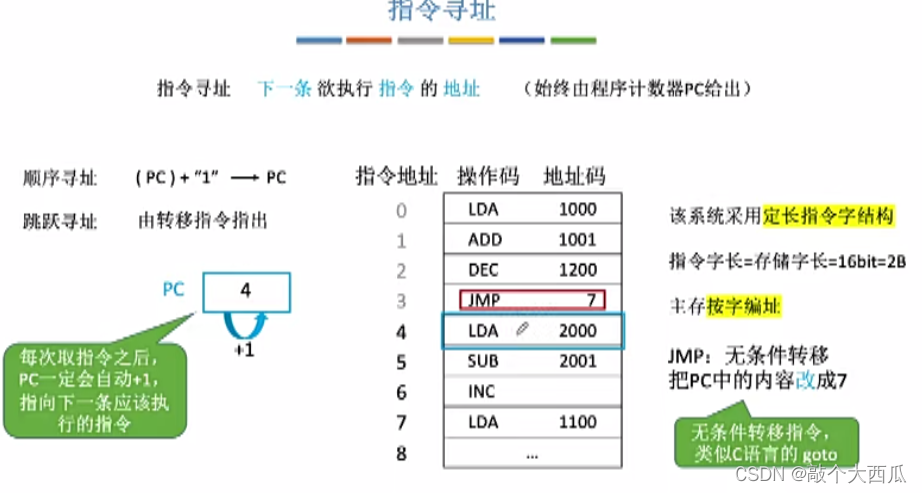

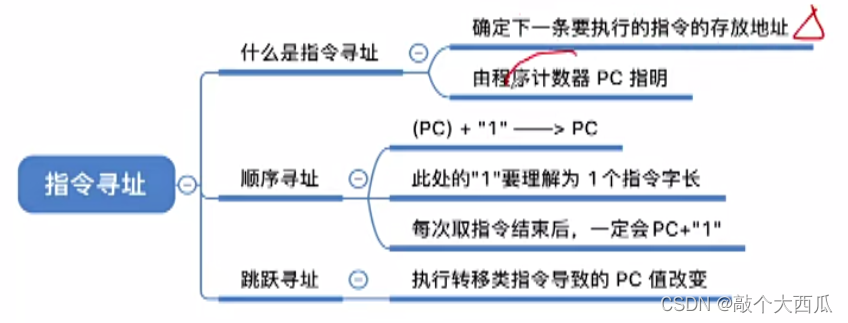

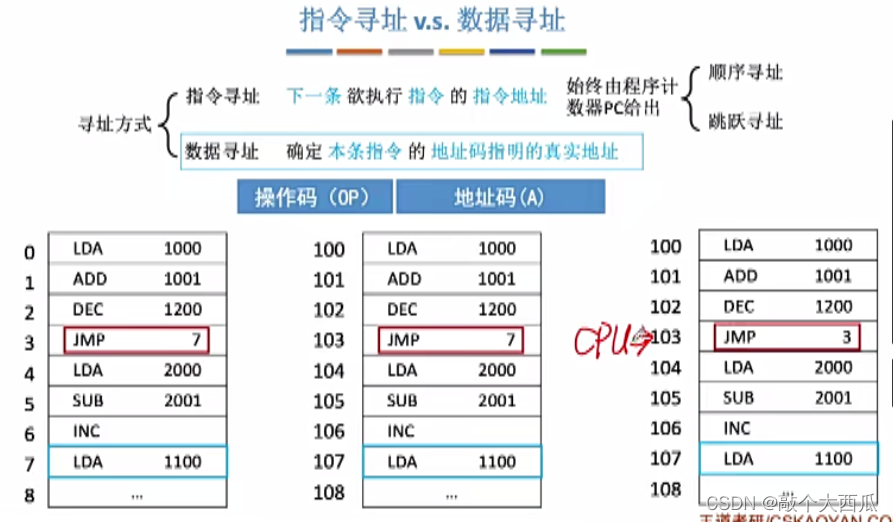

指令寻址

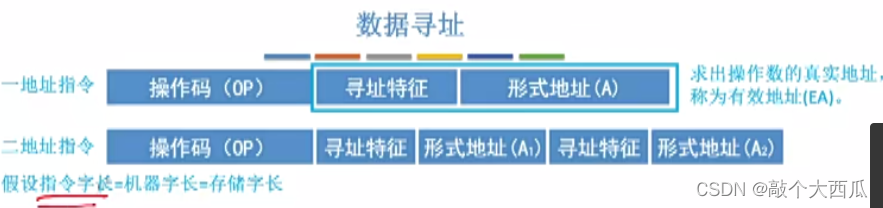

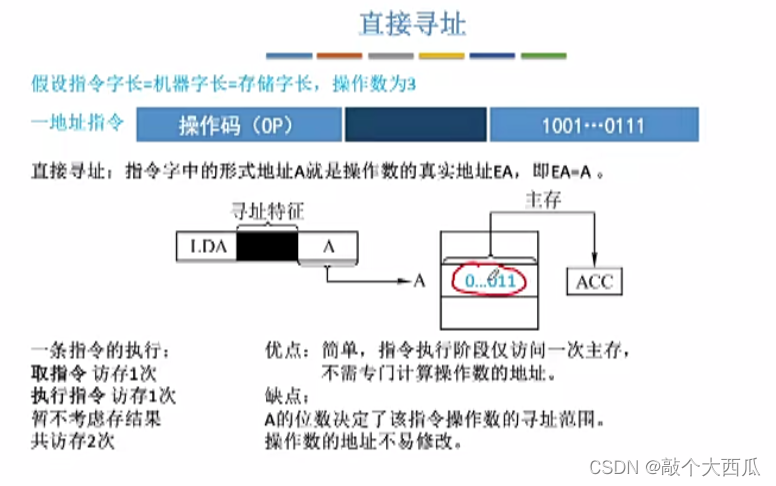

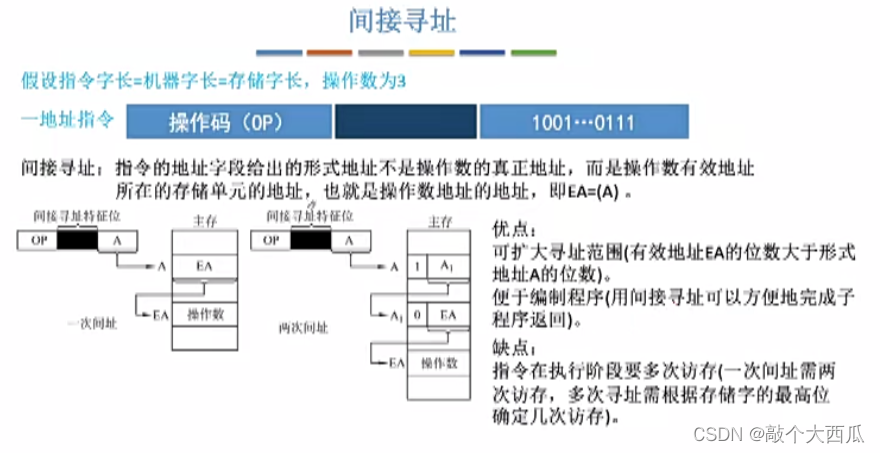

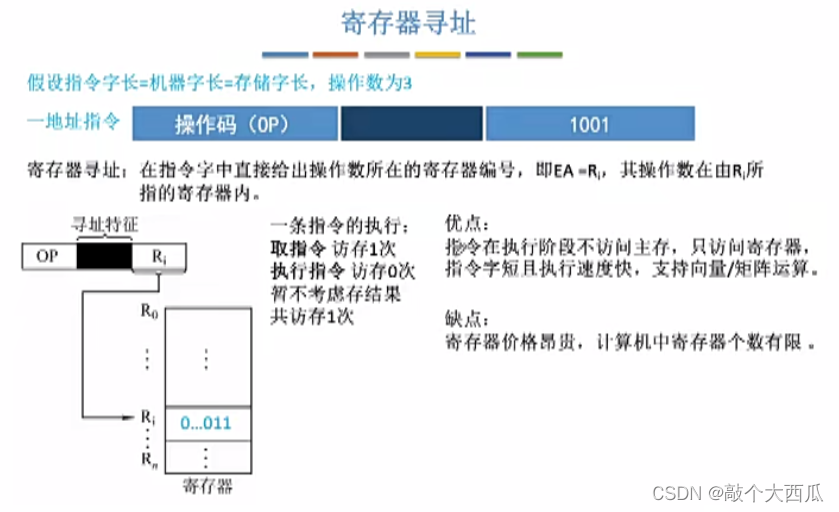

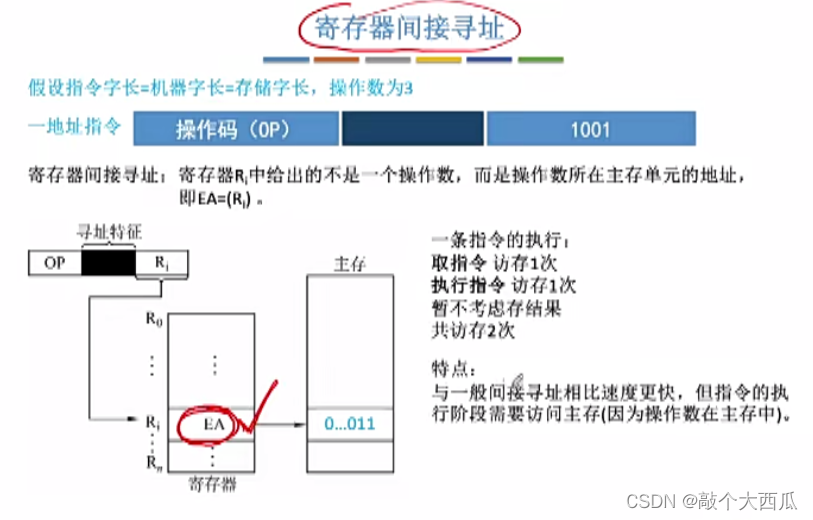

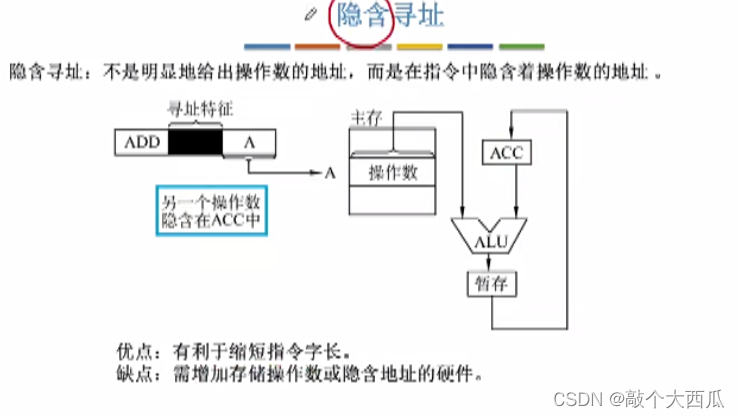

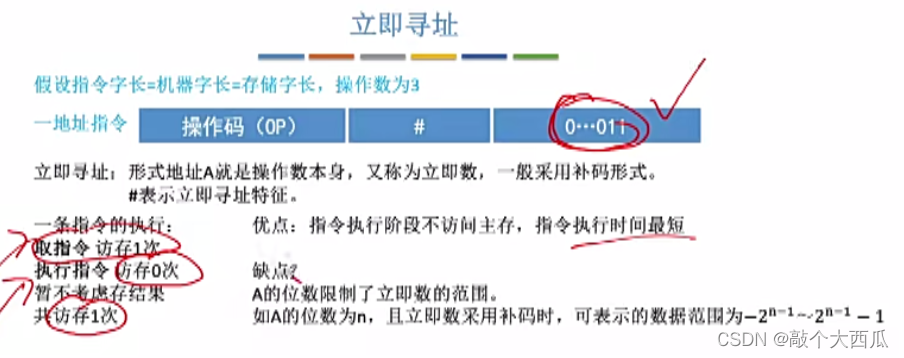

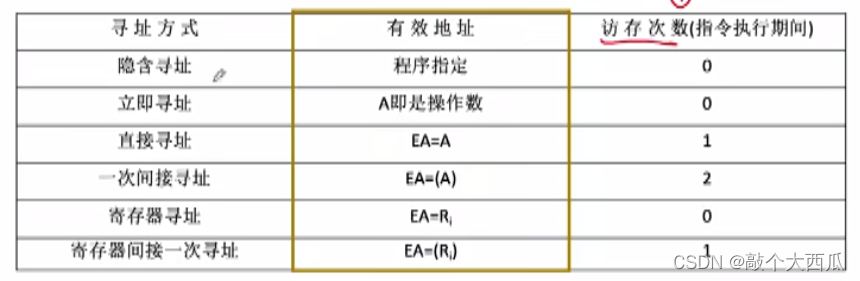

数据寻址

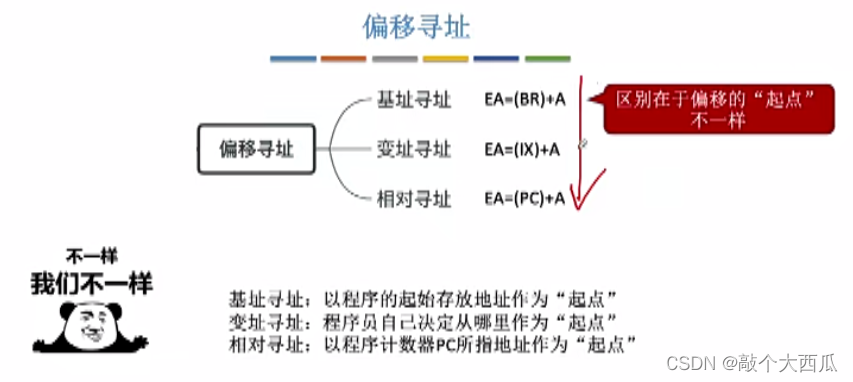

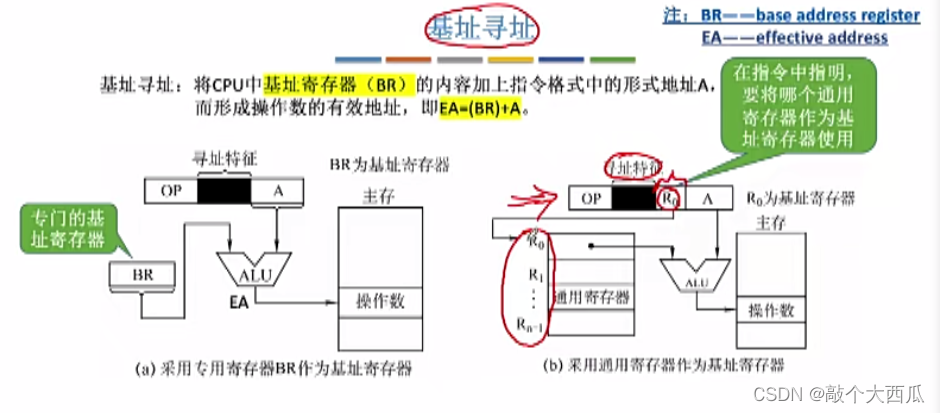

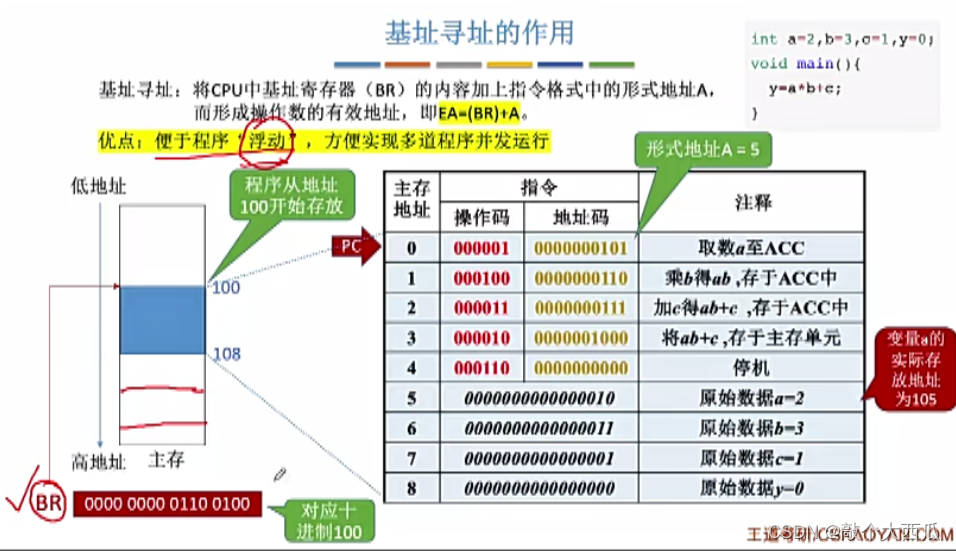

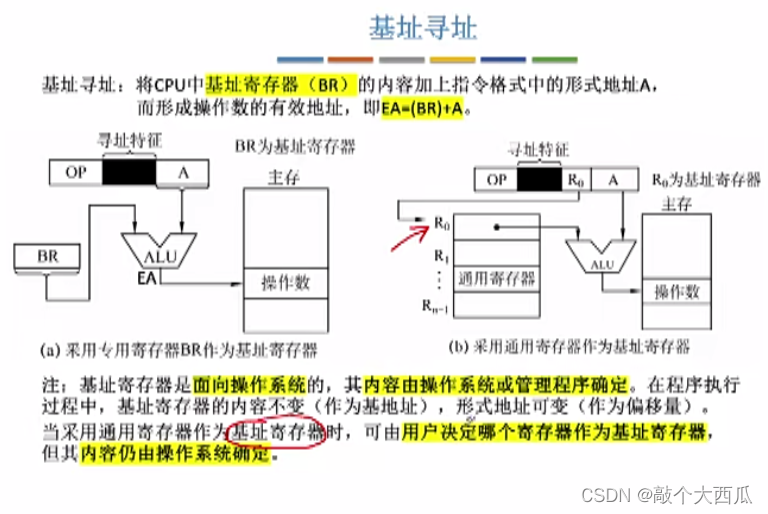

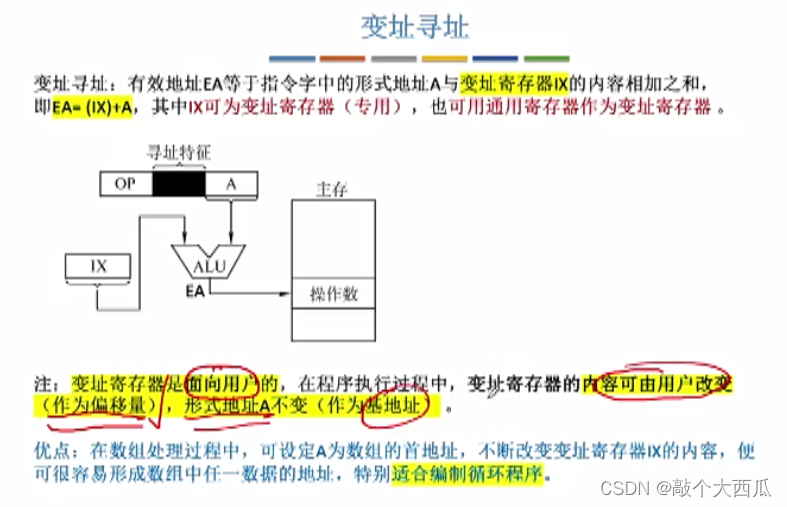

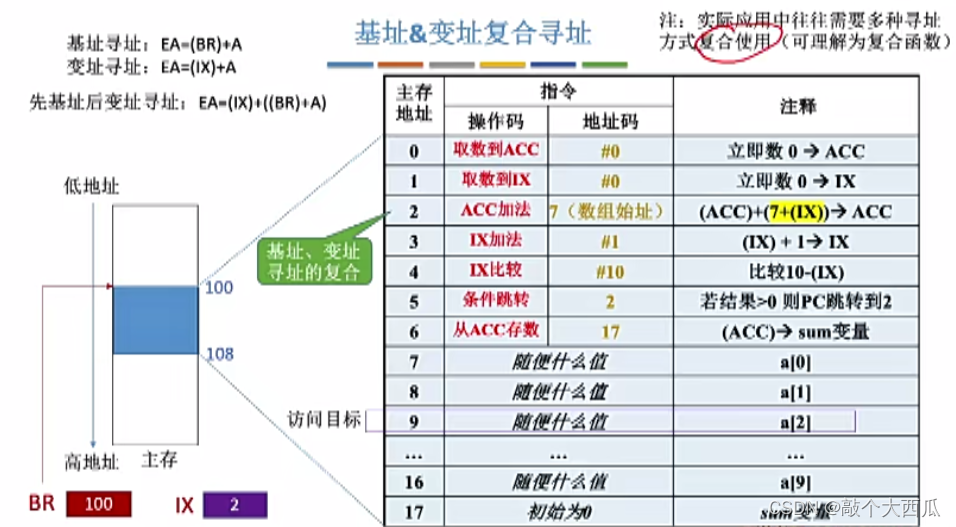

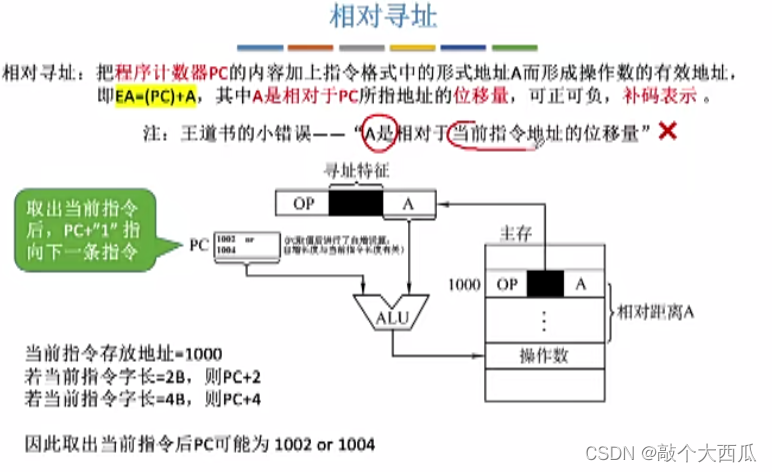

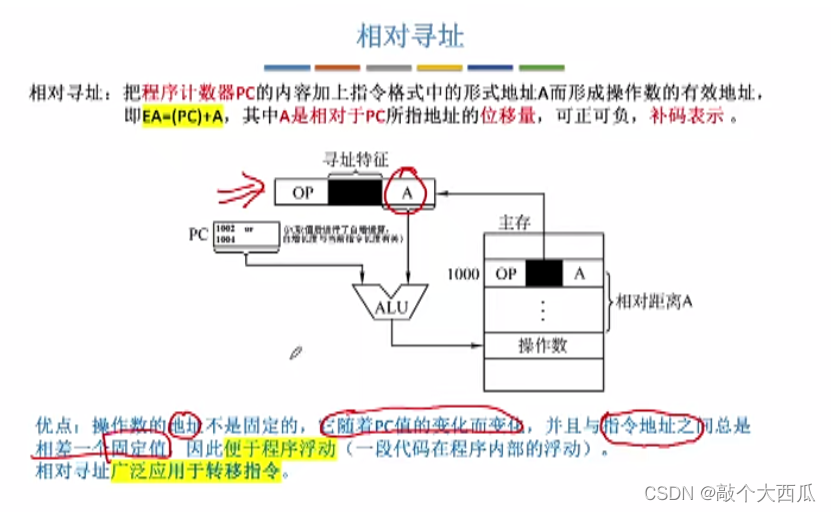

数据寻址-偏移寻址

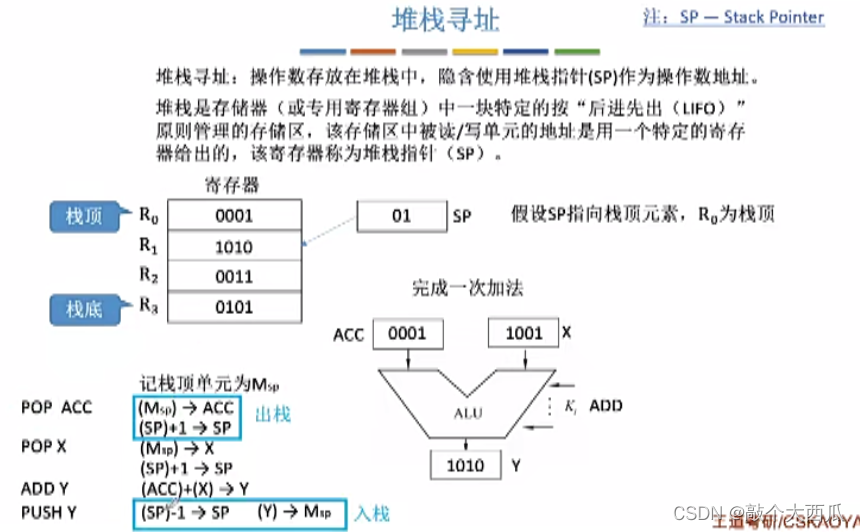

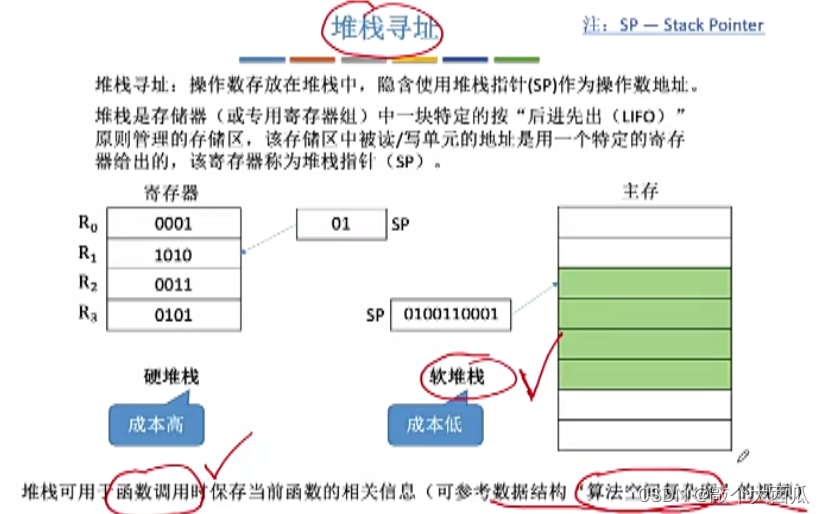

数据寻址-堆栈寻址

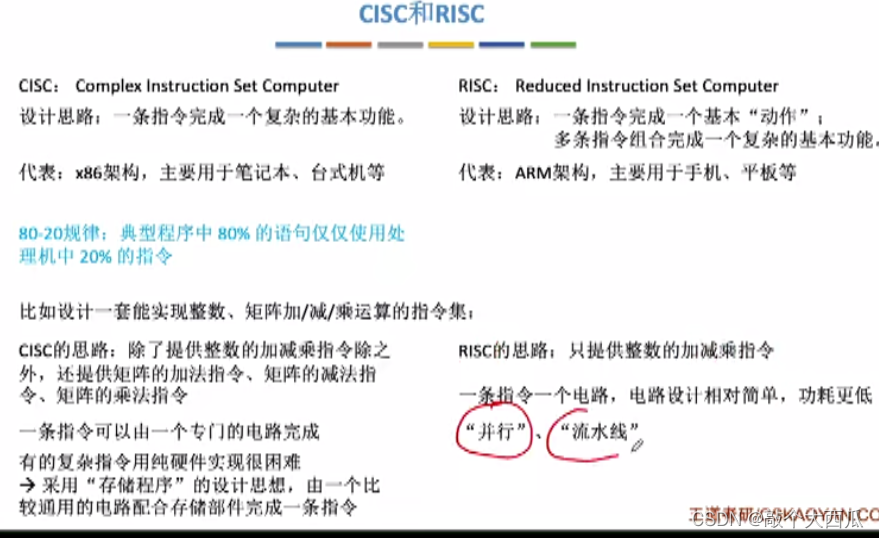

CIRC和RISC

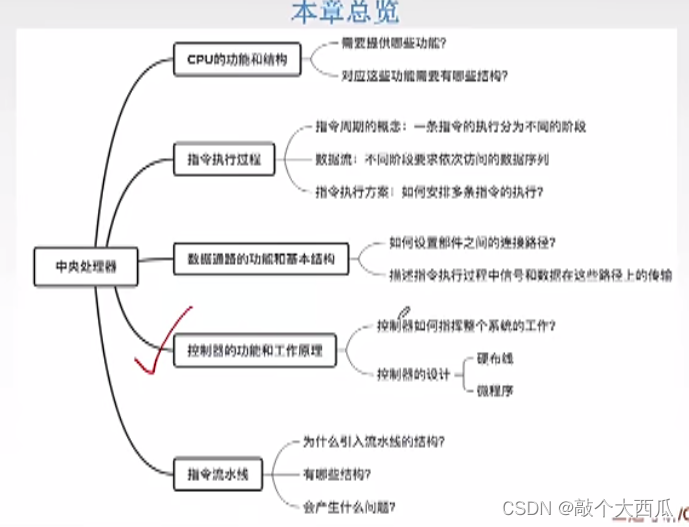

第五章 中央处理器

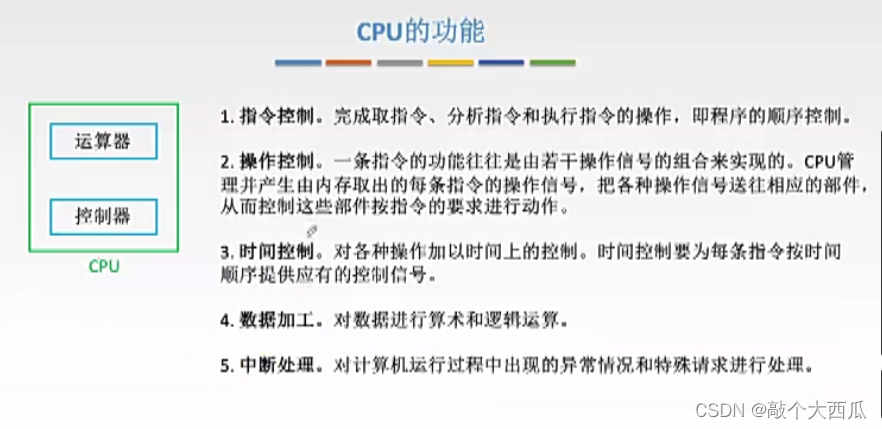

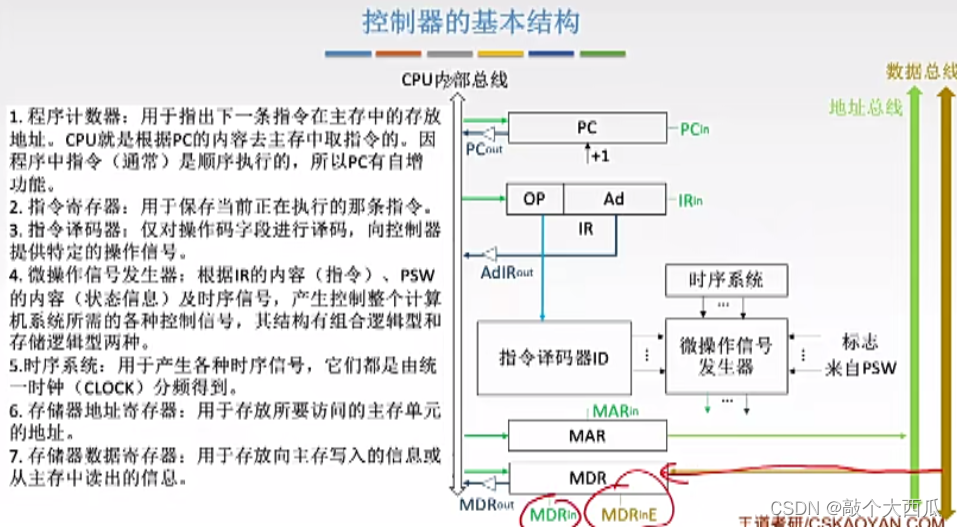

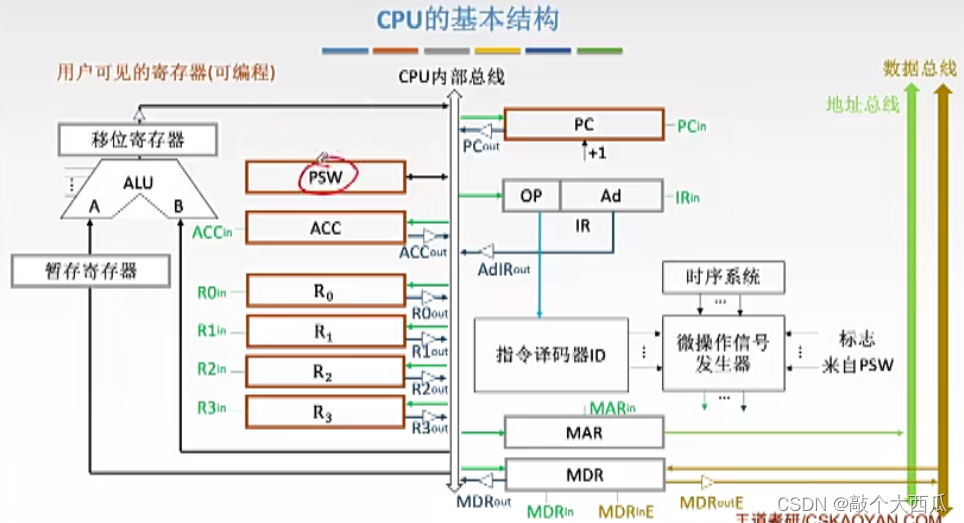

CPU的功能和基本结构

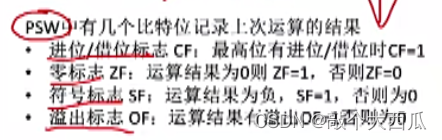

用户(所有程序员)可见:PSW、通用寄存器、PC

用户(所有程序员)透明:MAR、MDR、IR、Cache、微程序的结构和功能

应用程序员透明:暂存寄存器、虚拟存储器

汇编程序员可见:PC

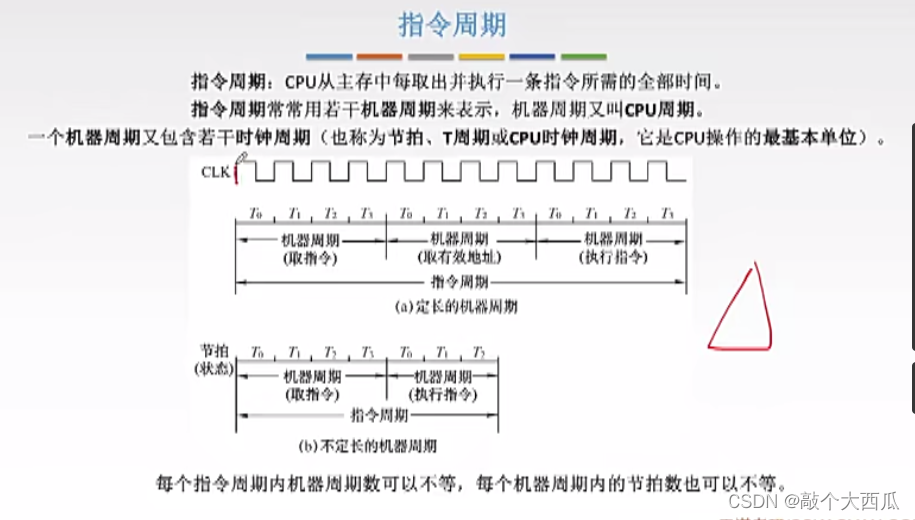

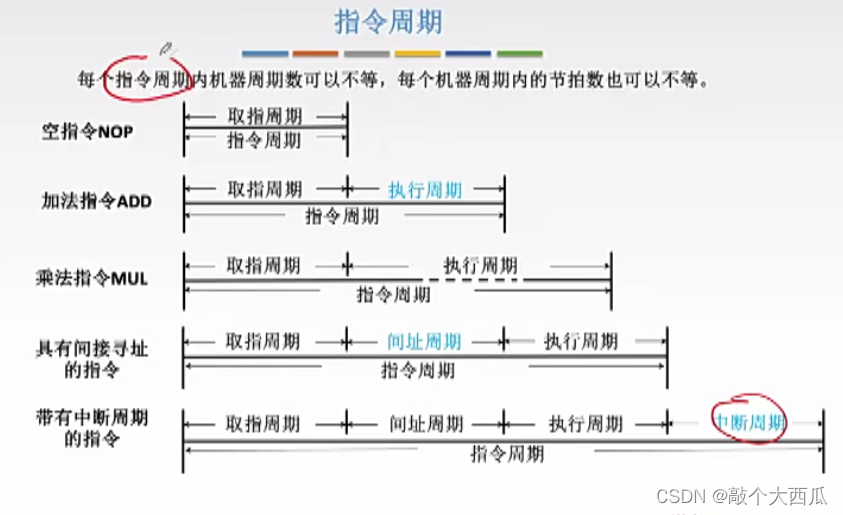

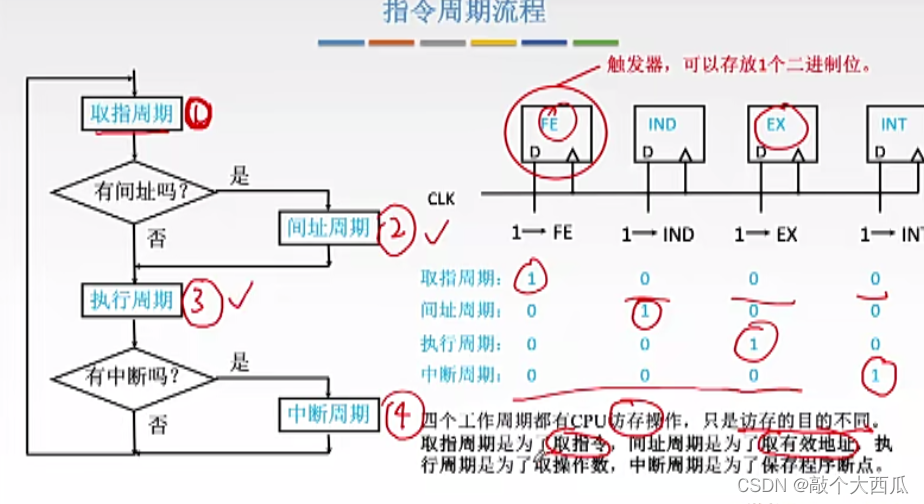

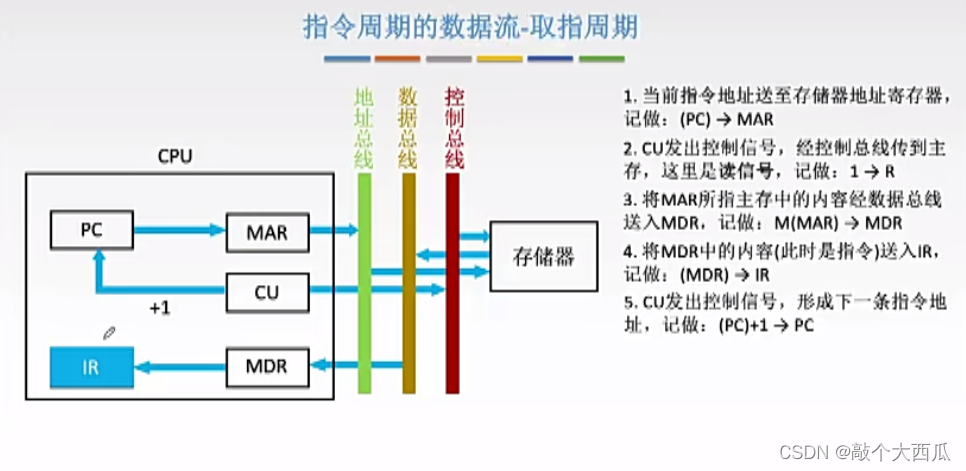

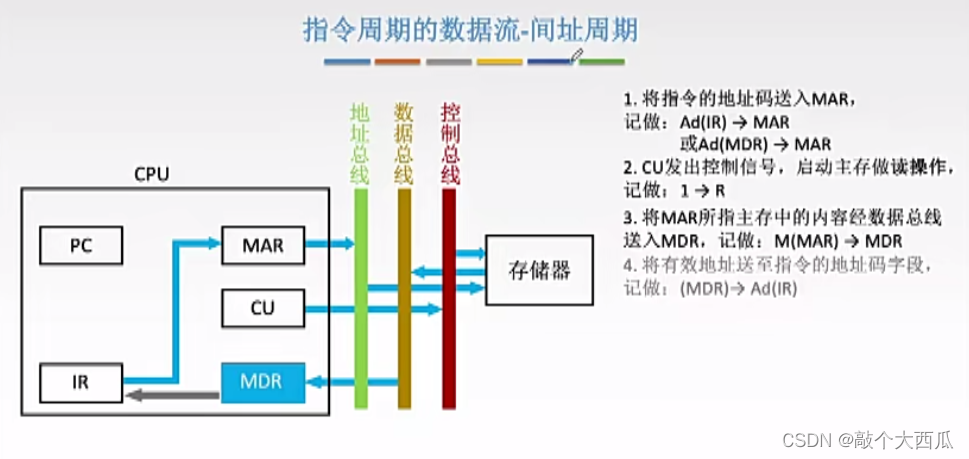

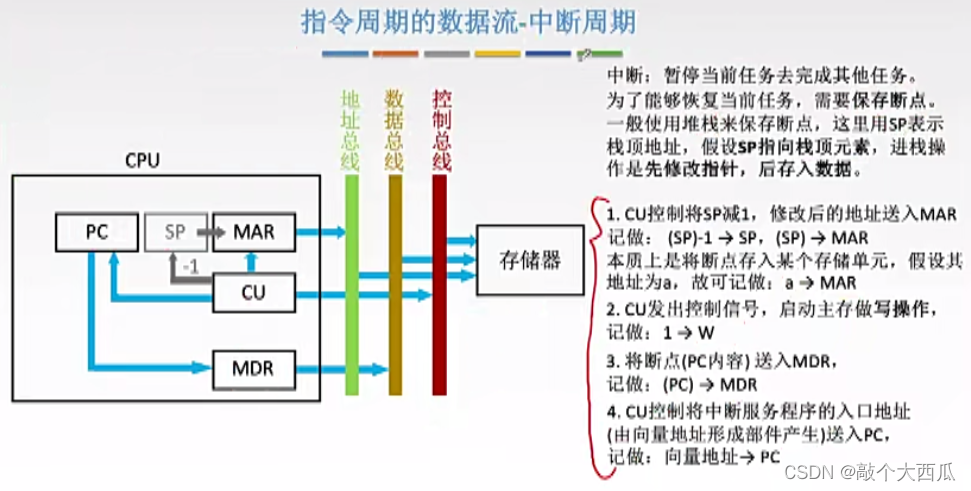

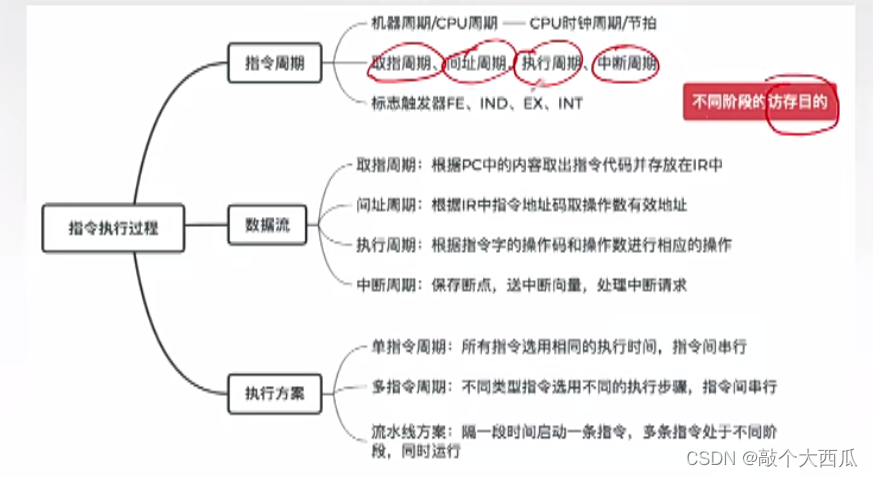

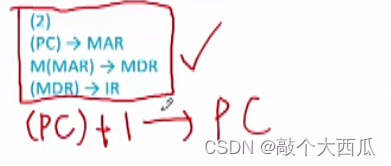

系统程序员可见:虚拟存储器指令周期的数据流

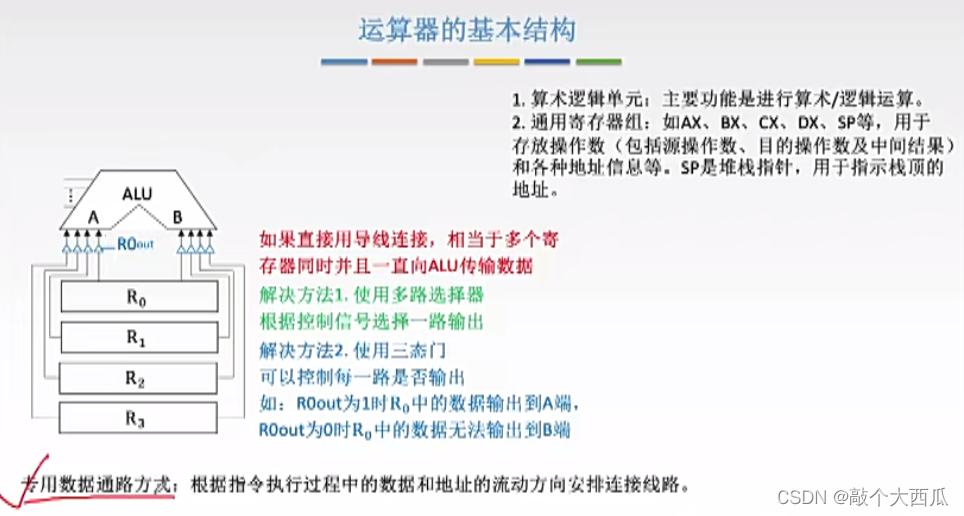

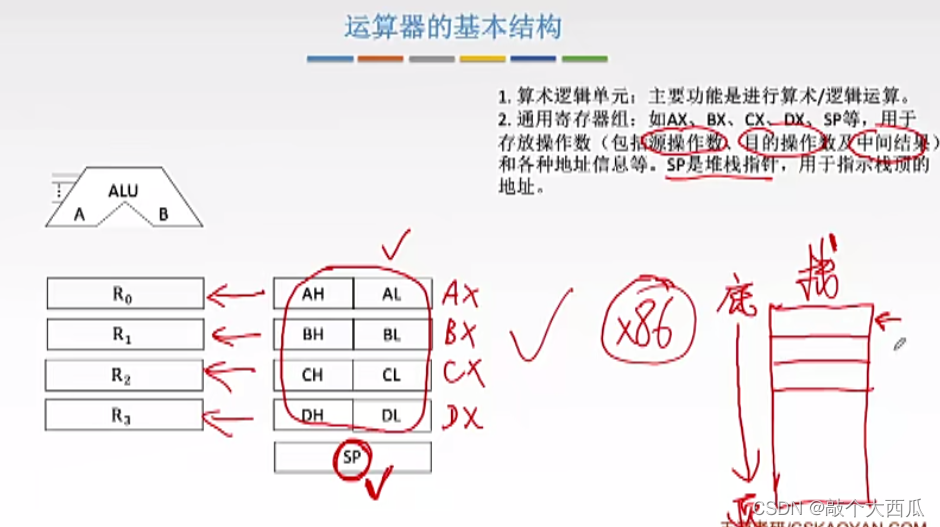

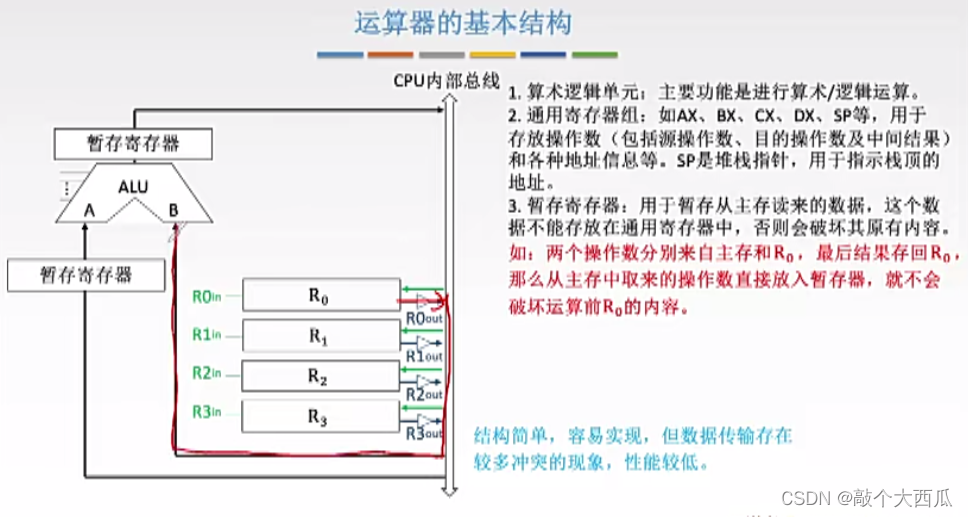

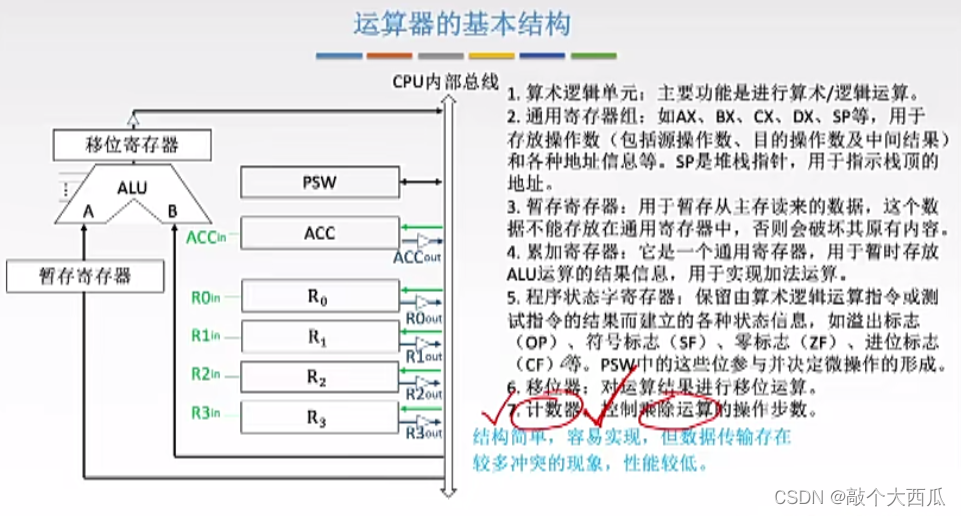

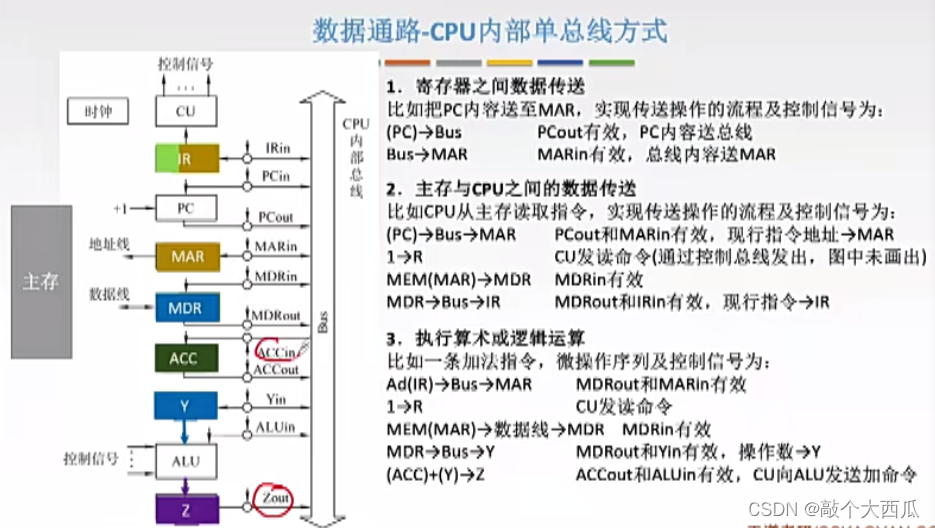

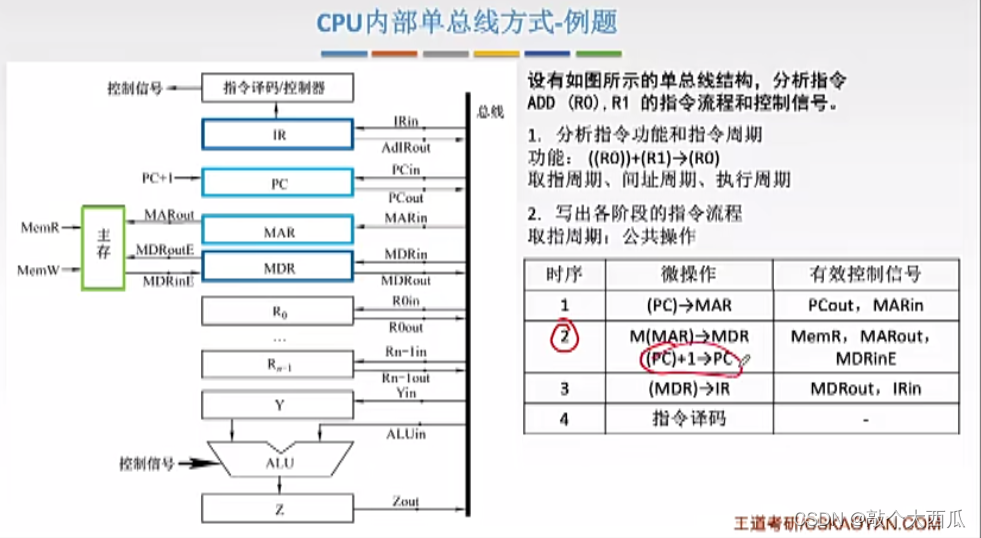

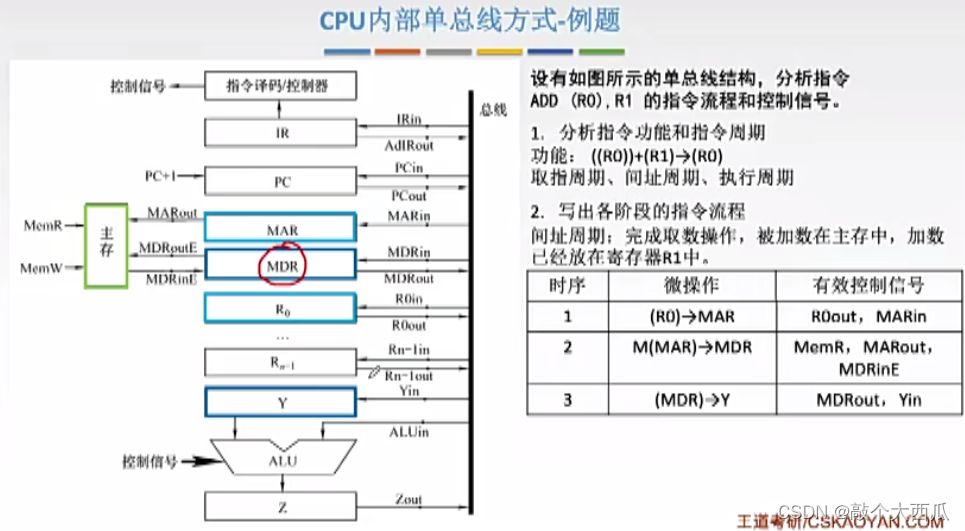

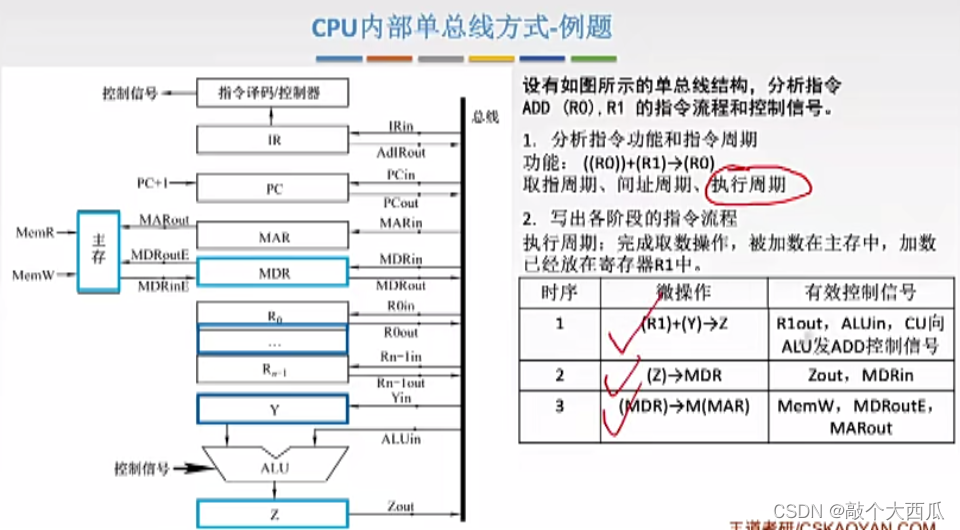

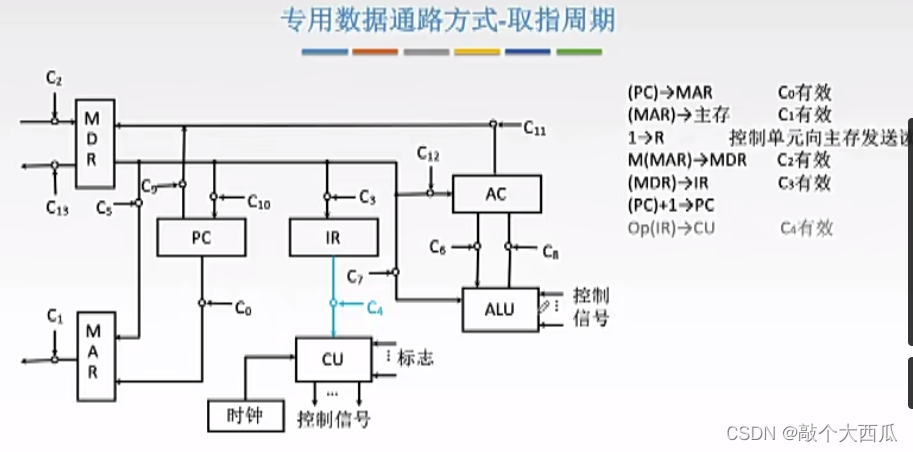

数据通路-单总线结构

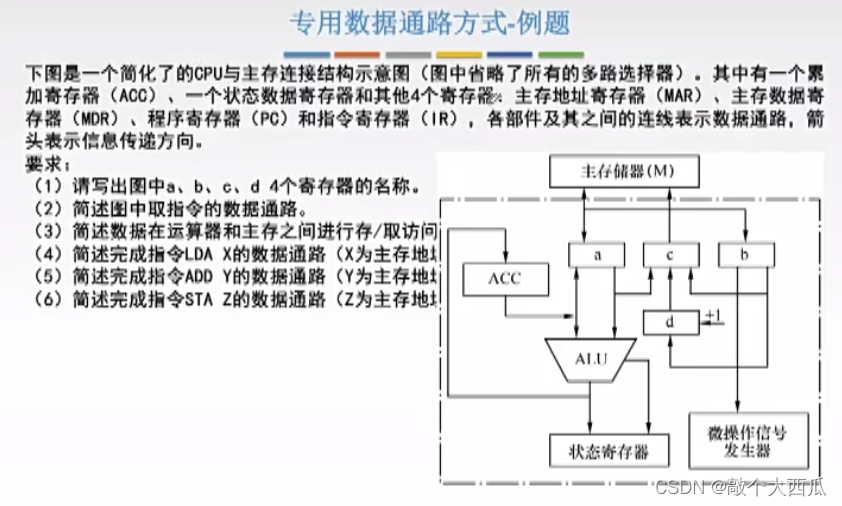

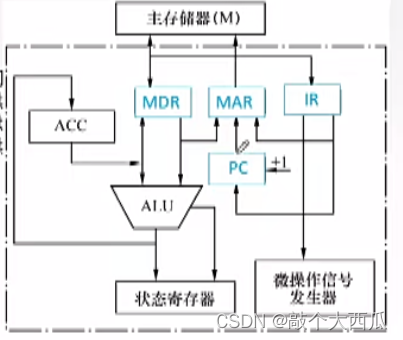

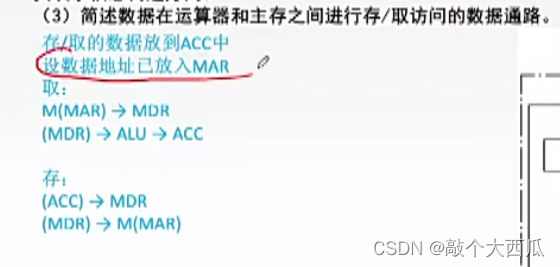

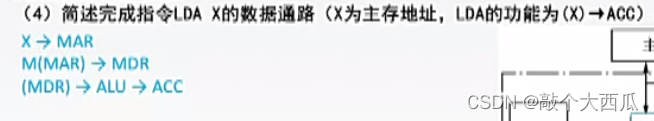

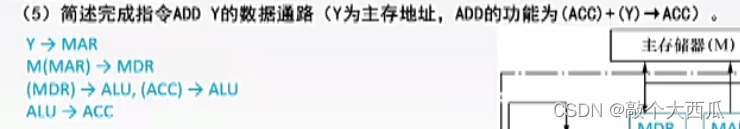

数据通路-专用数据通路

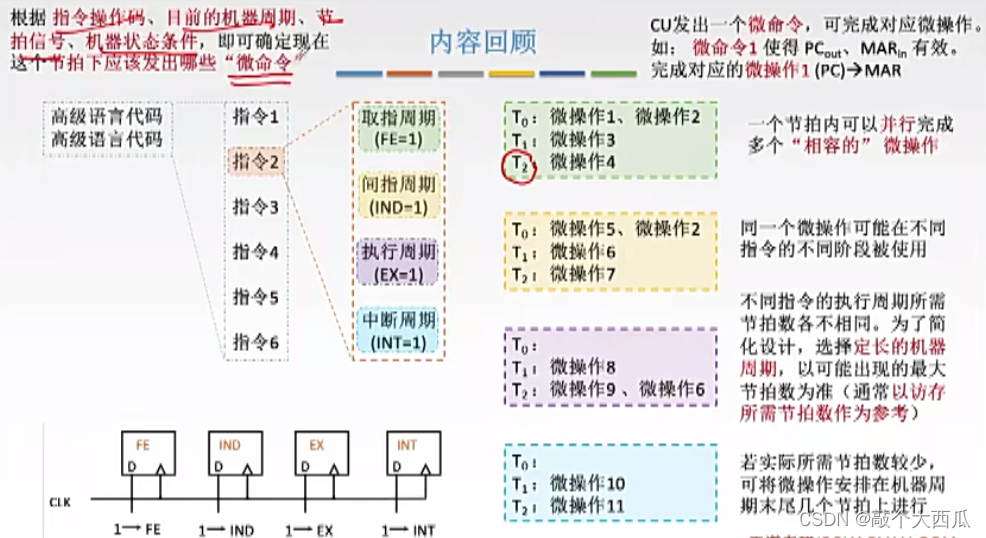

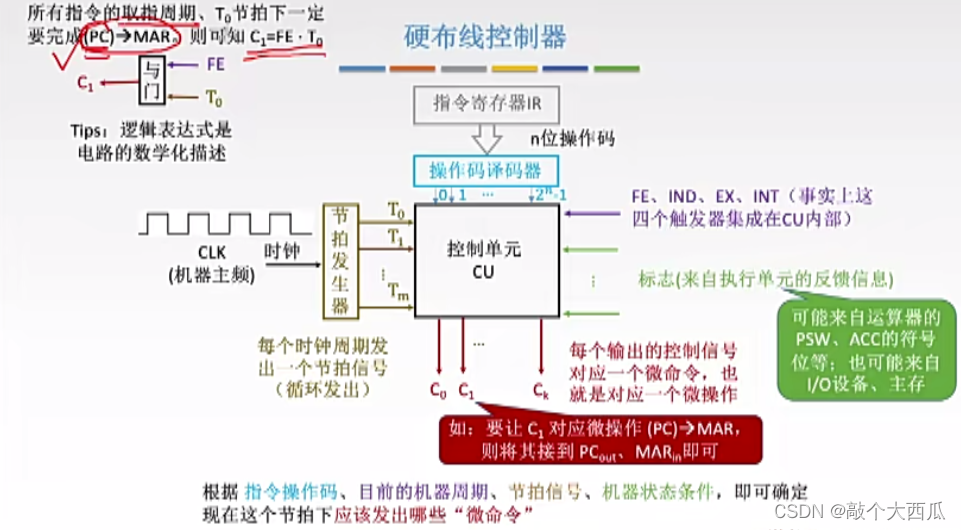

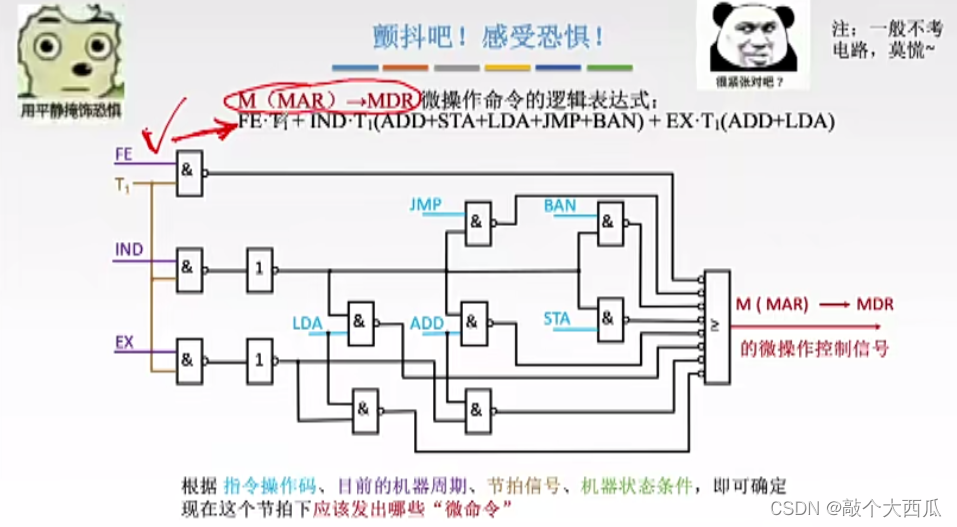

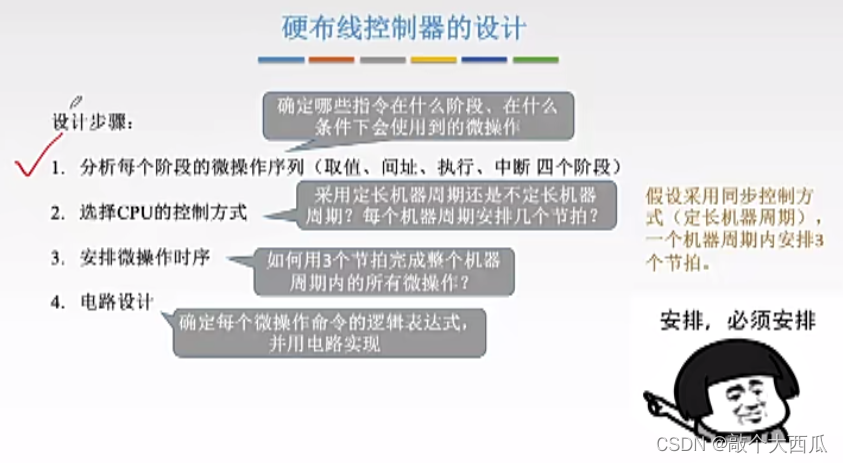

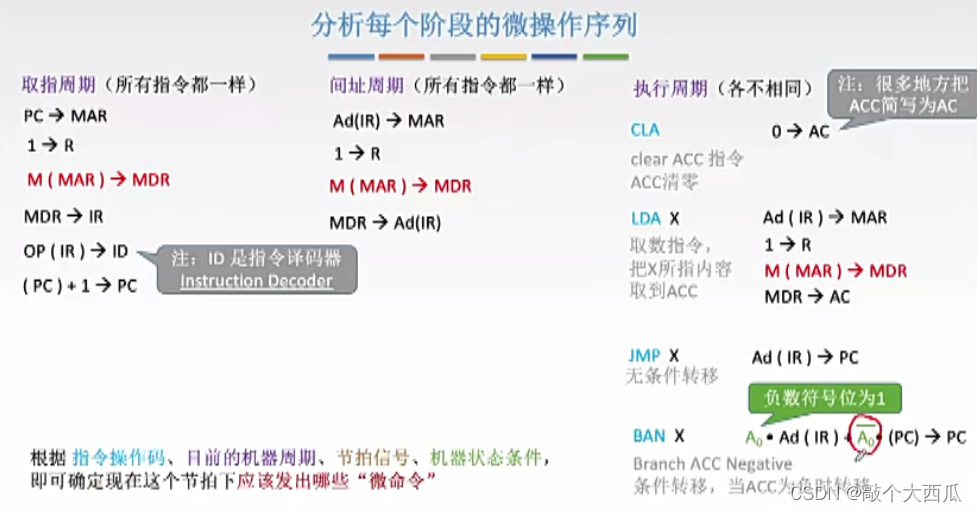

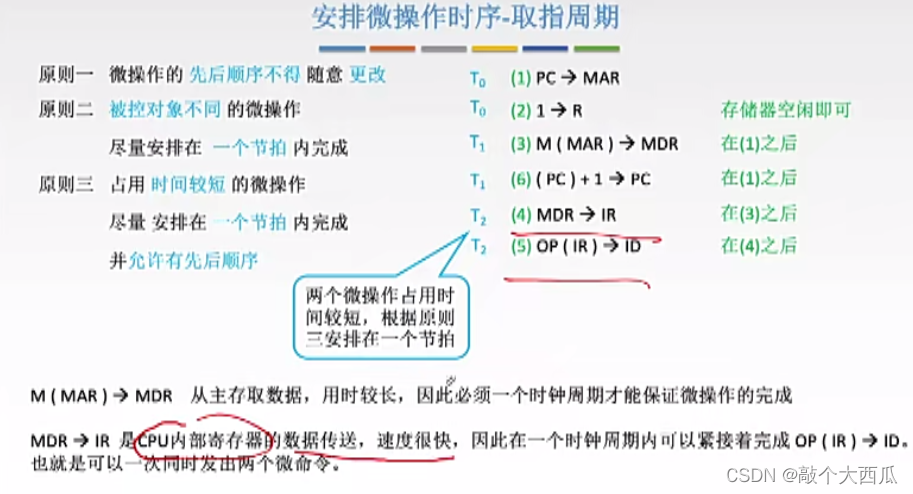

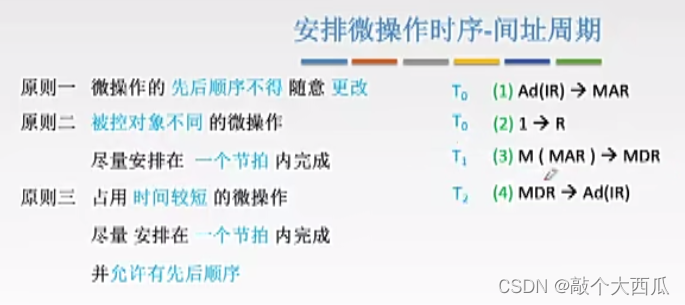

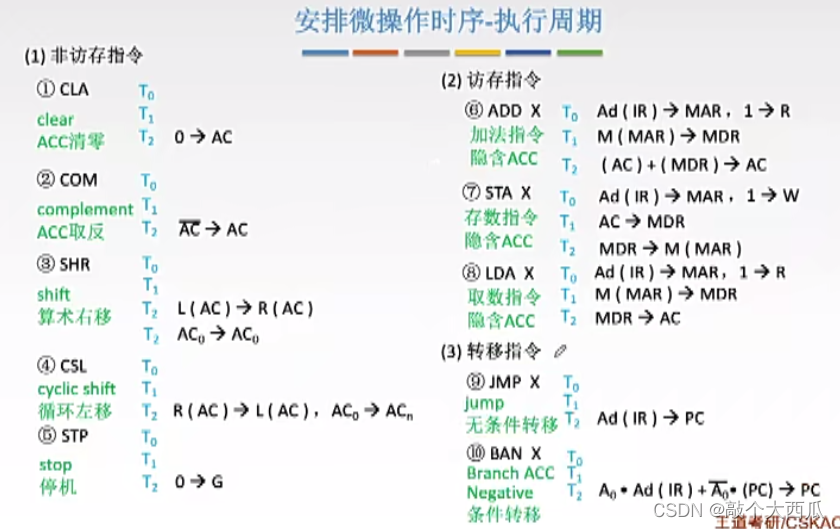

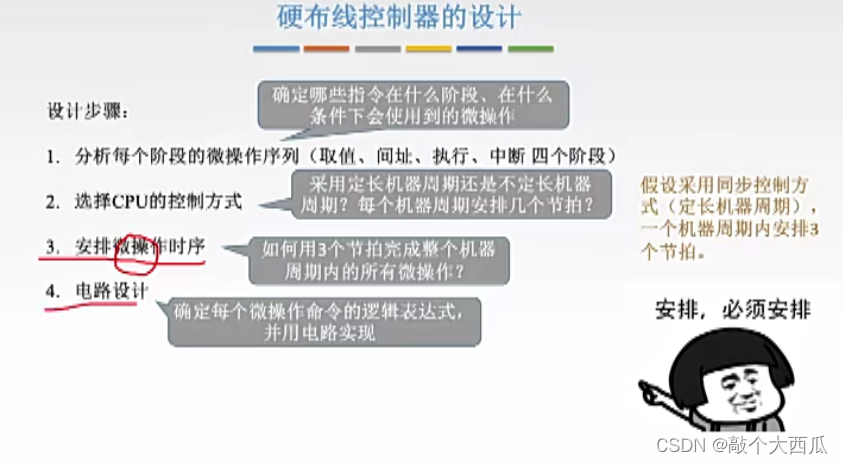

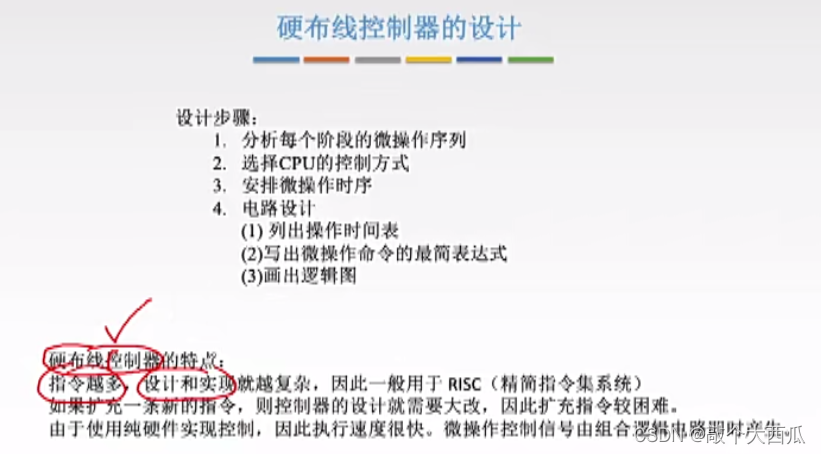

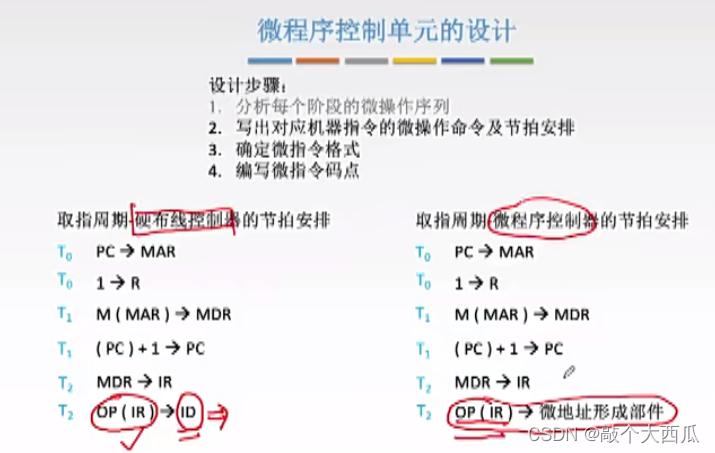

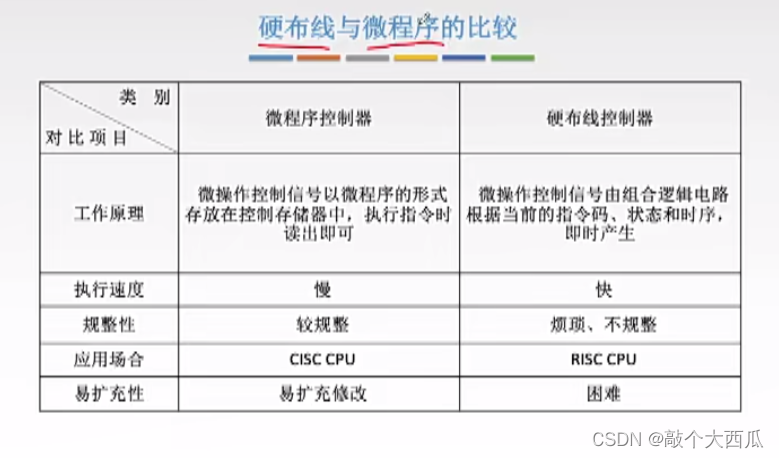

硬布线控制器设计

电路设计不会考略

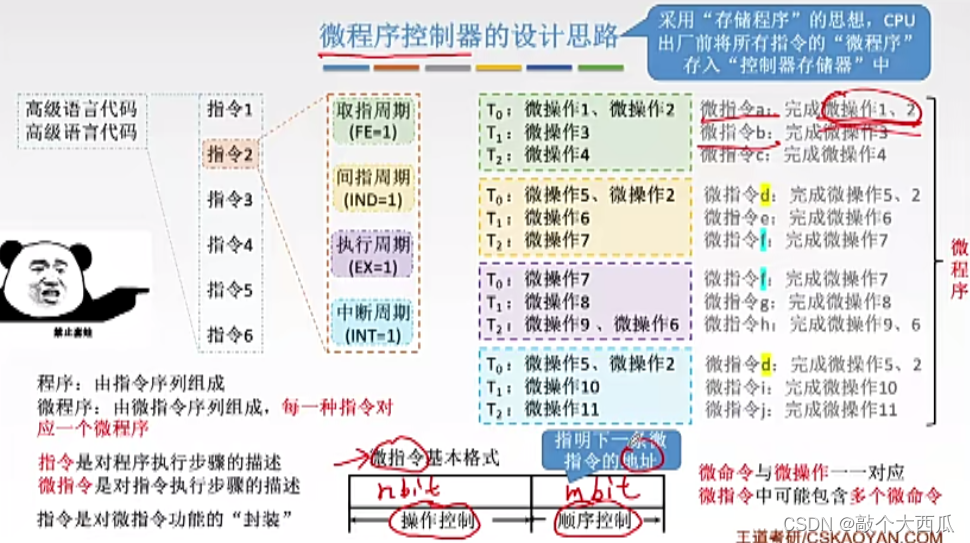

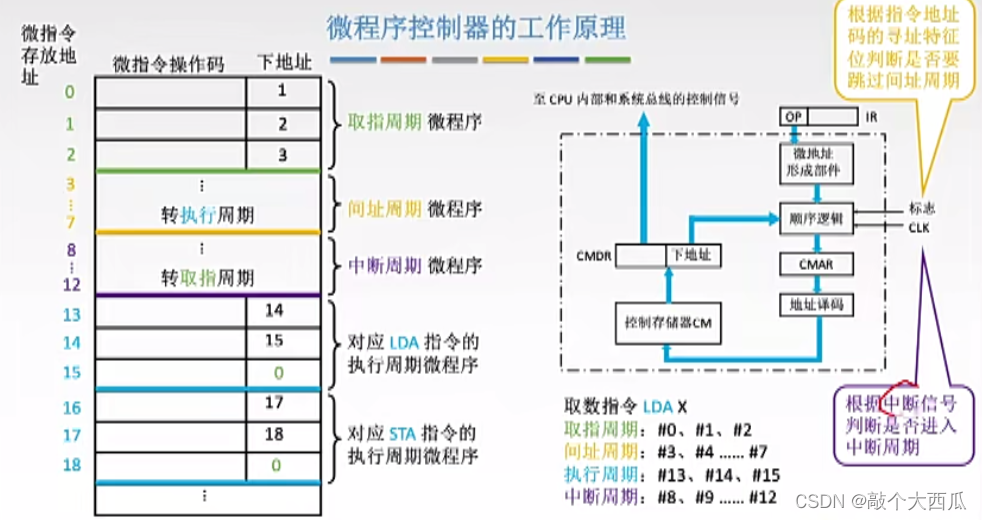

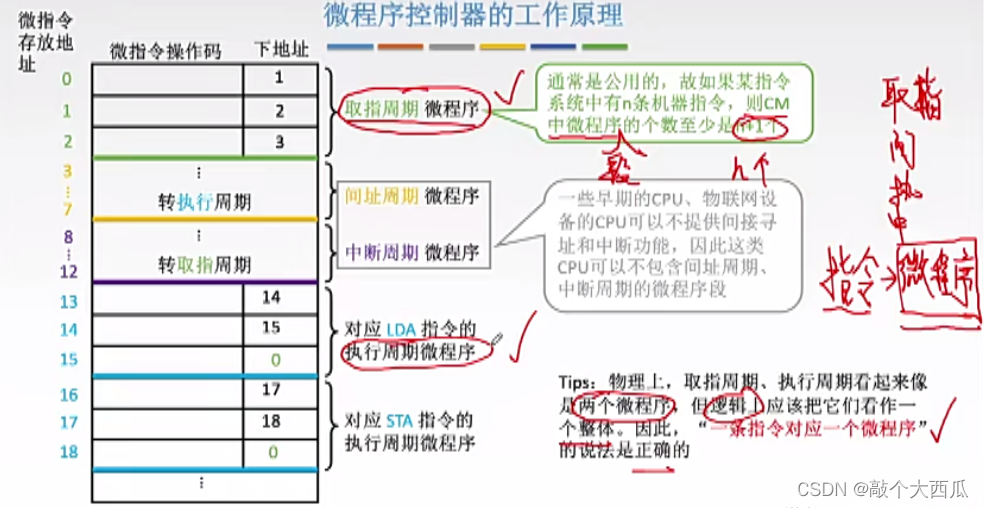

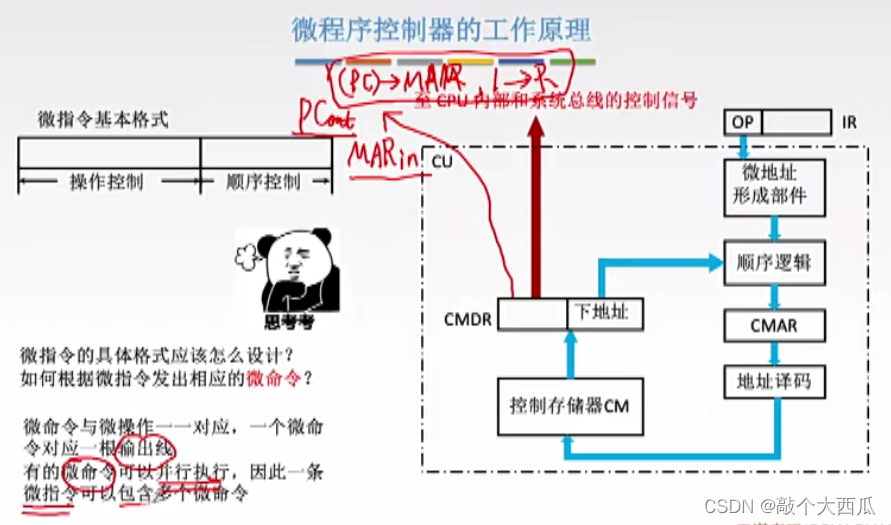

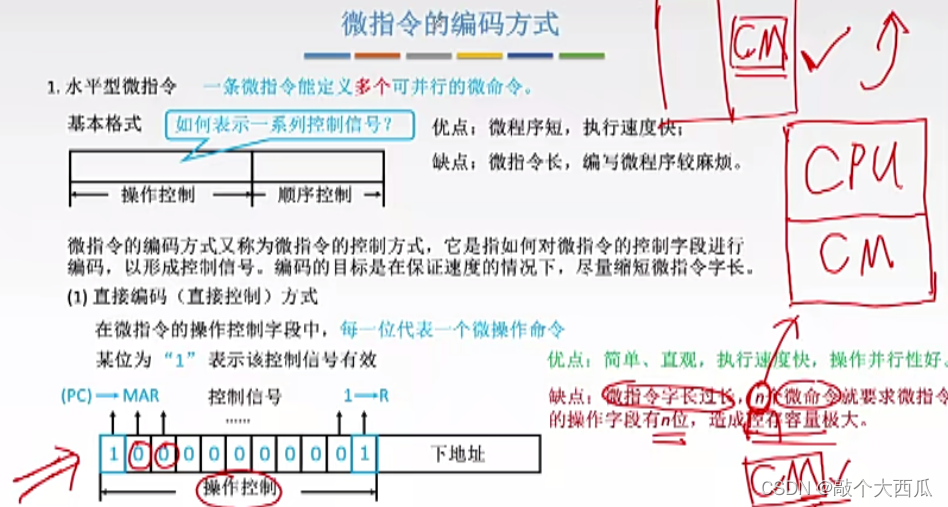

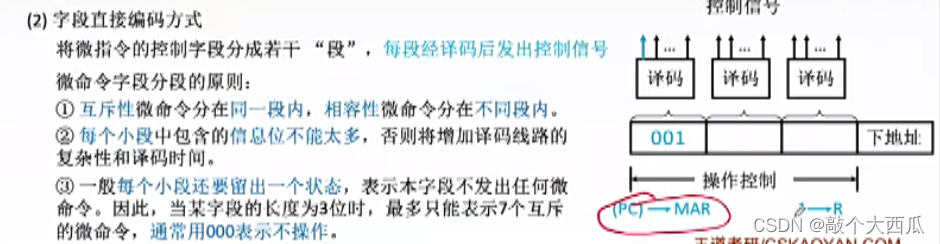

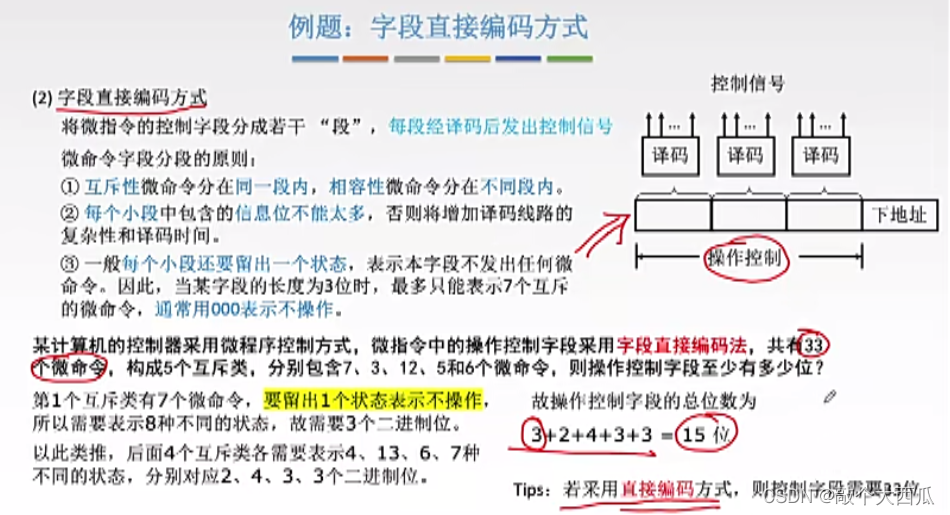

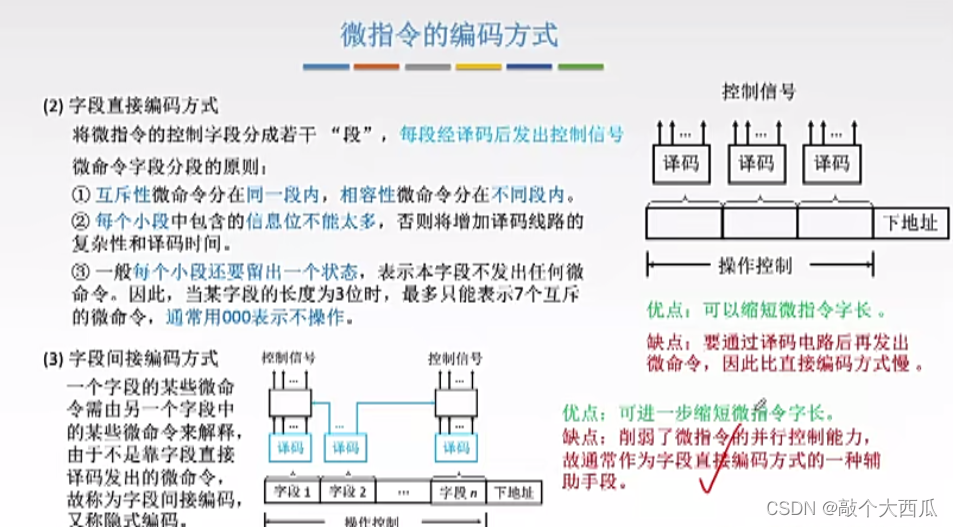

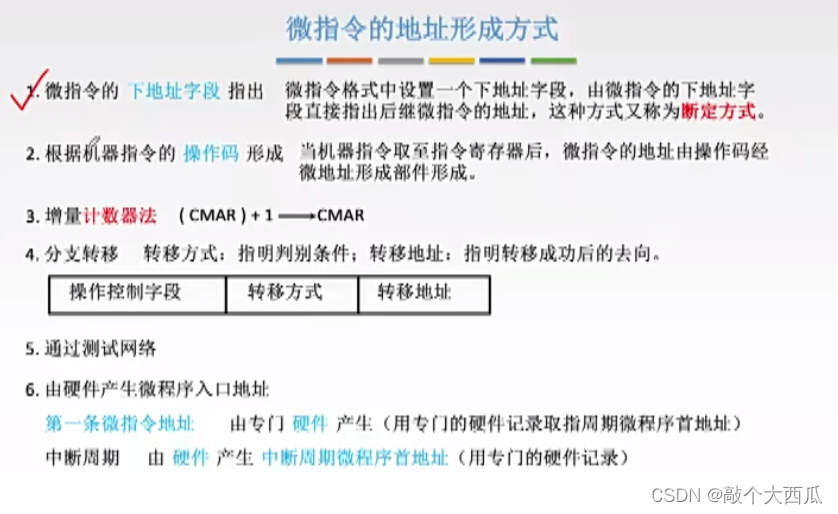

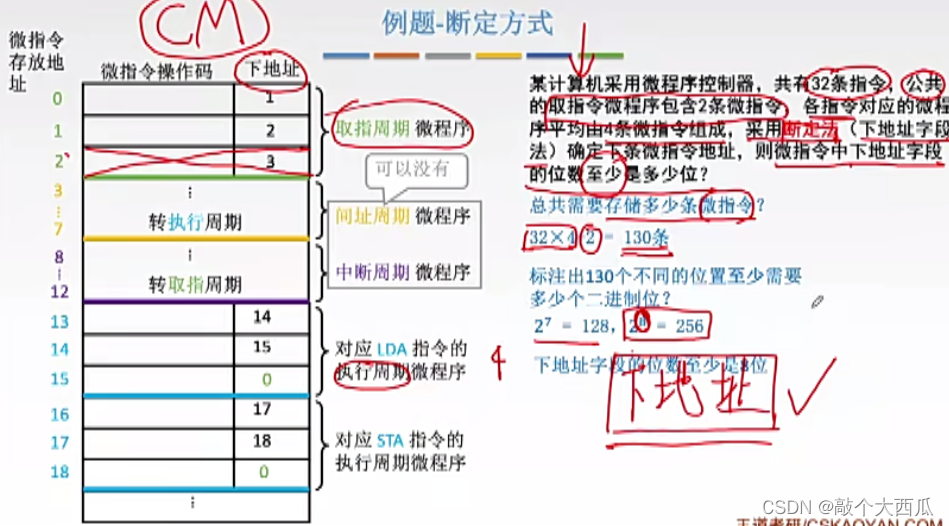

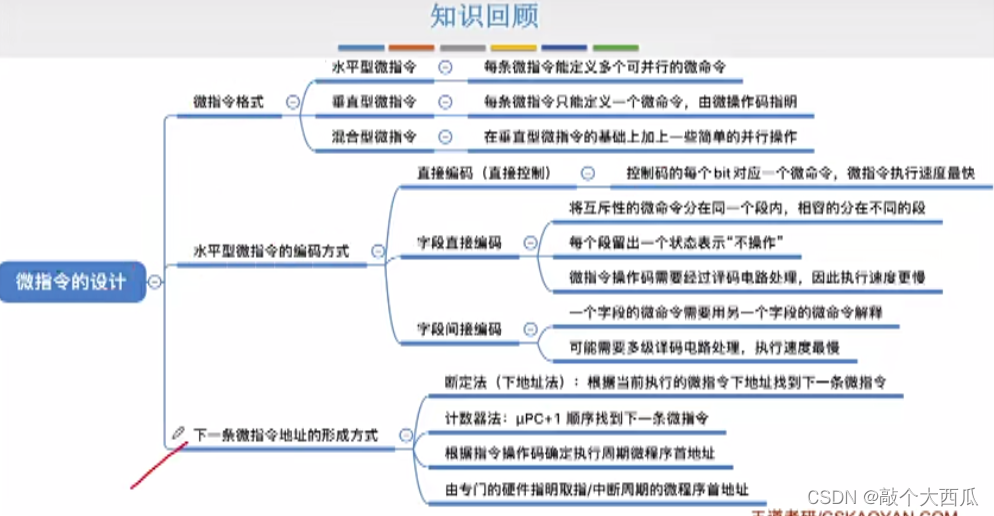

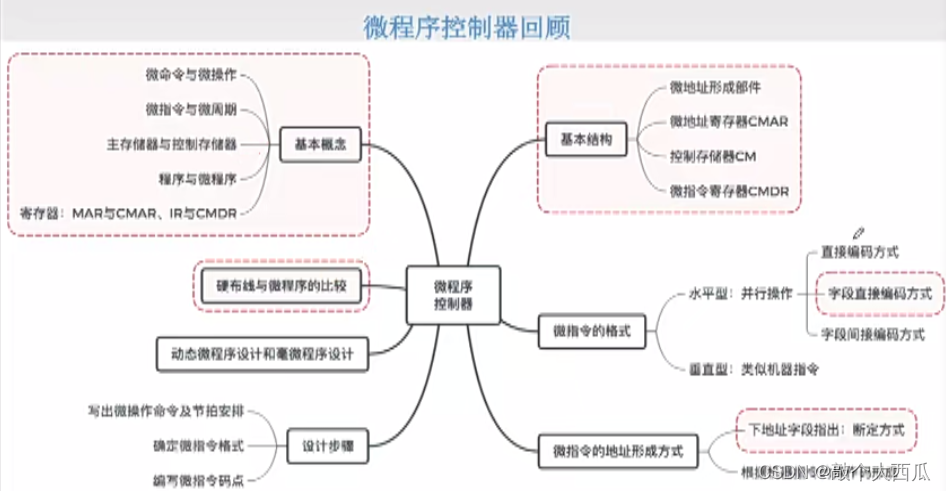

微程序控制器的基本原理

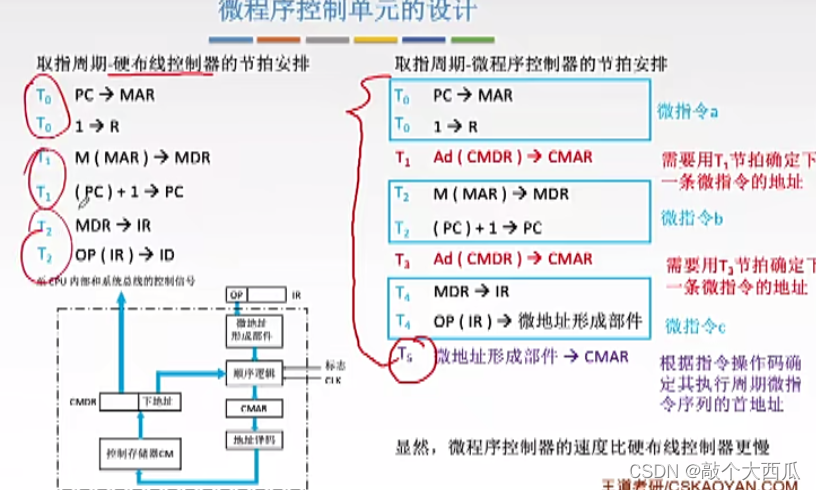

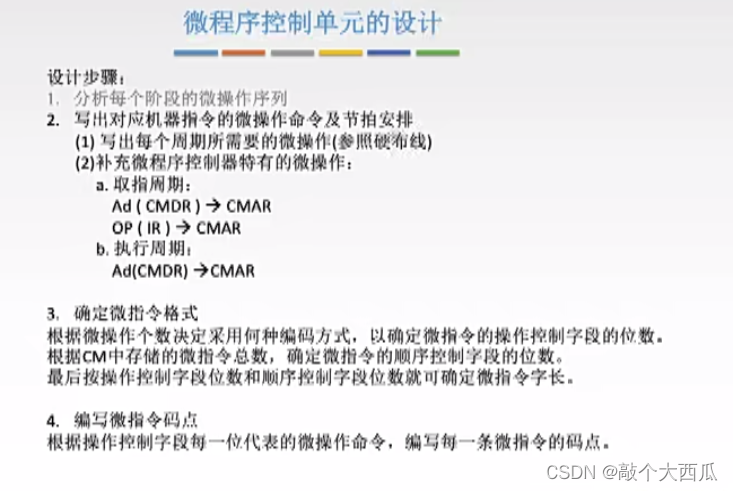

微程序控制单元设计

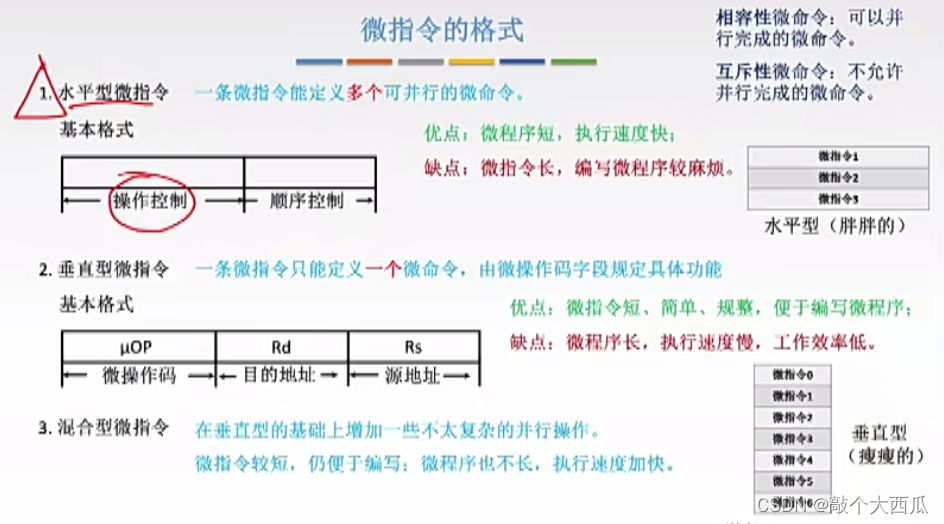

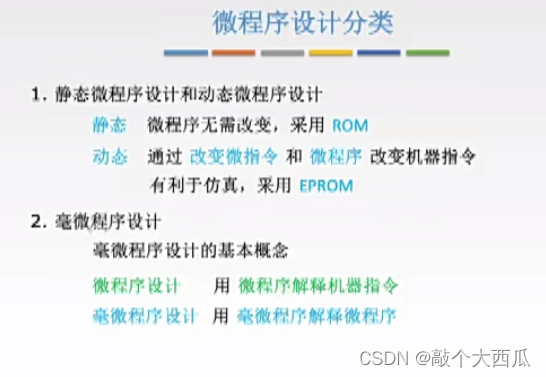

微程序设计分类

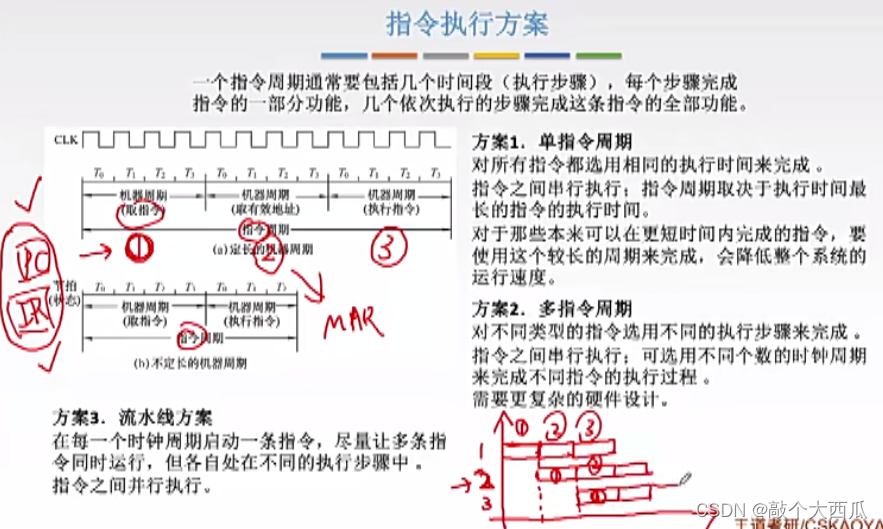

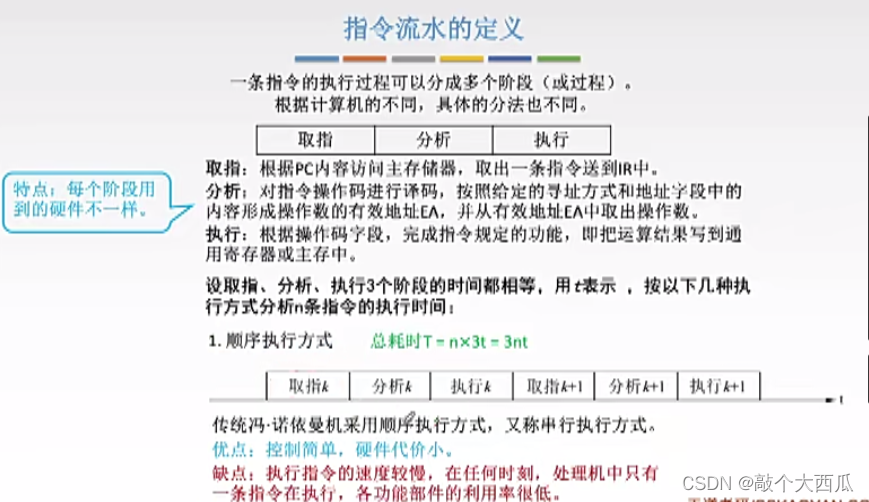

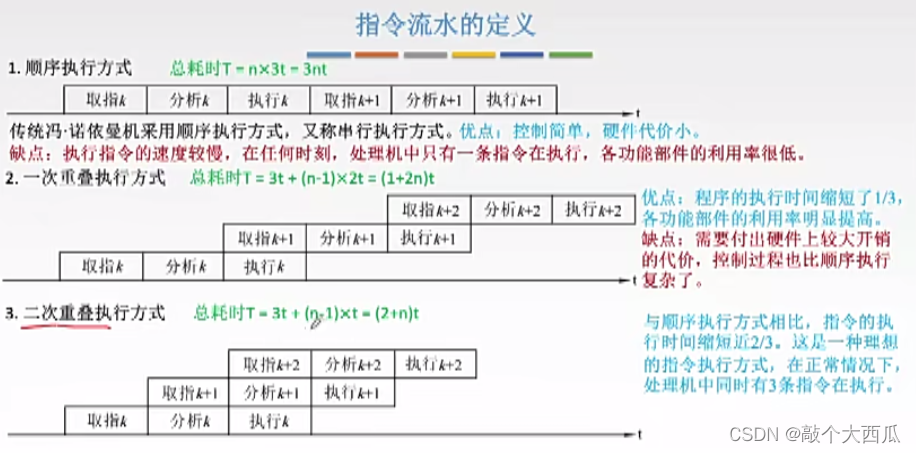

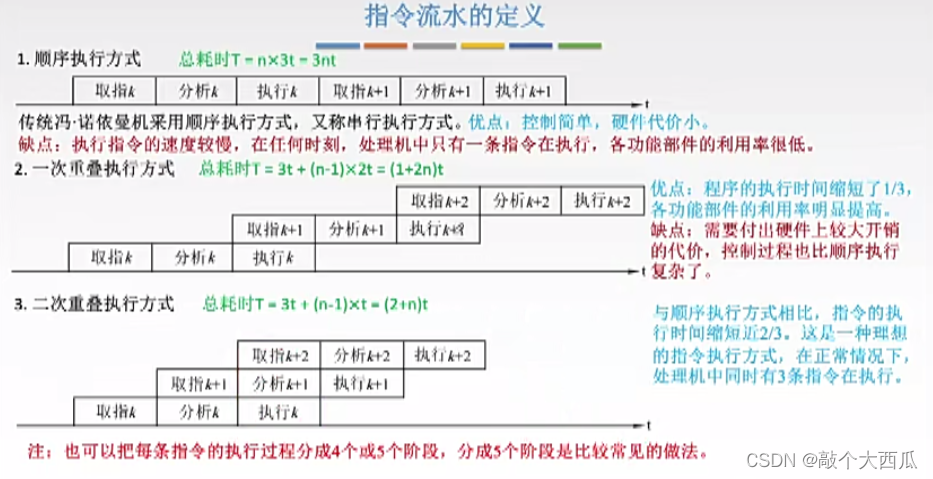

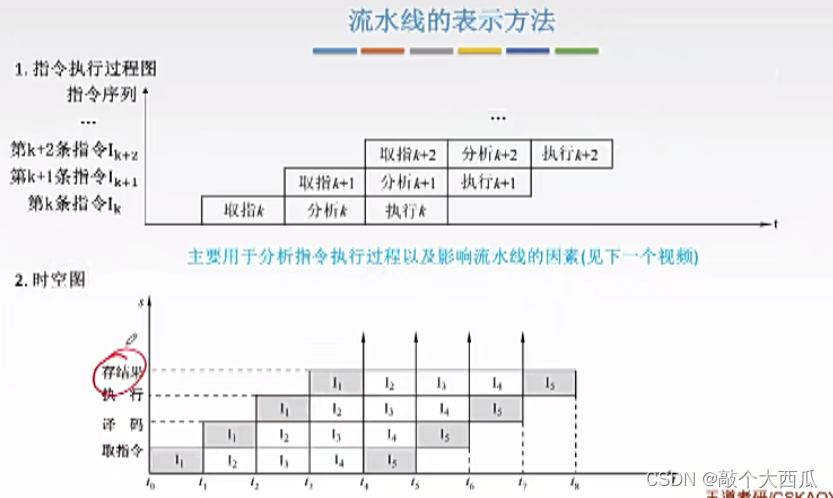

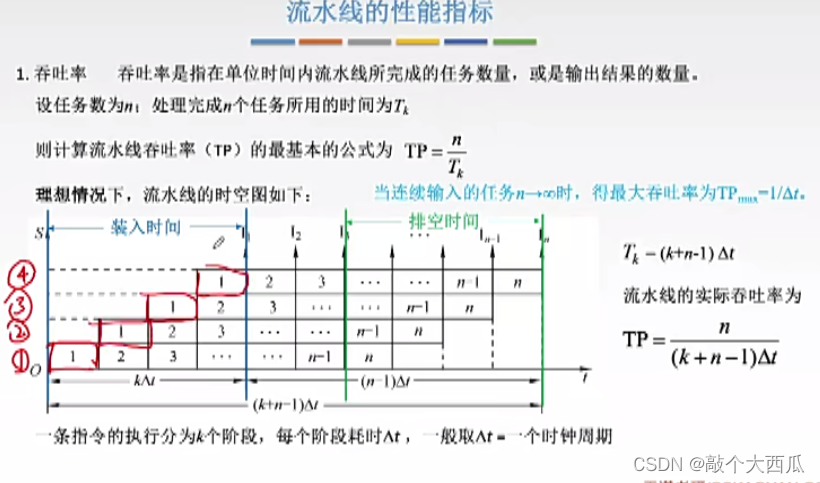

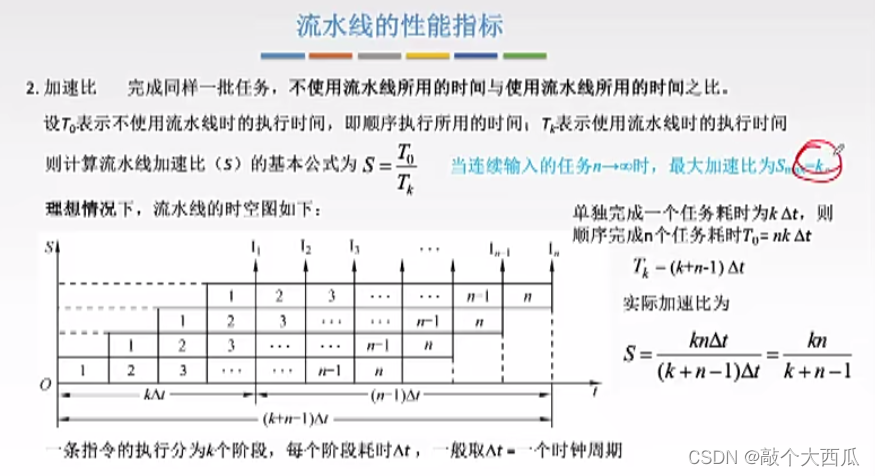

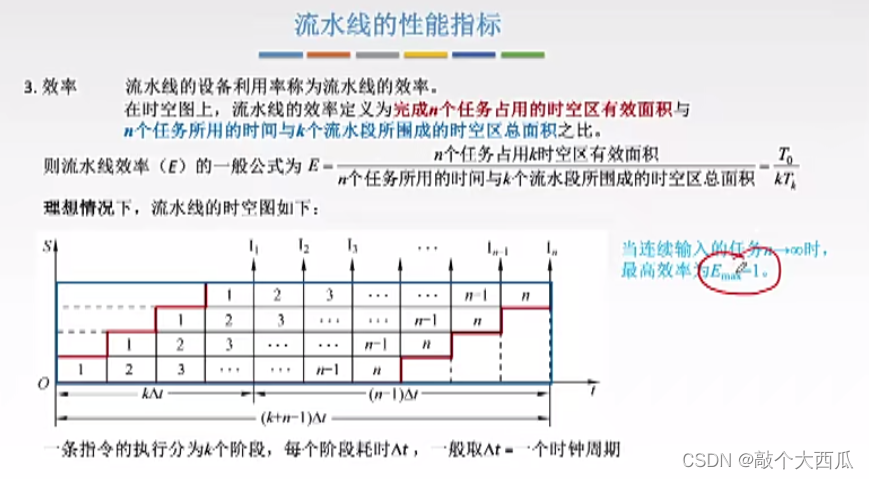

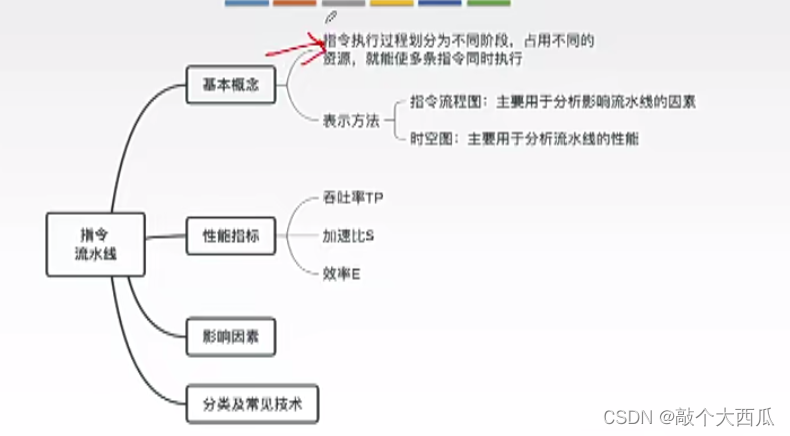

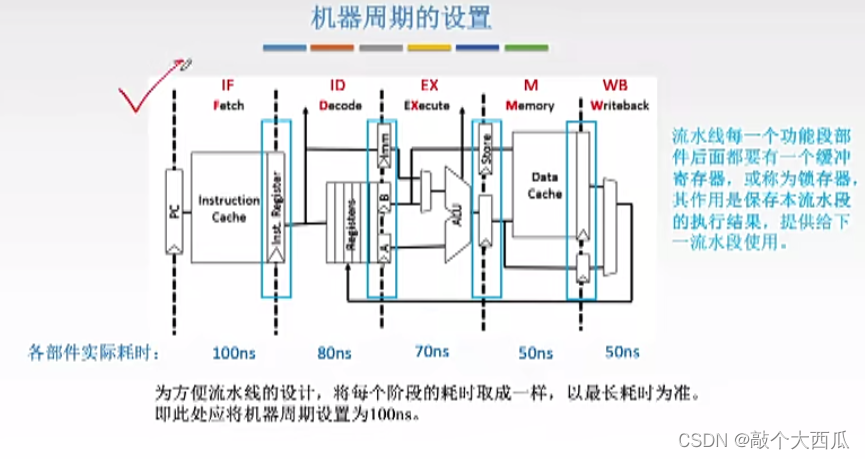

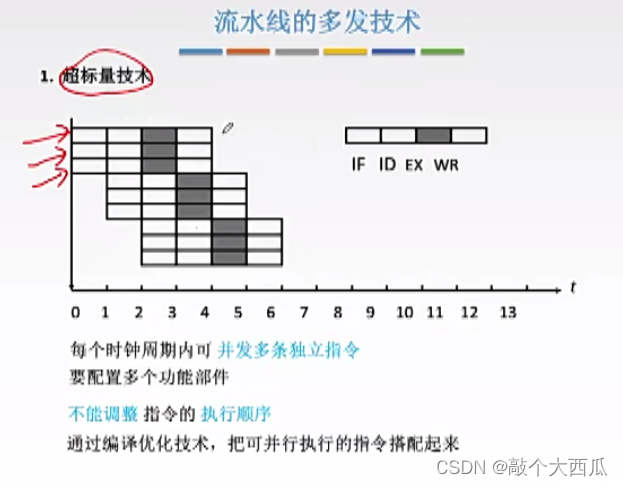

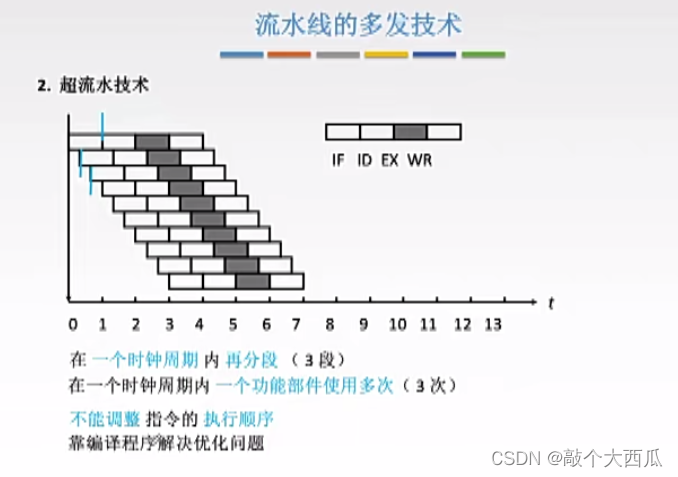

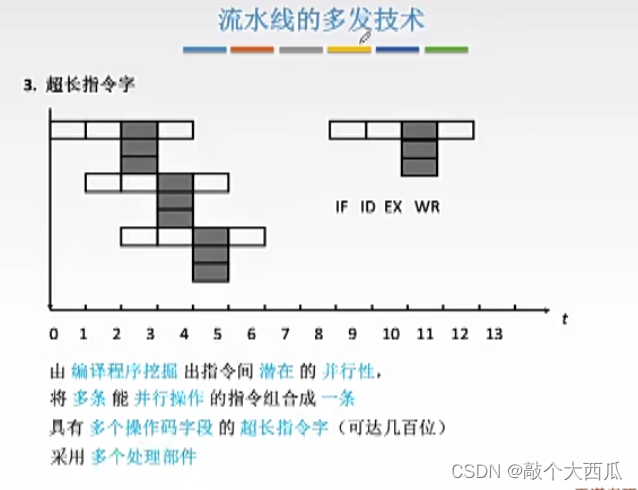

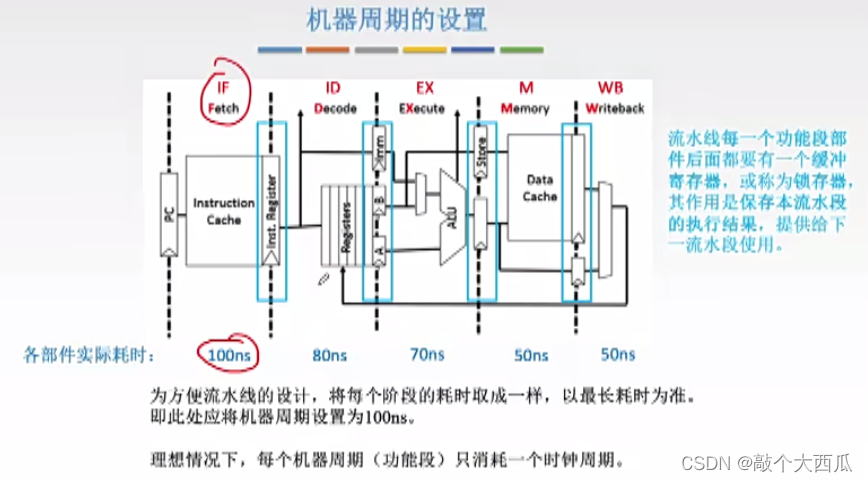

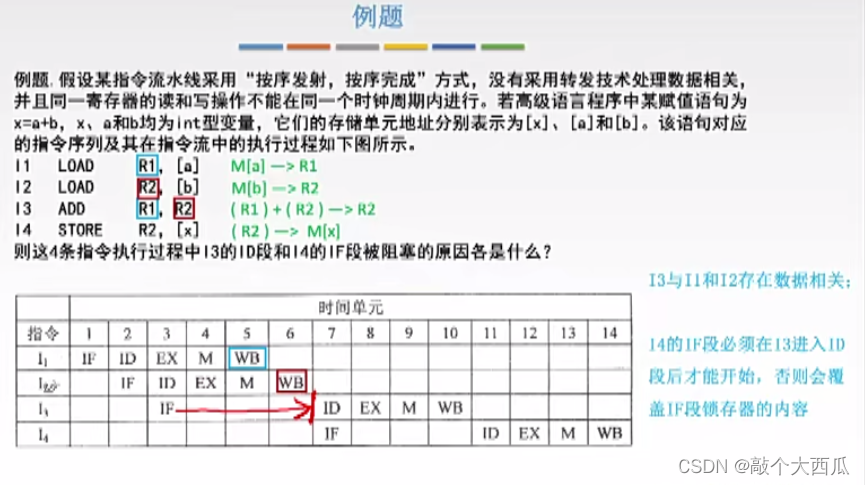

指令流水线

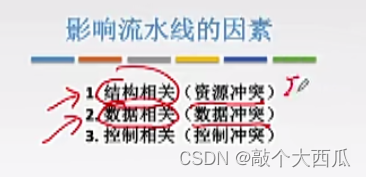

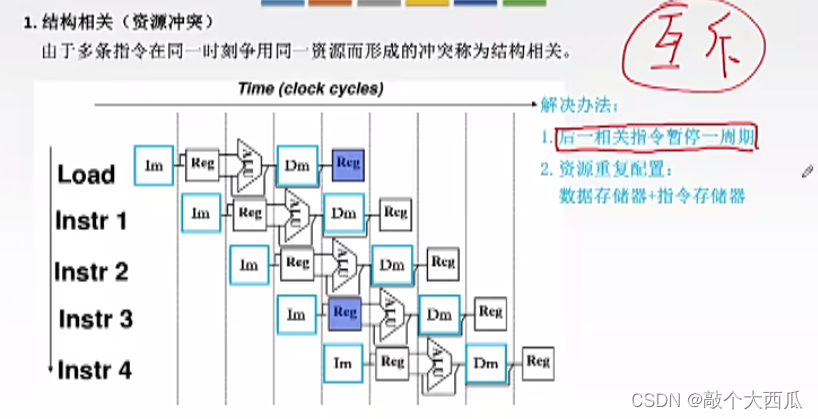

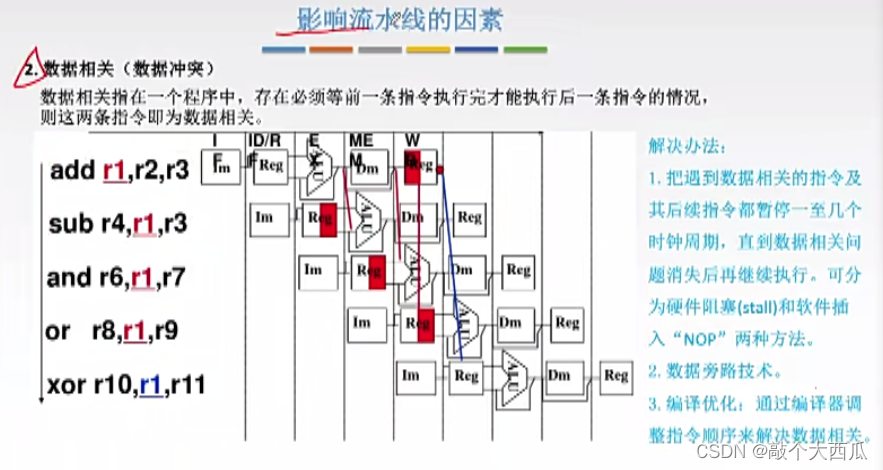

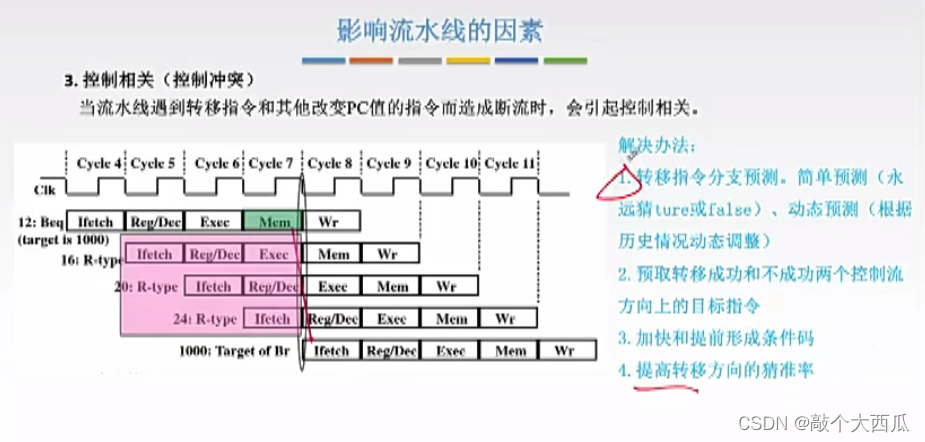

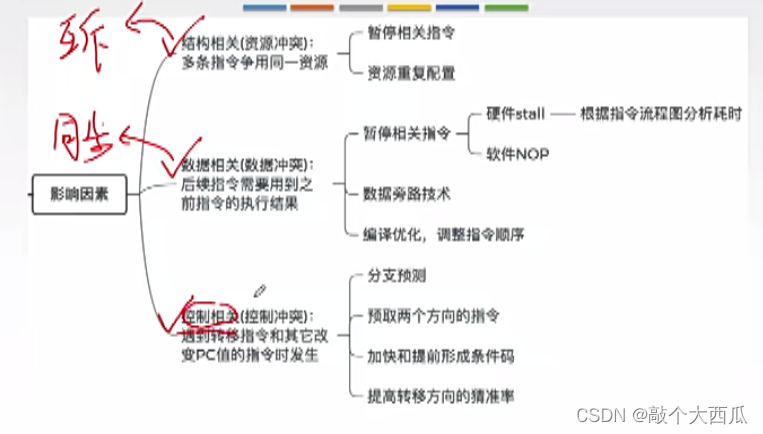

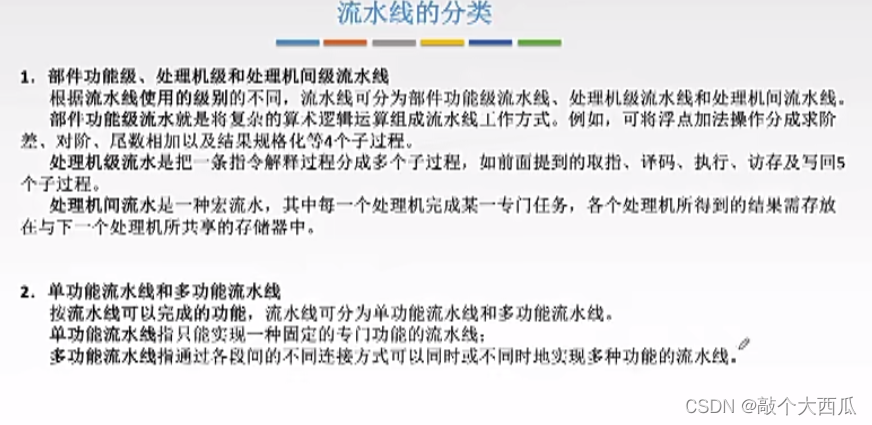

指令流水线的影响因素和分类

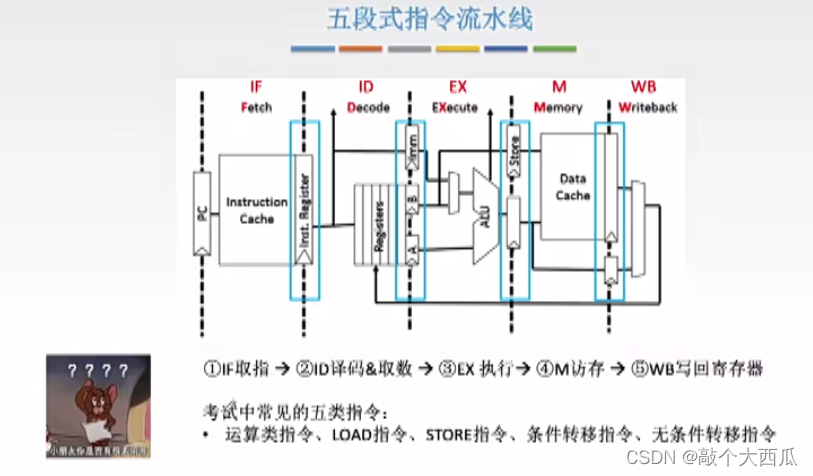

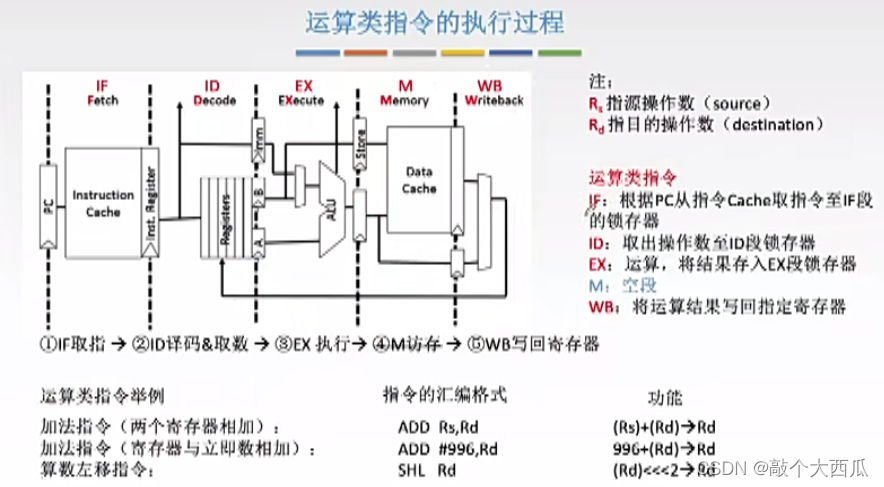

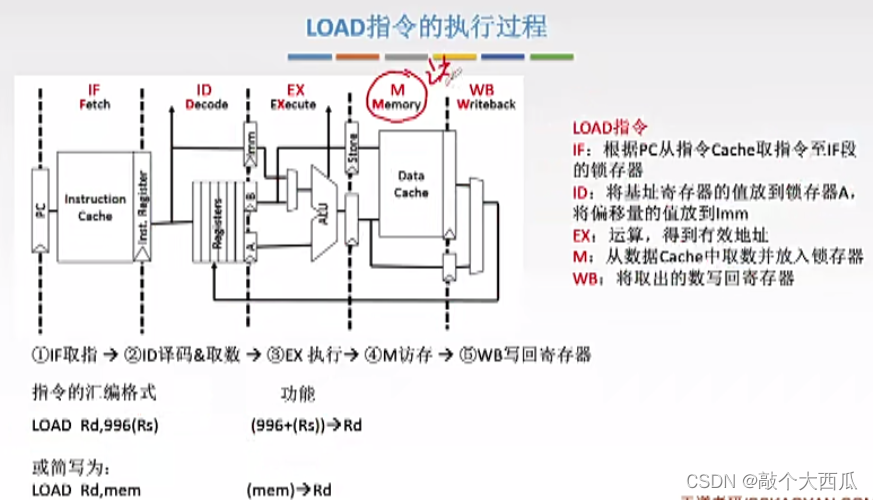

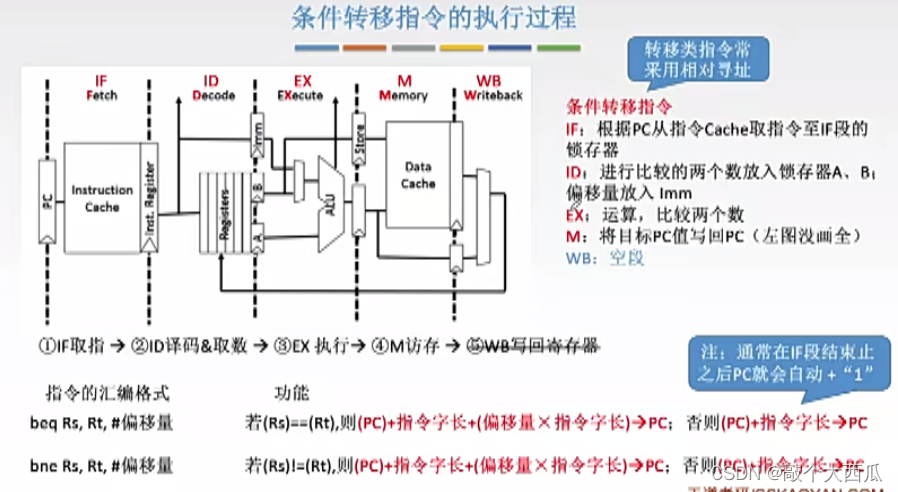

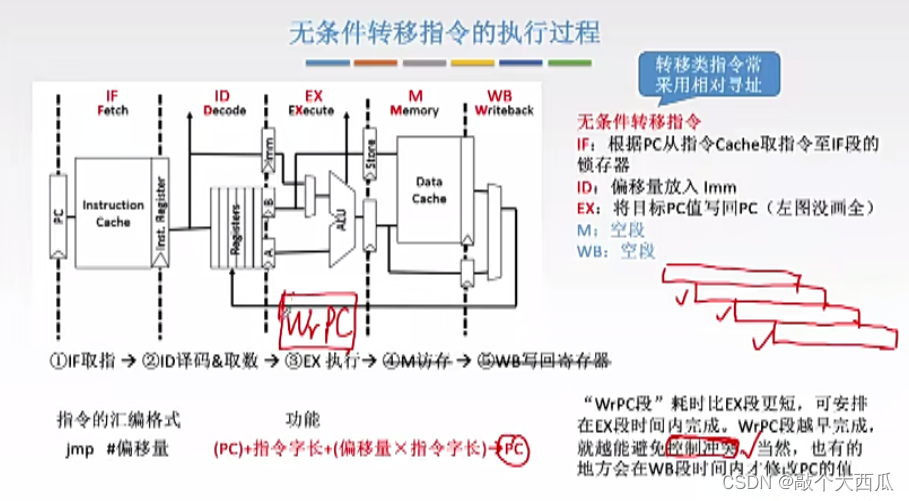

五段MIPS架构是考研常考的内容

在该题中数据旁路技术的使用就是使用额外的部件r2加r3的结果直接输出打sub的r1输入端,以解决add指令和sub指令数据相关的问题

五段式指令流水线

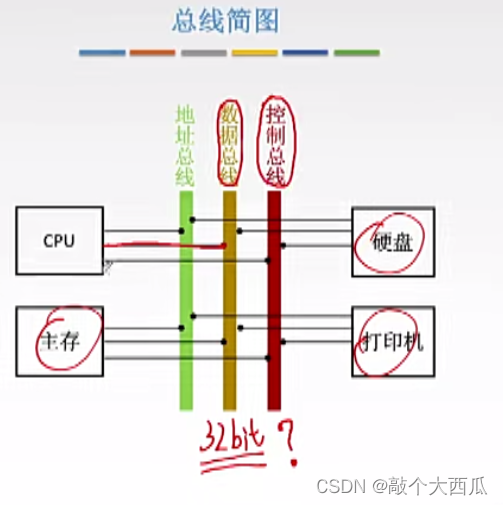

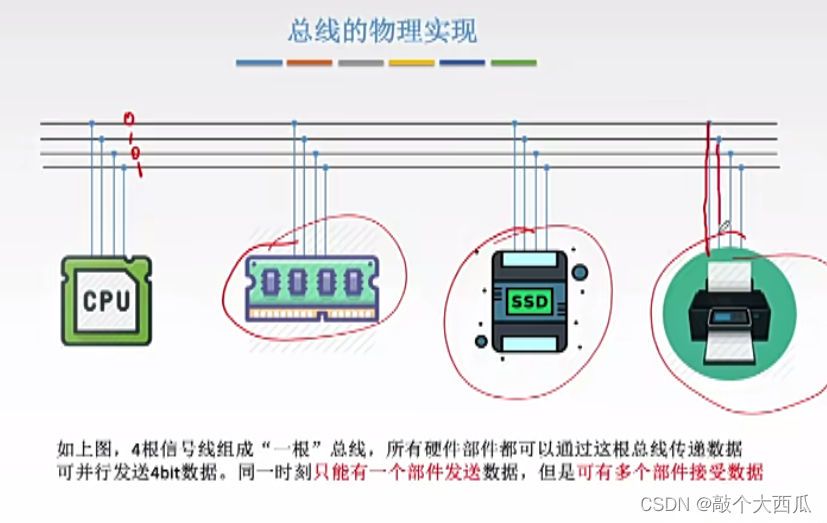

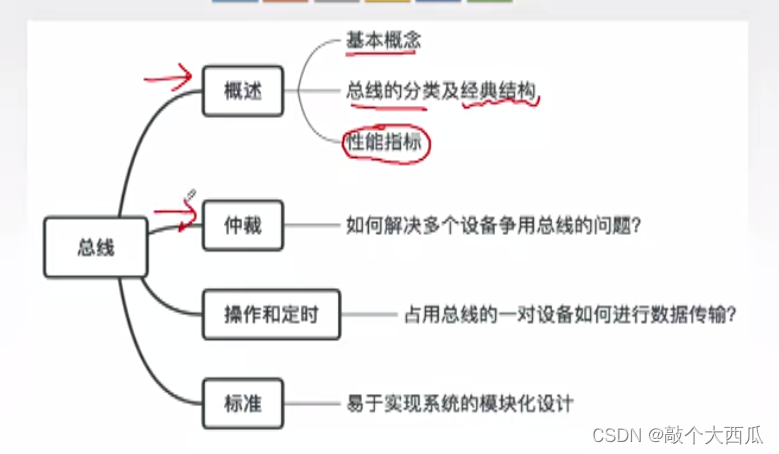

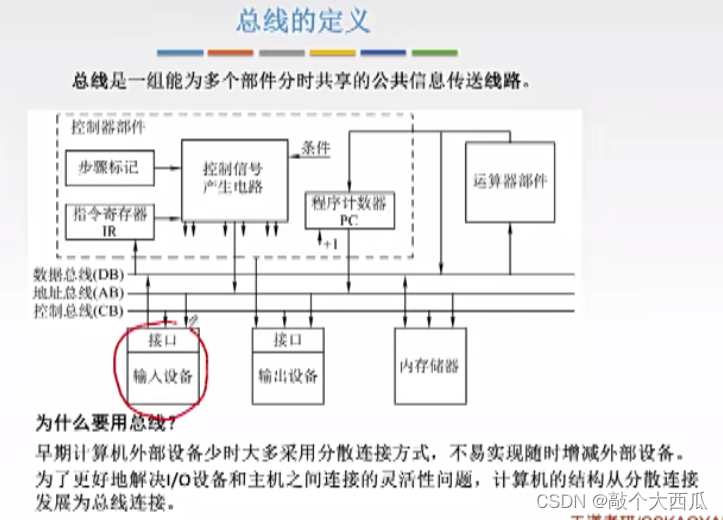

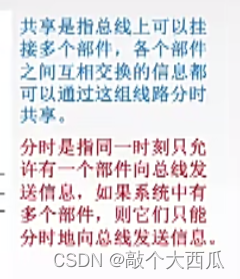

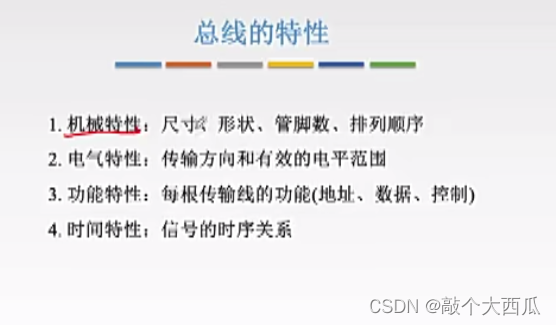

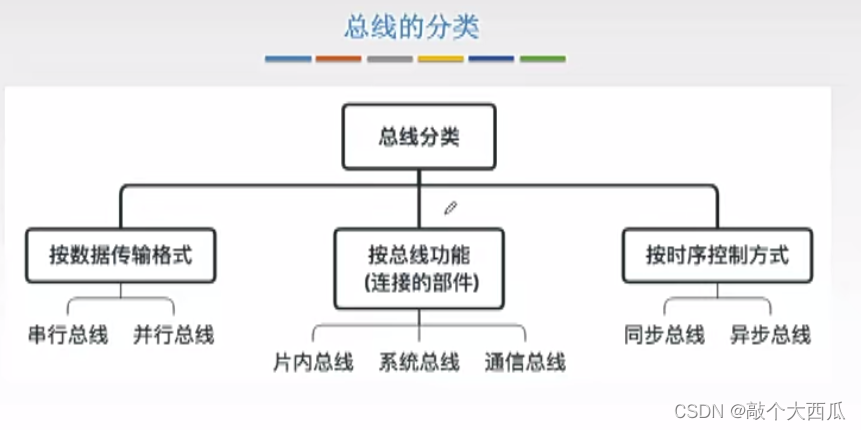

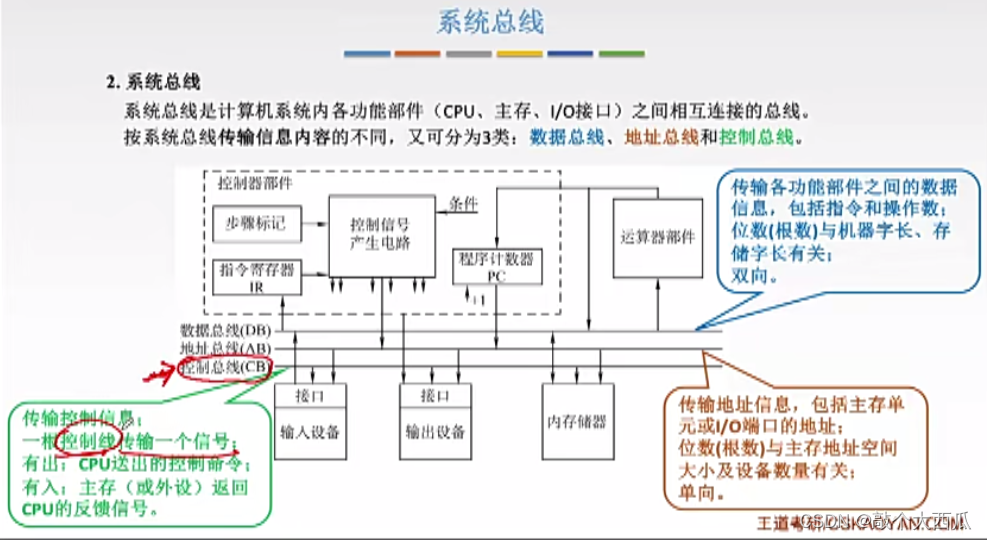

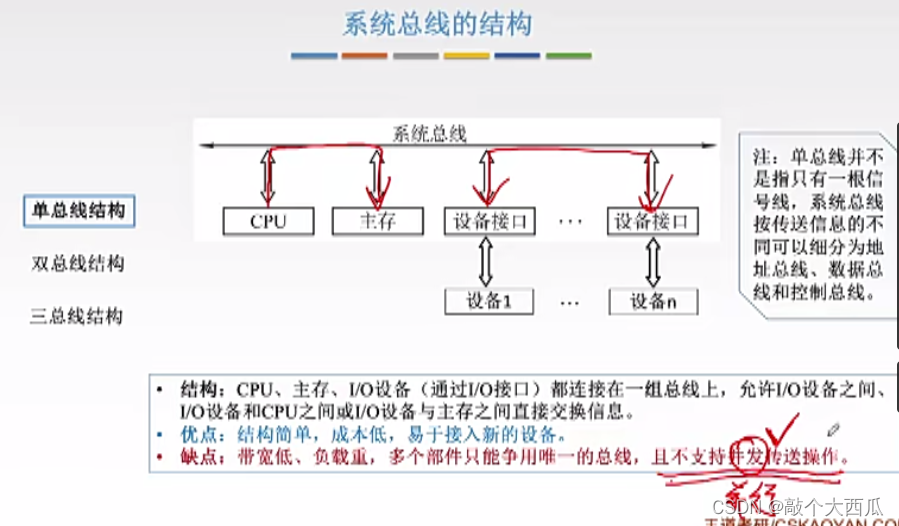

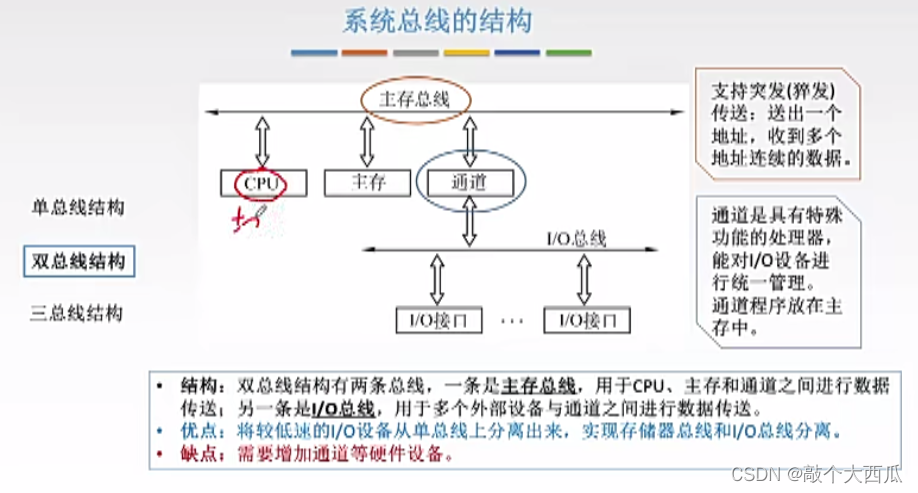

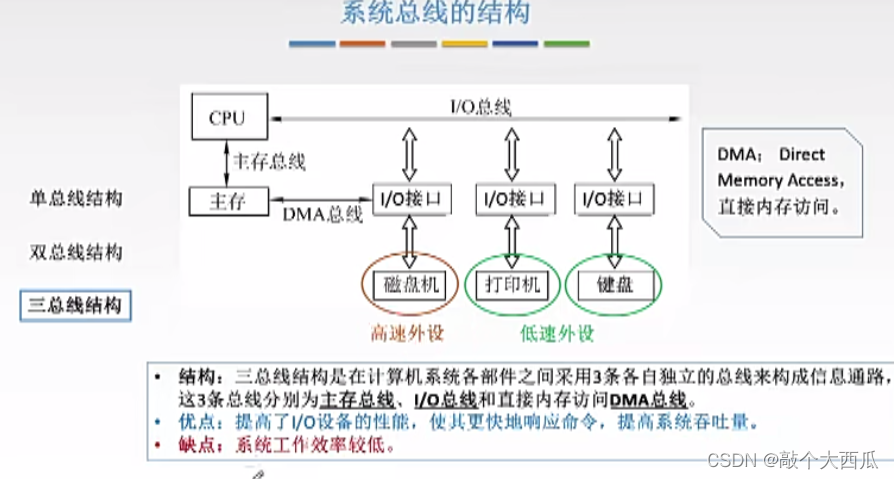

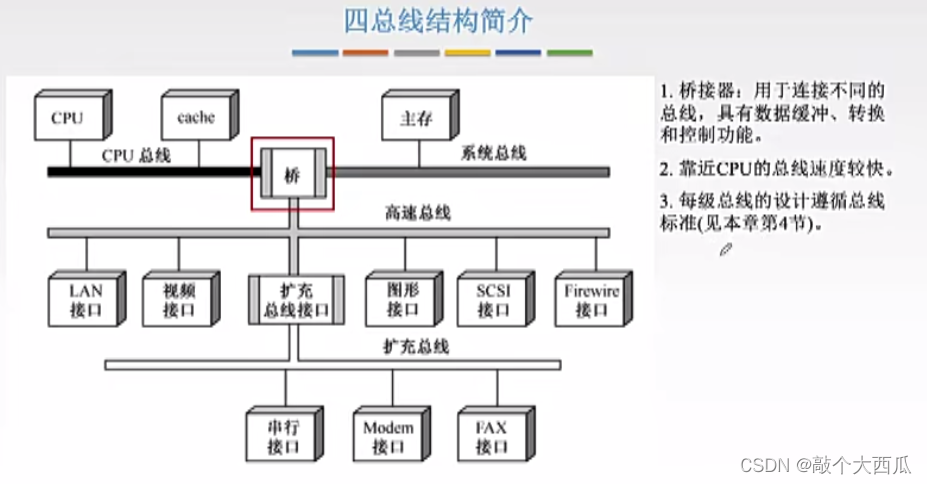

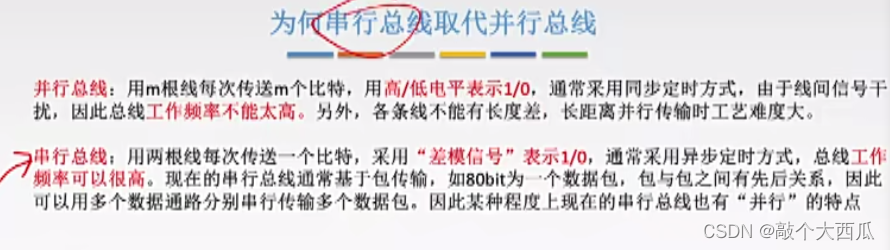

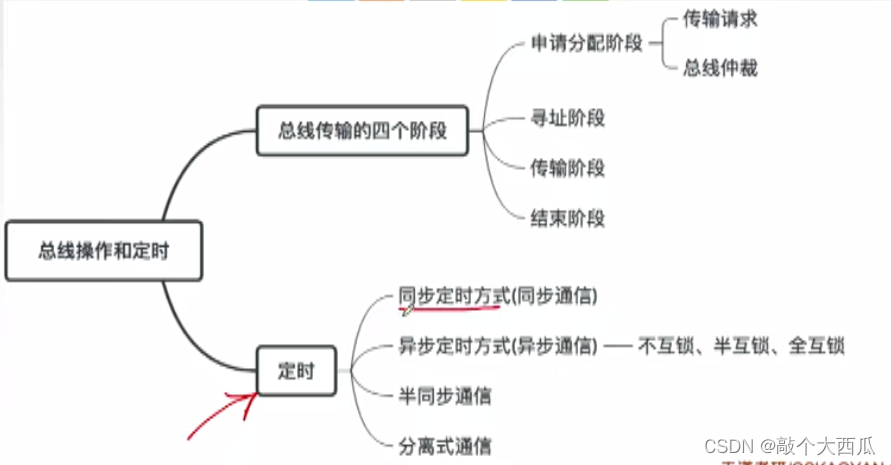

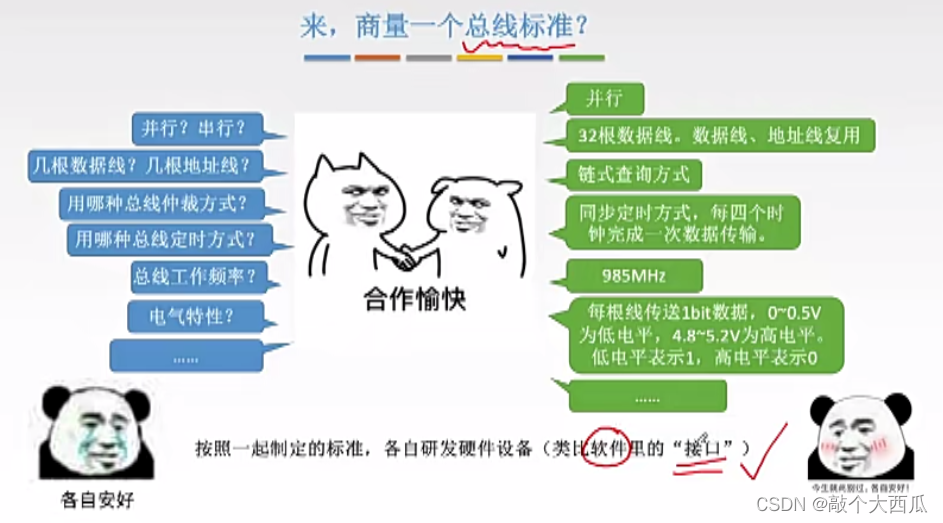

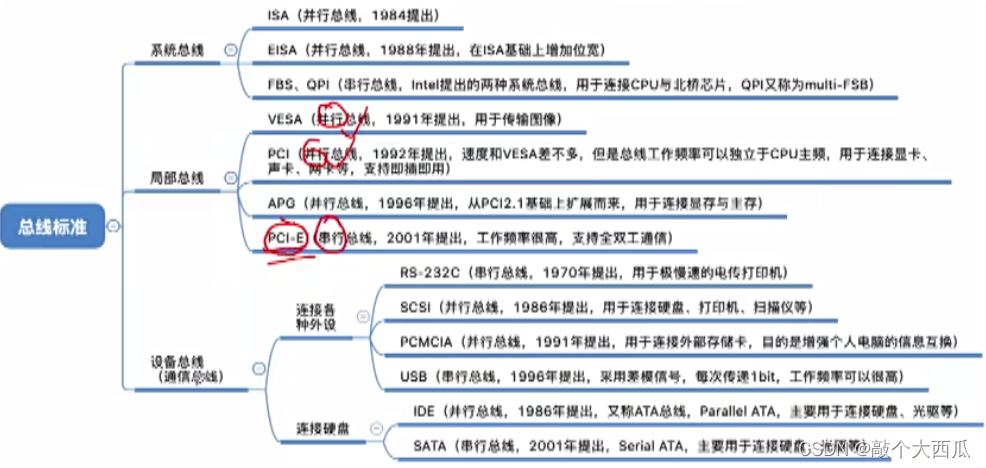

第六章 总线

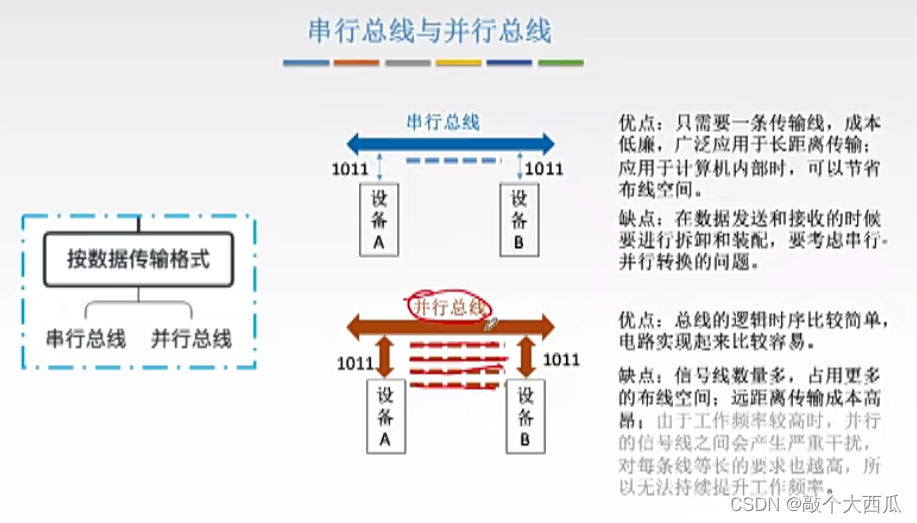

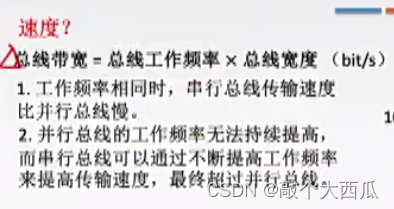

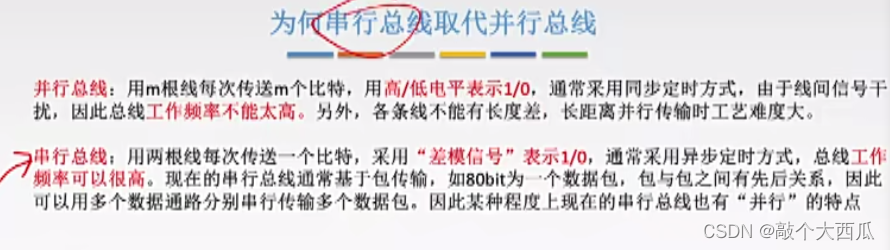

如果说并行总线的传输速率一定比串行总线高,这种说法是错误的

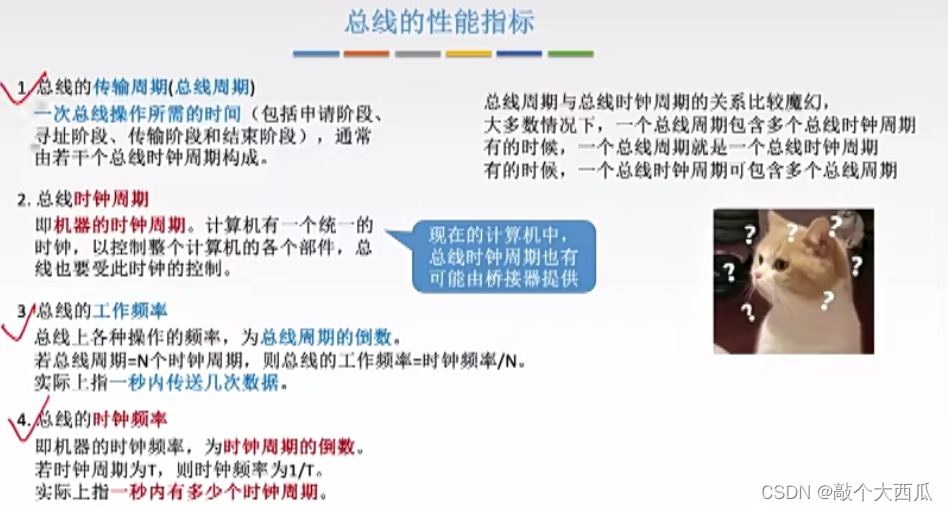

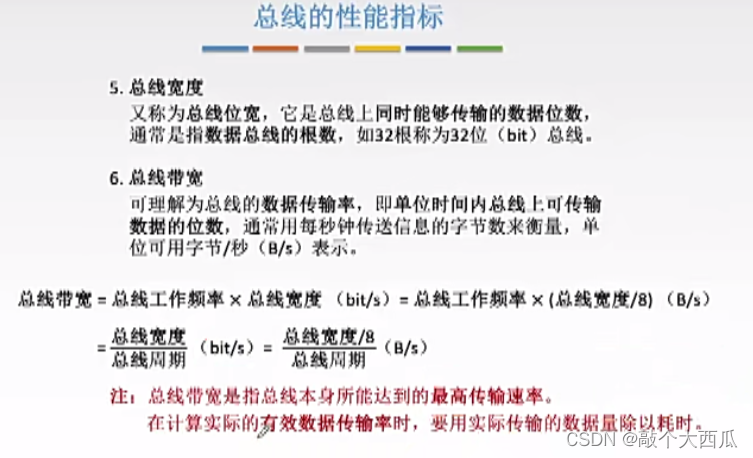

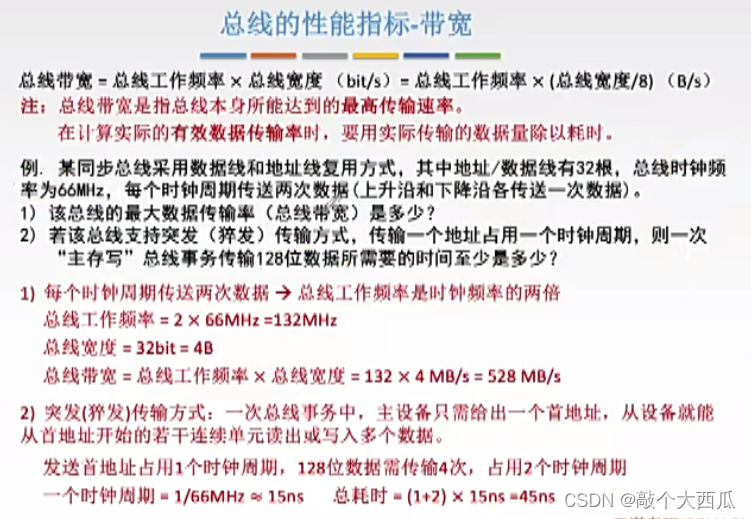

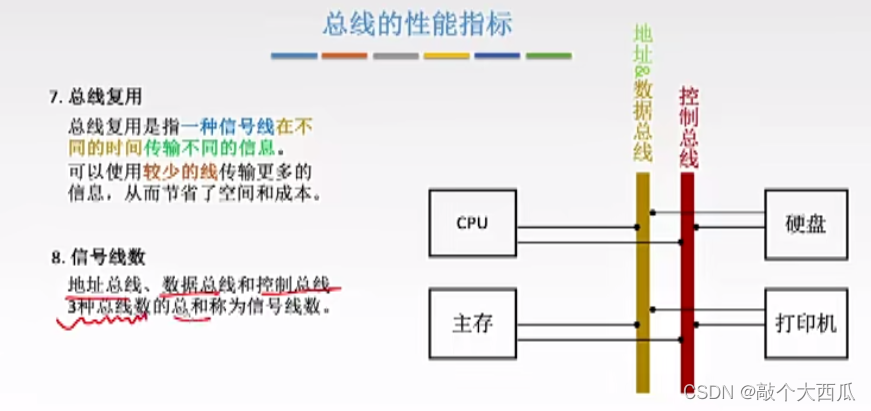

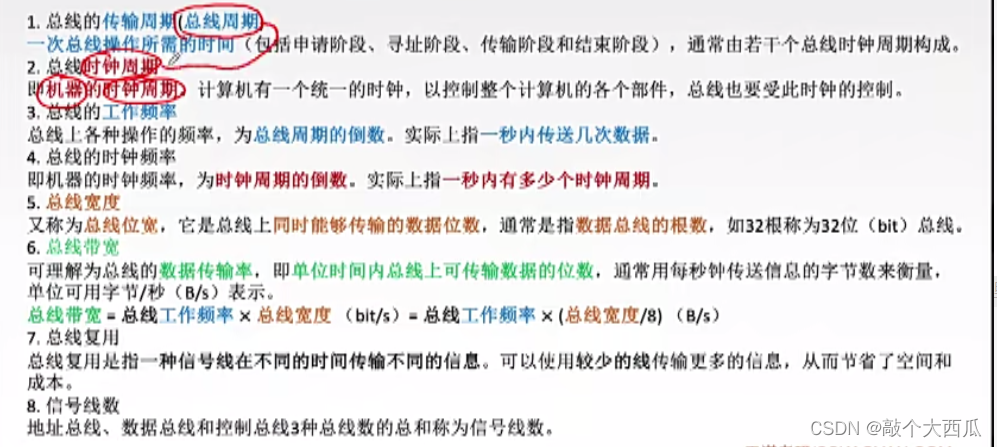

总线的性能指标

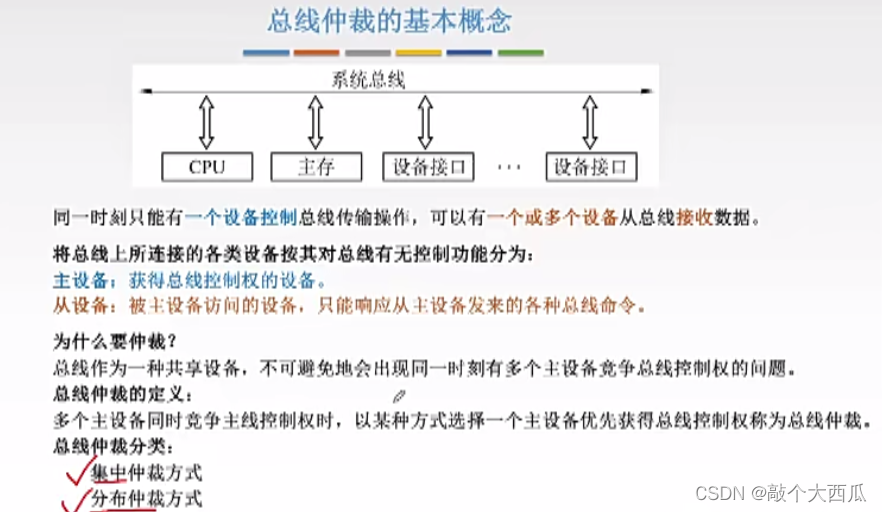

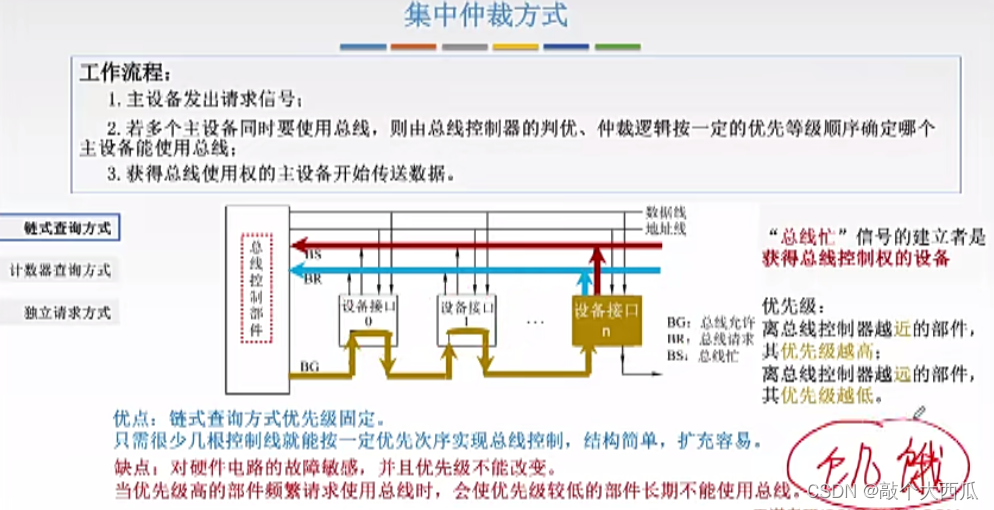

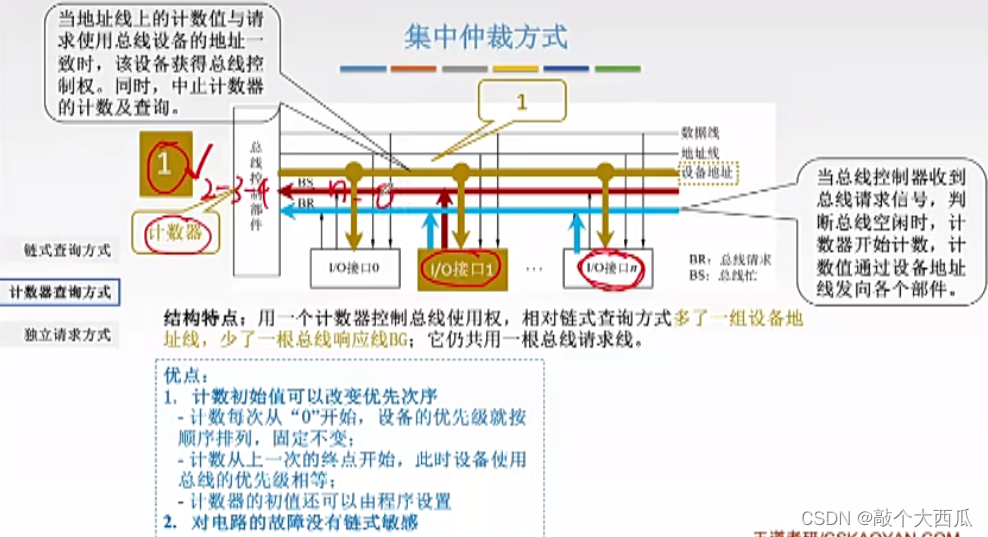

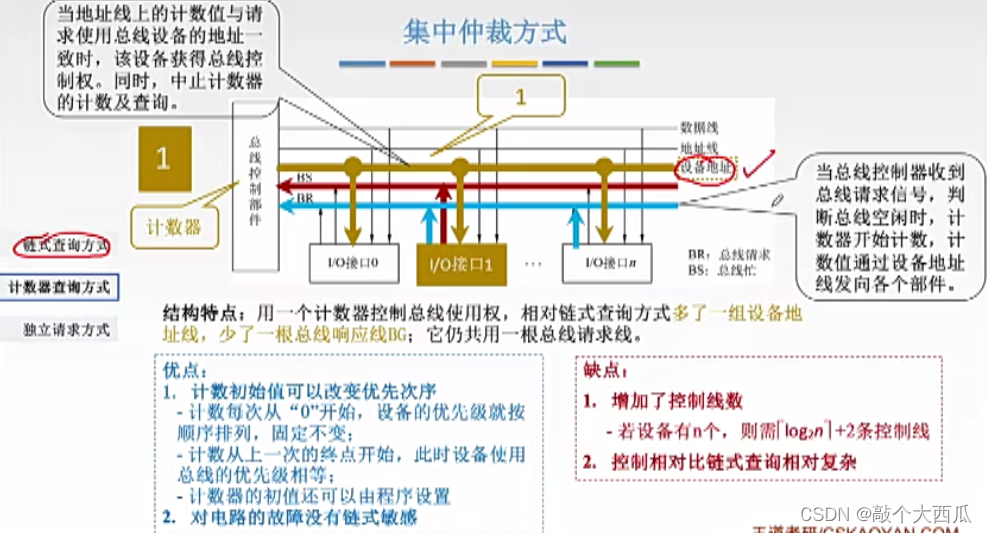

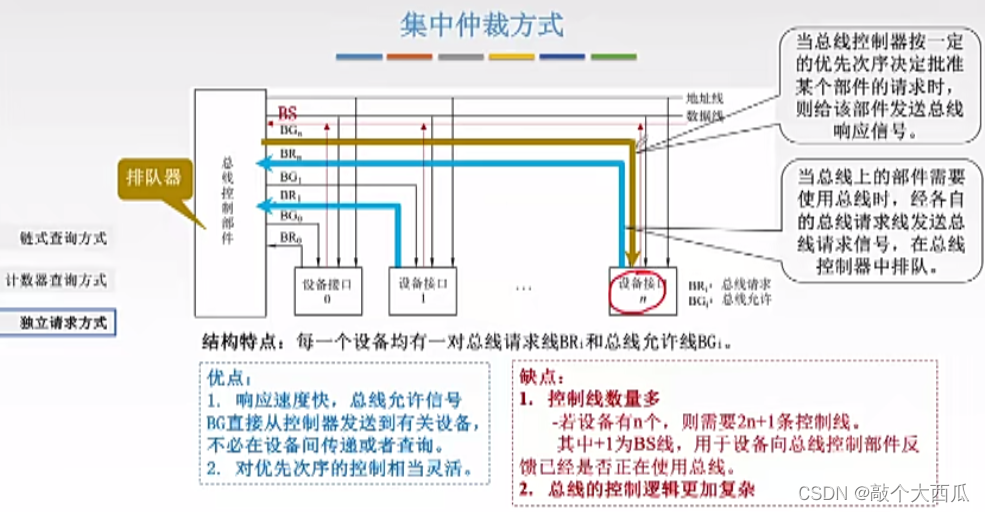

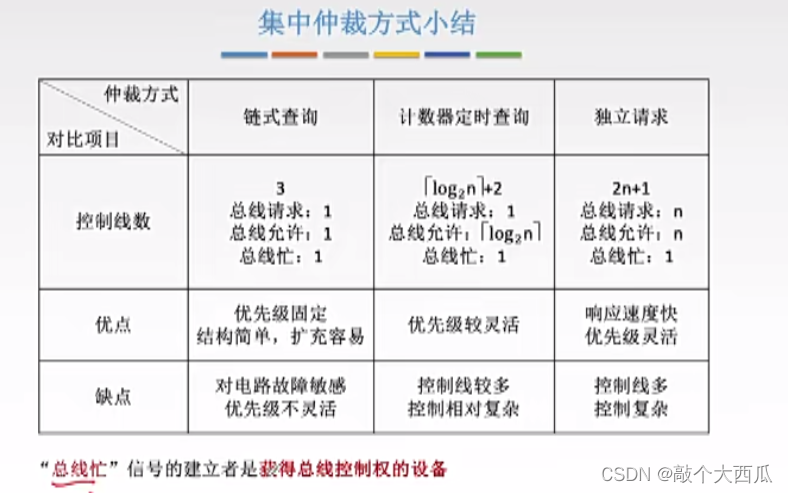

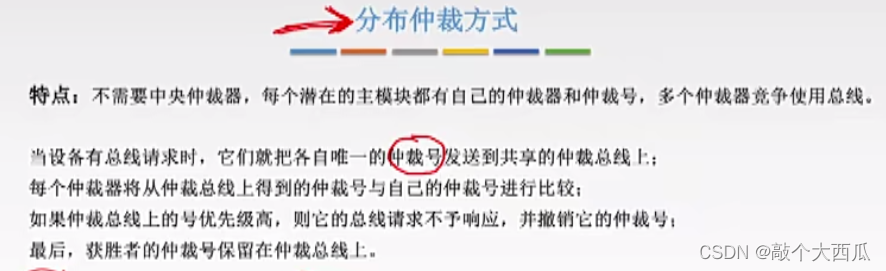

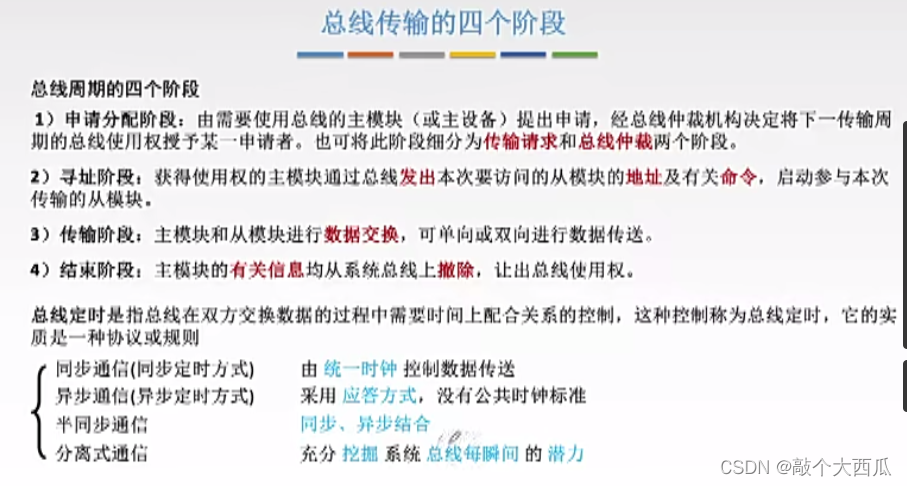

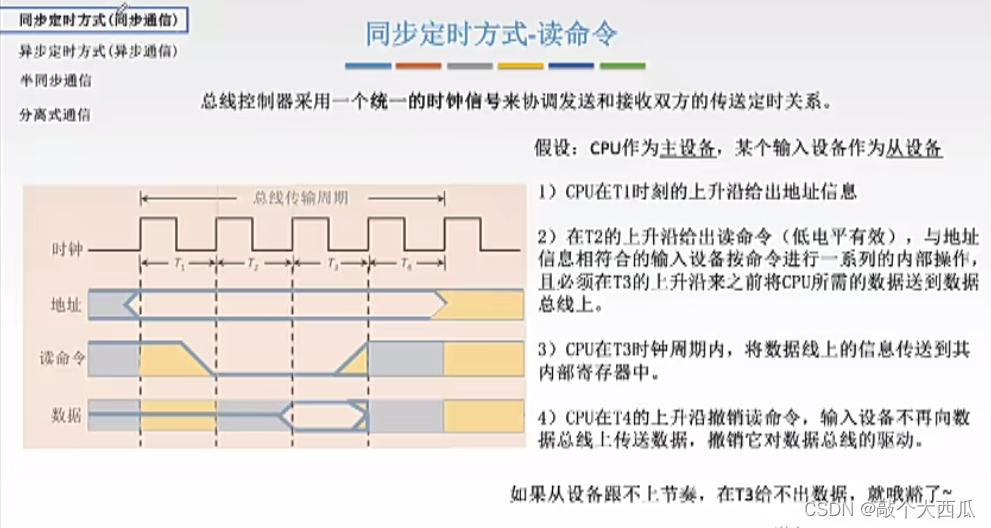

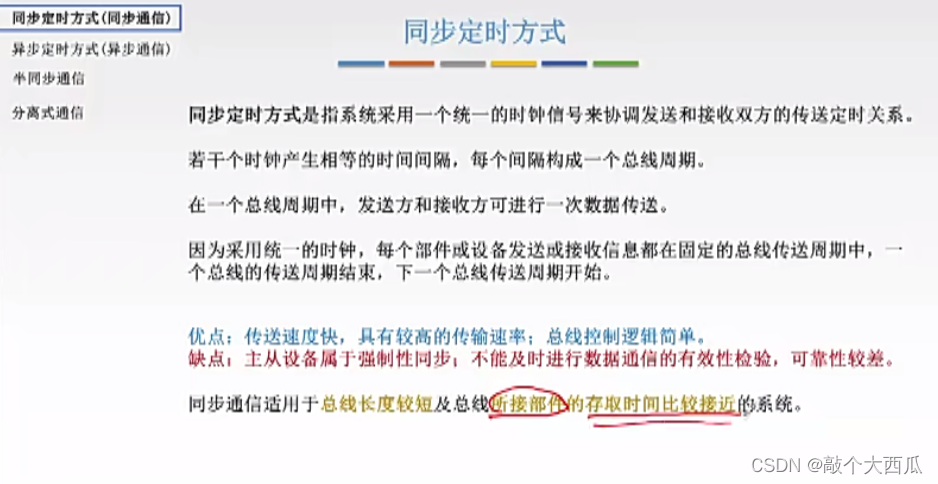

总线总裁

总线标准

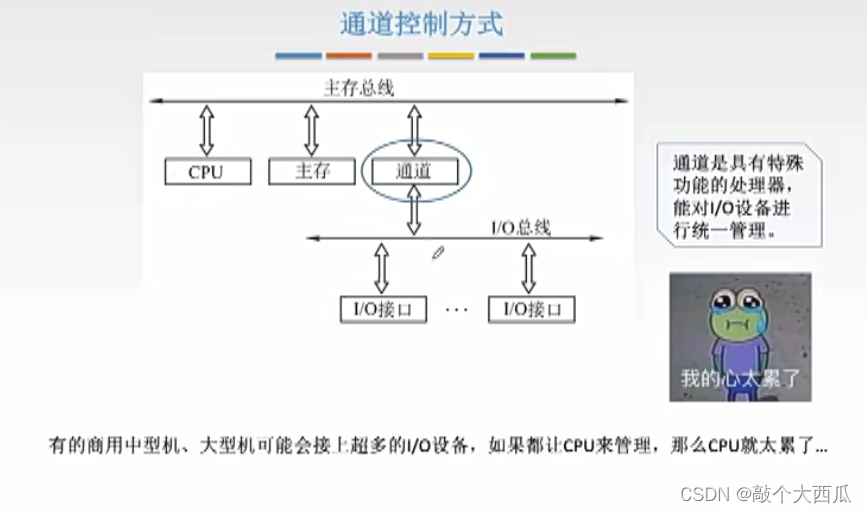

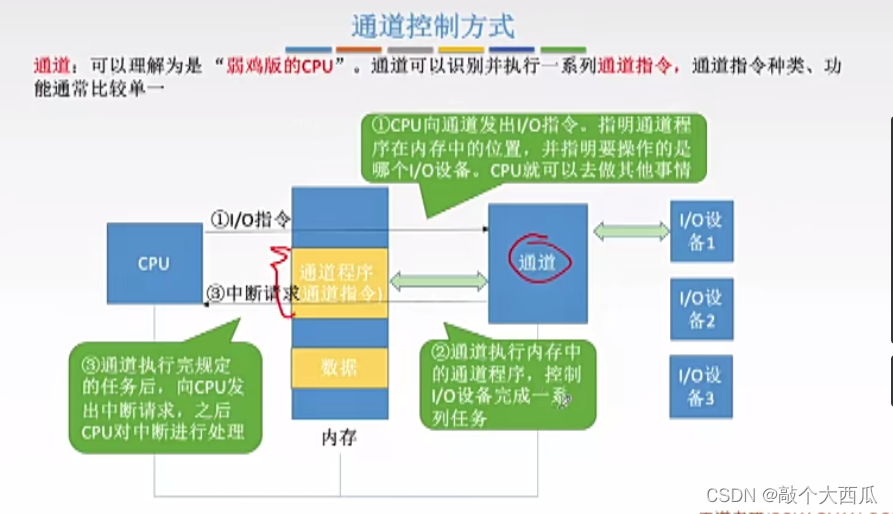

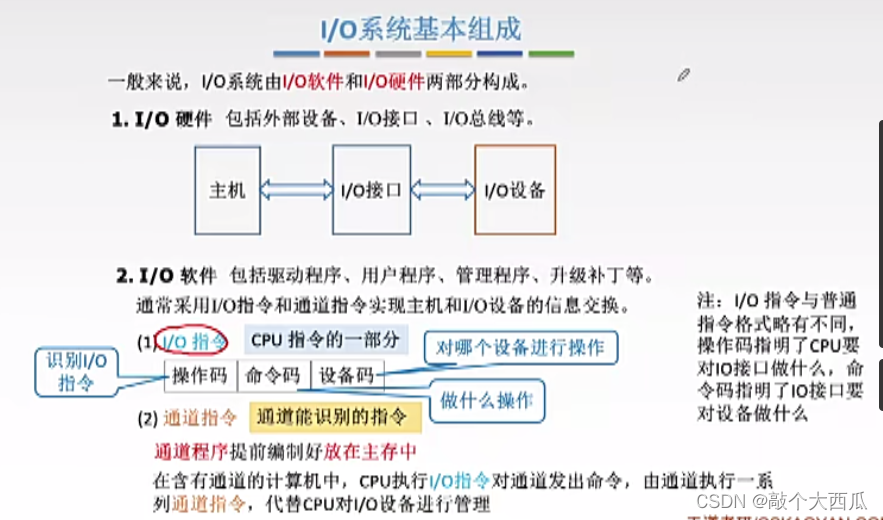

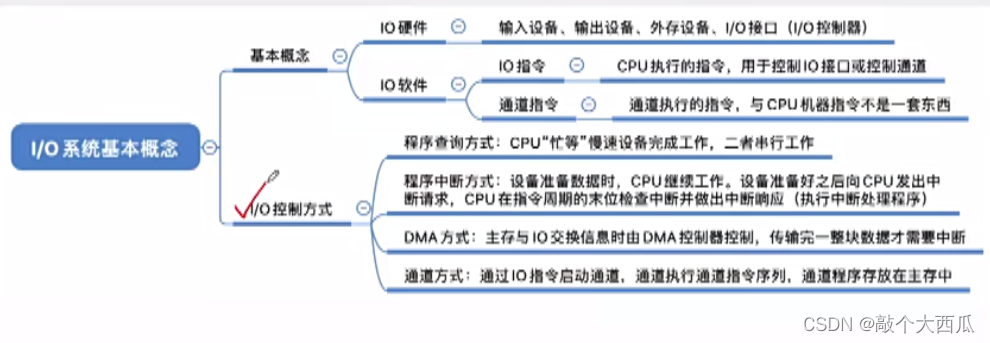

第七章 输入输出系统

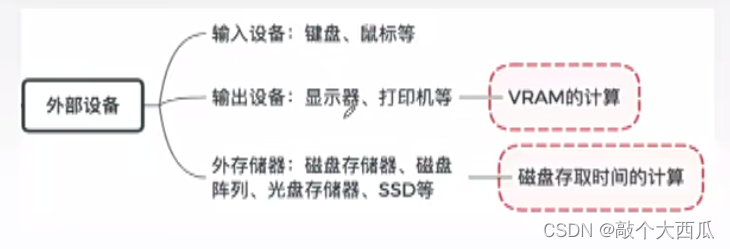

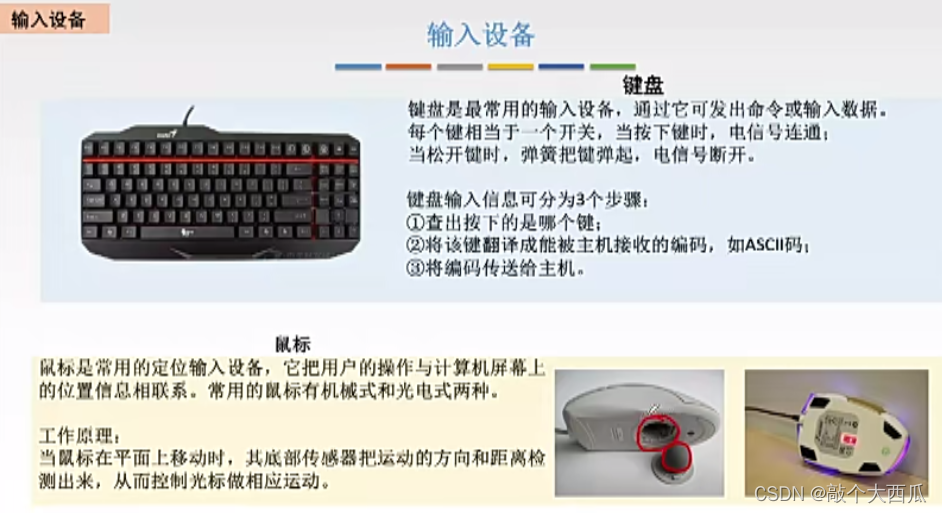

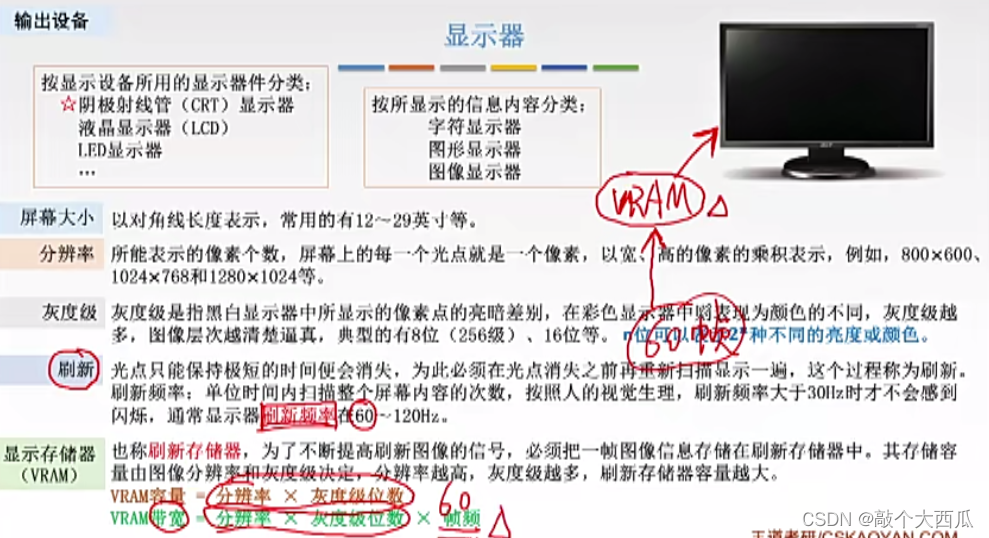

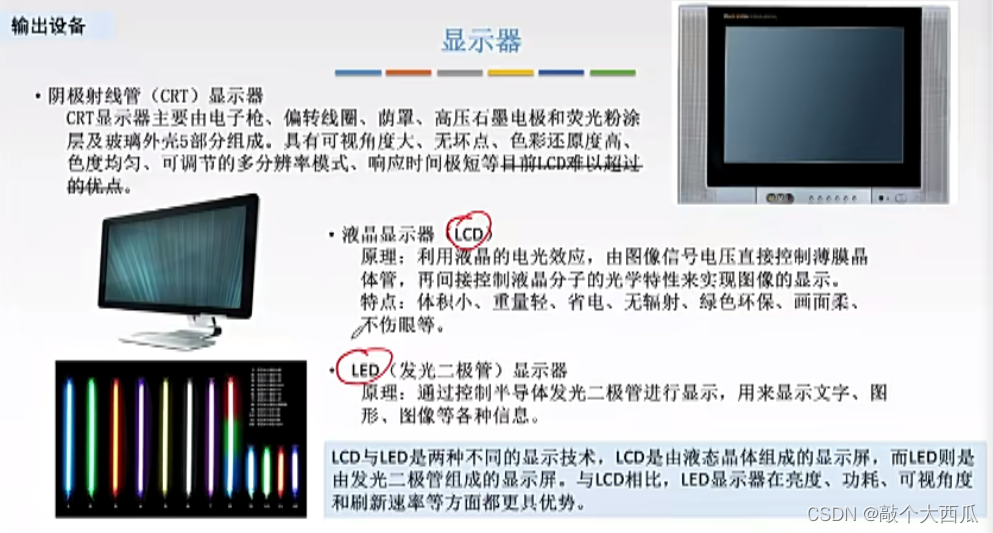

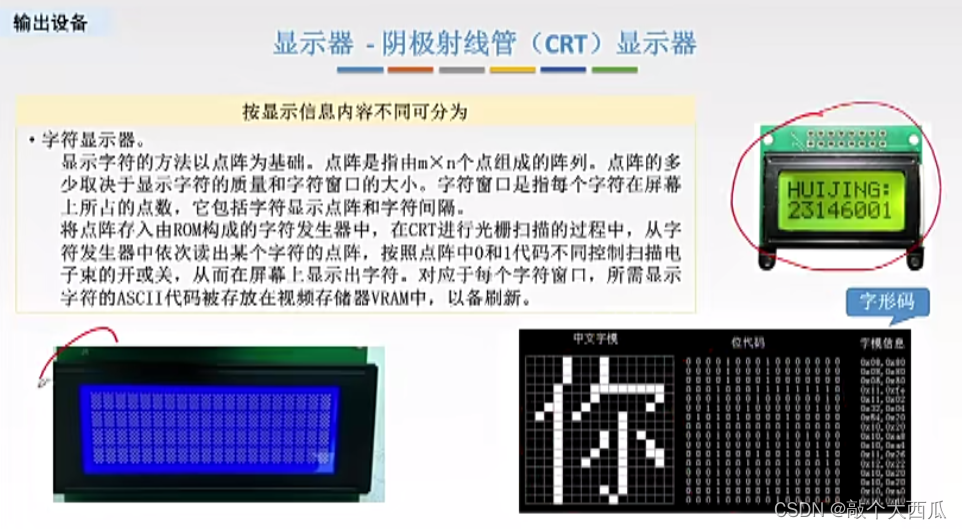

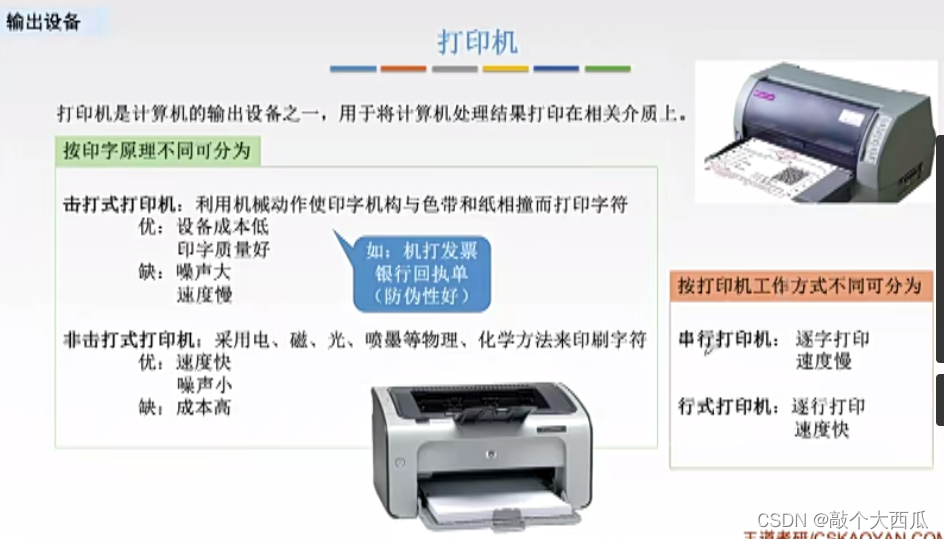

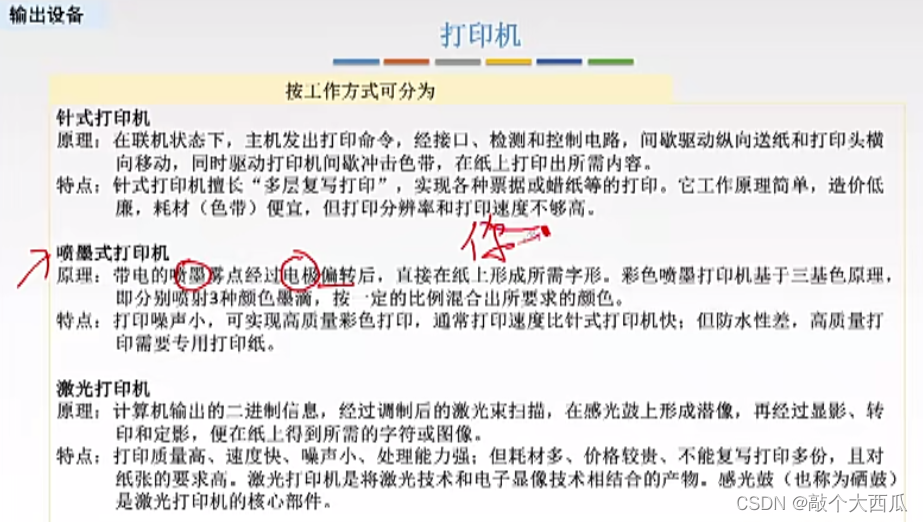

输入输出设备

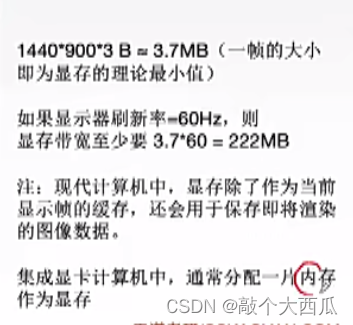

理论上计算机的显存大小最少是一帧的容量,

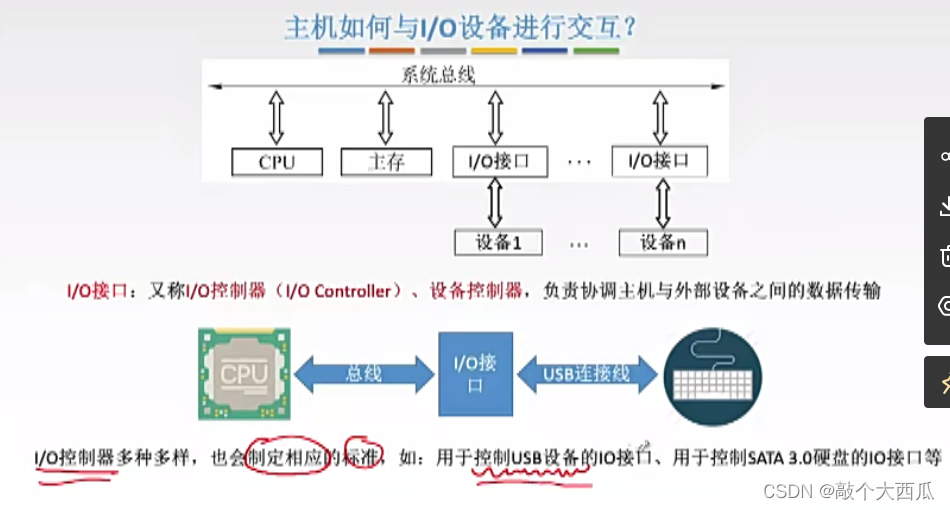

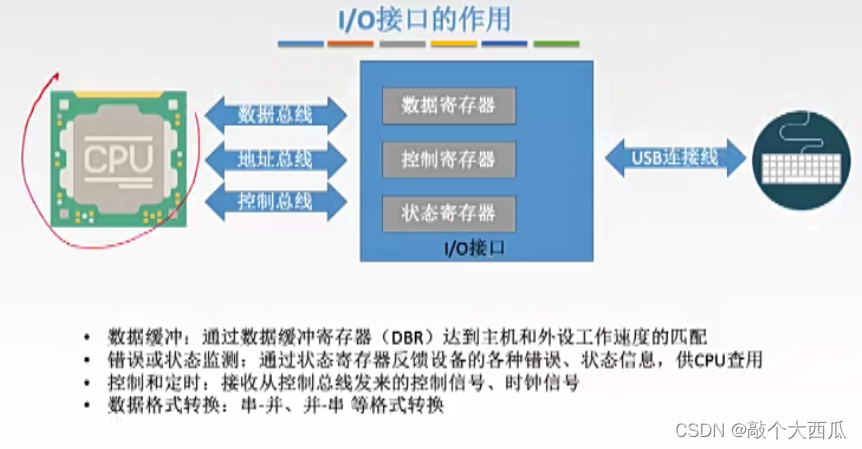

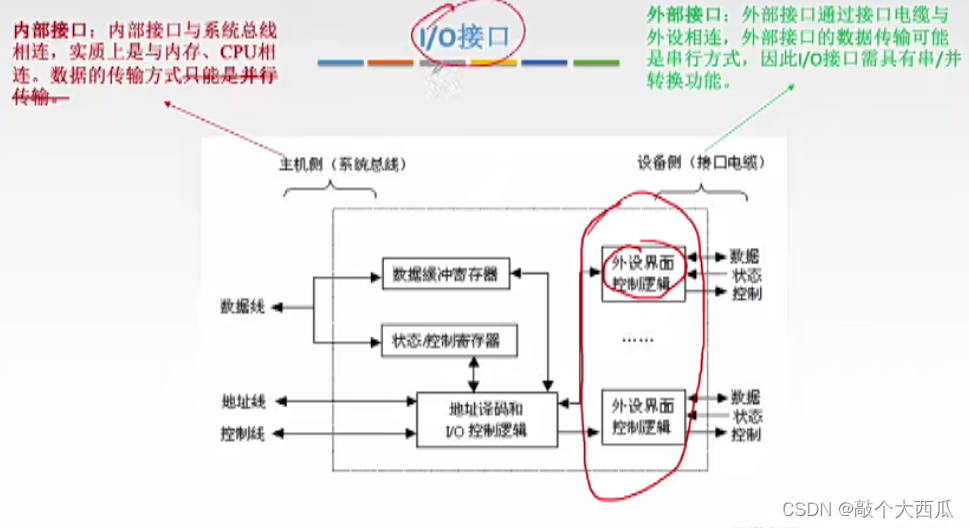

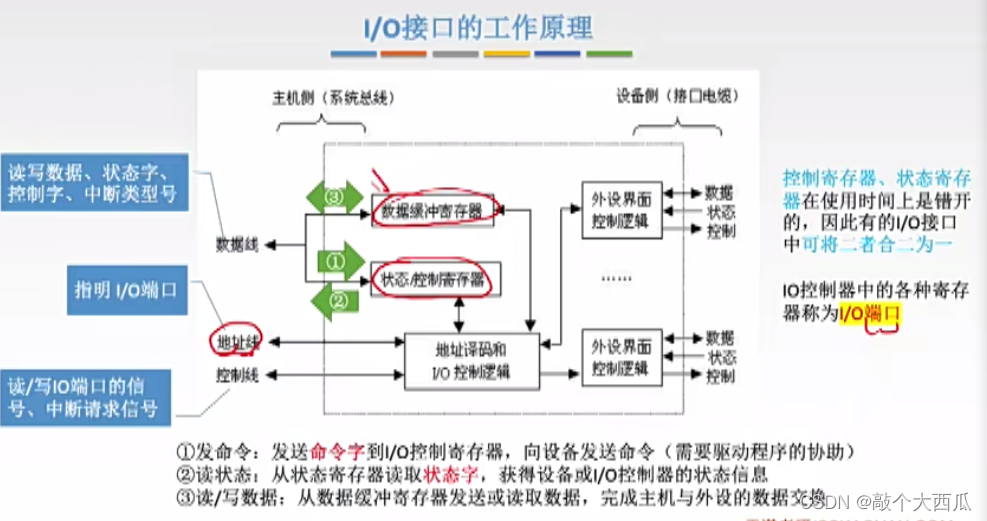

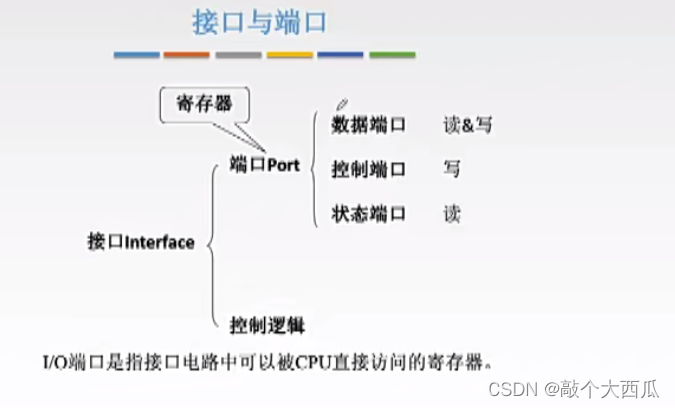

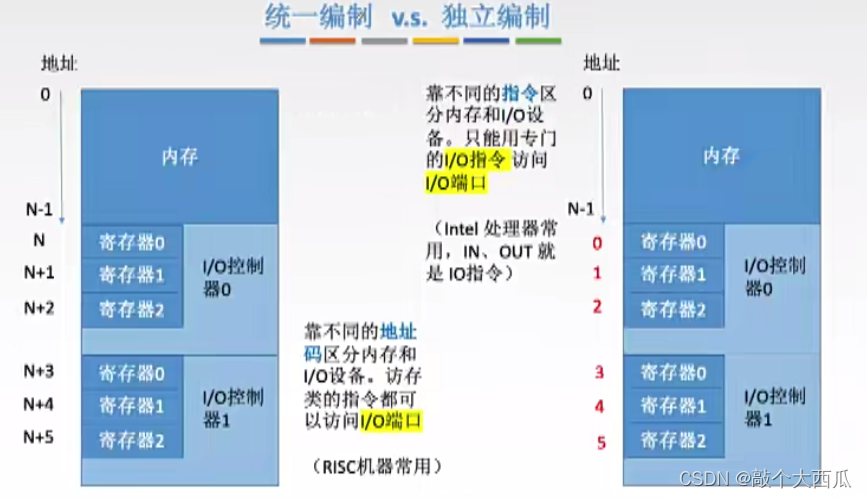

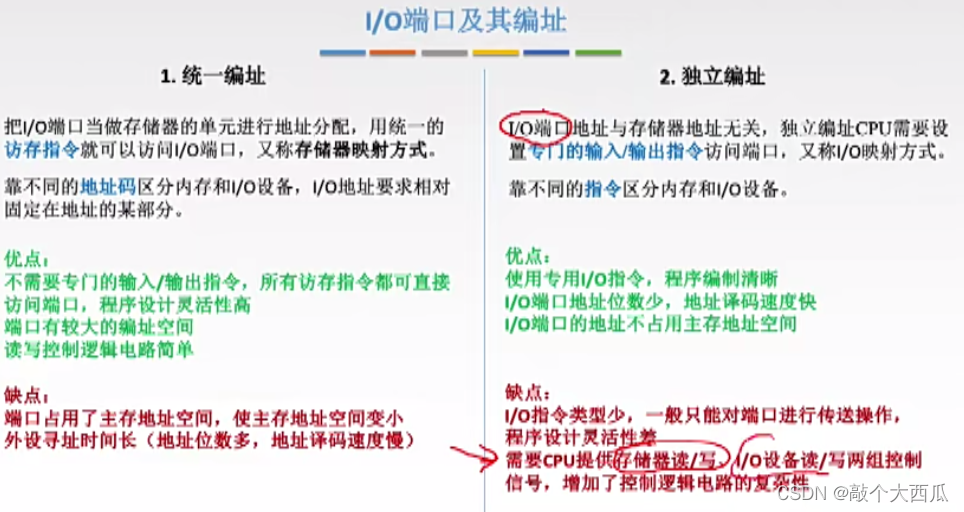

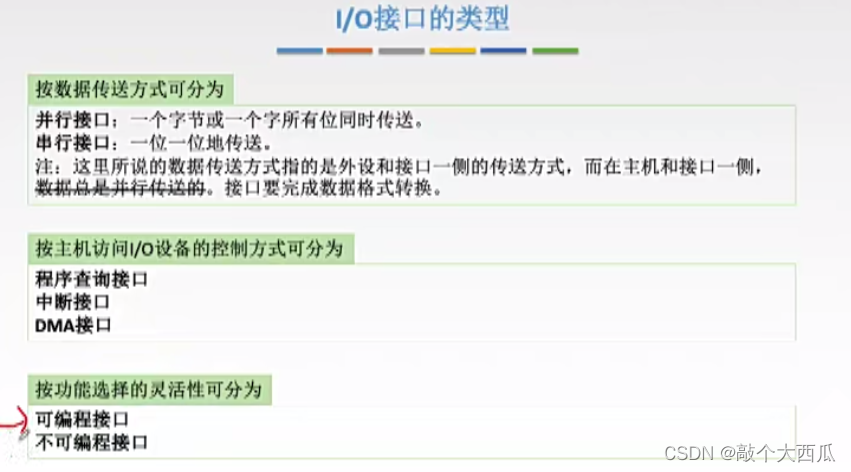

I/O接口

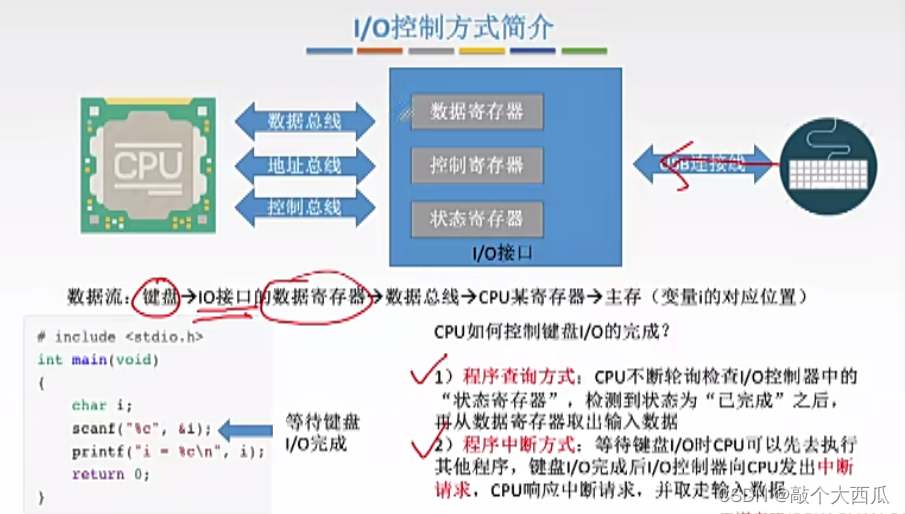

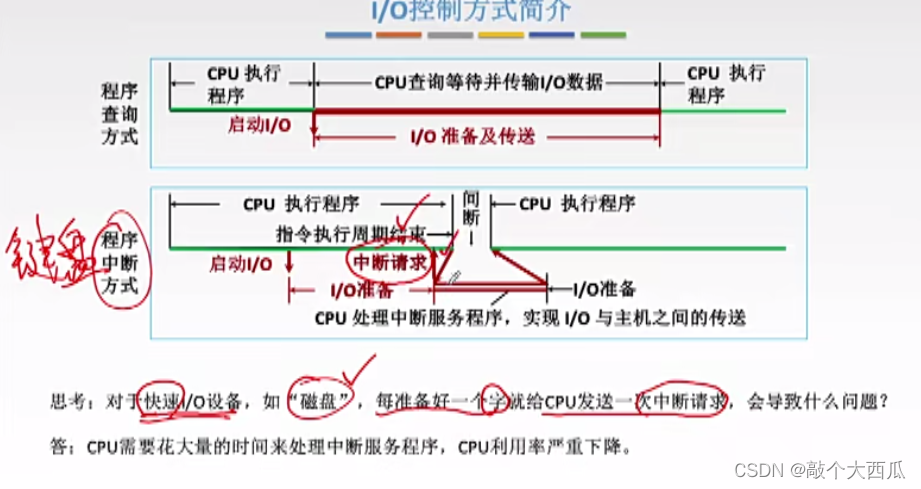

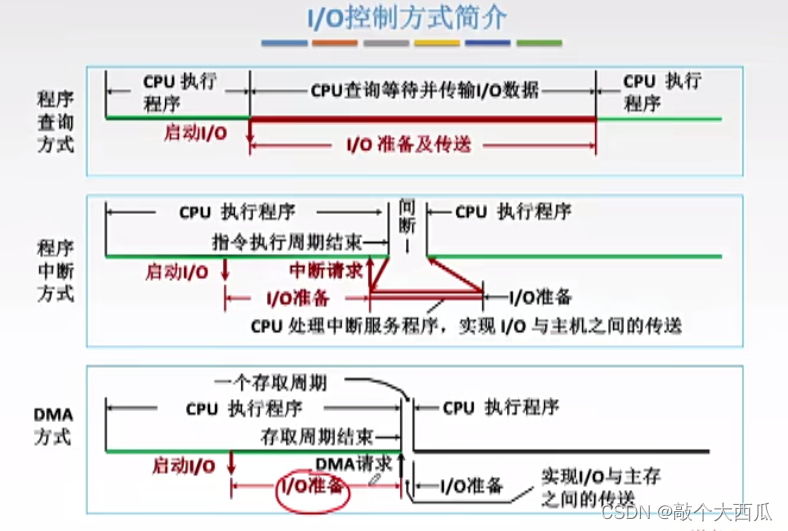

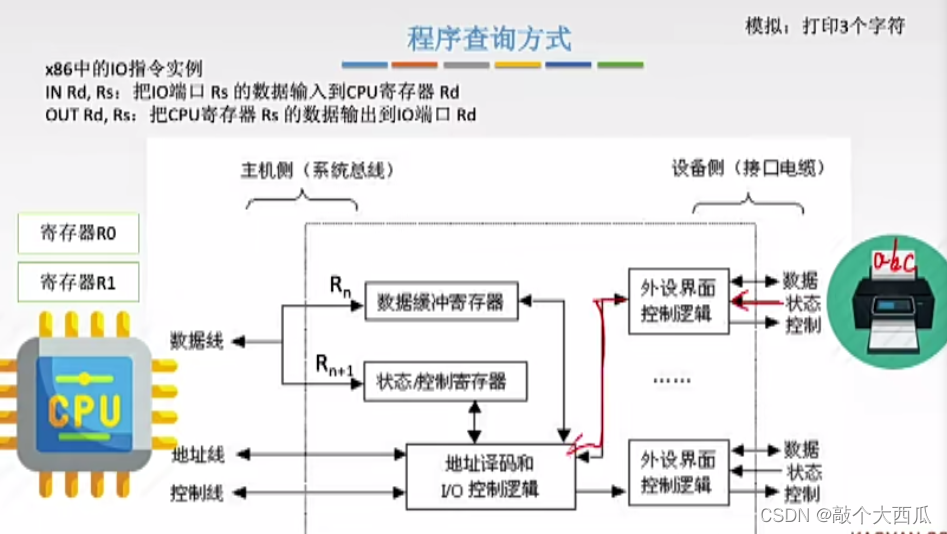

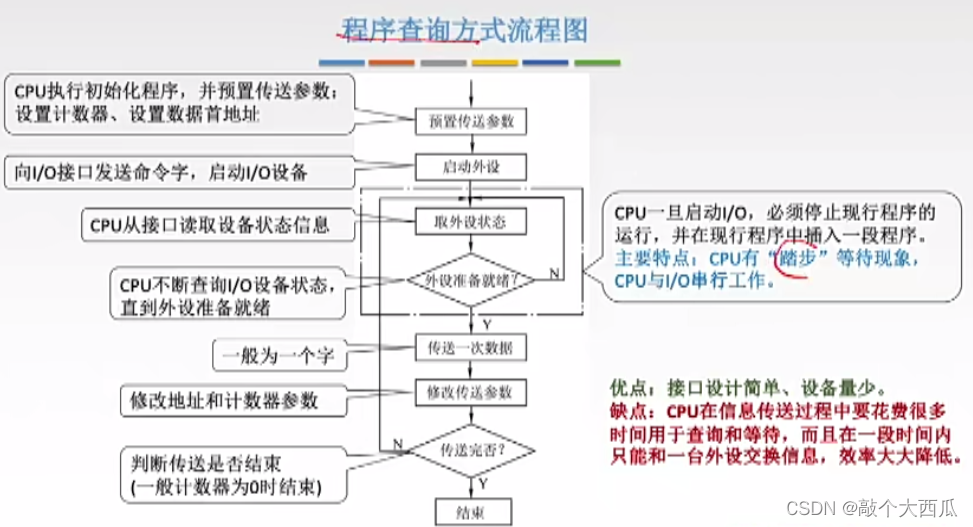

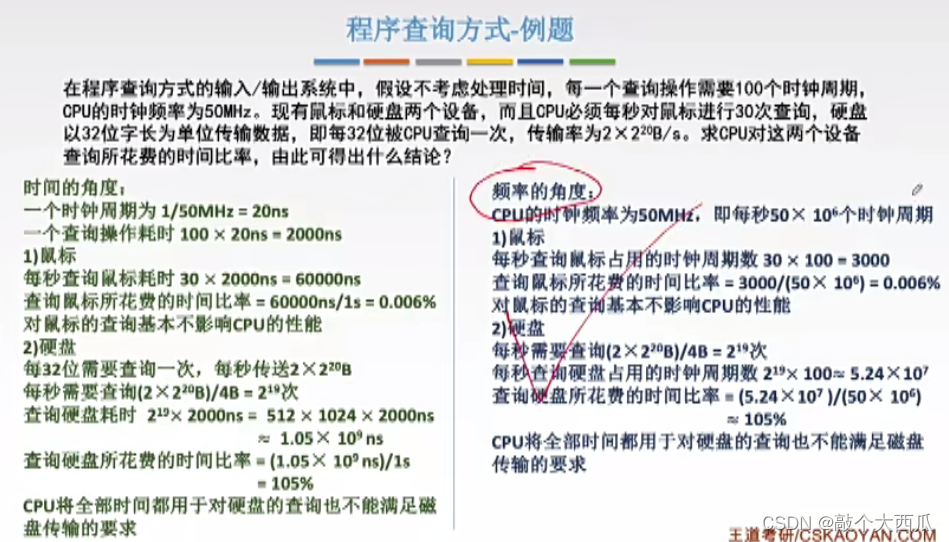

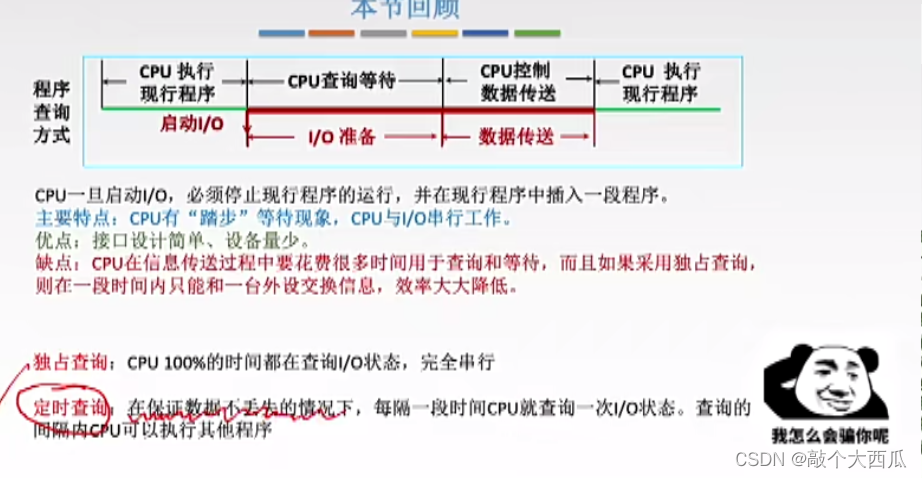

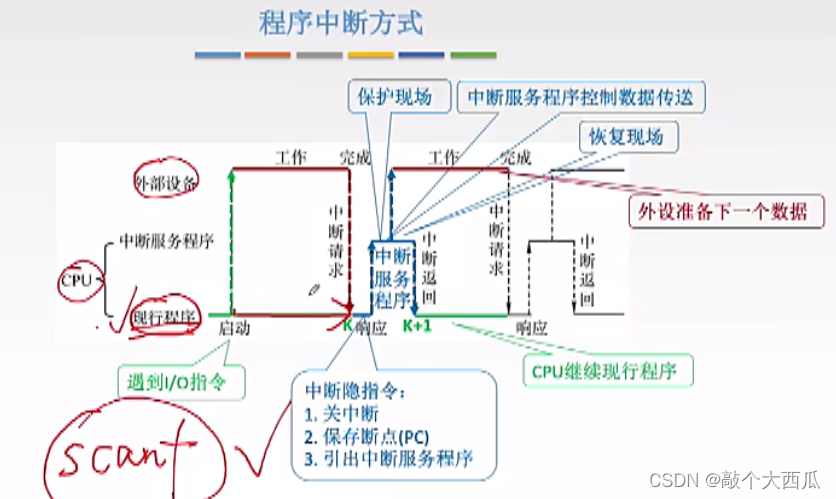

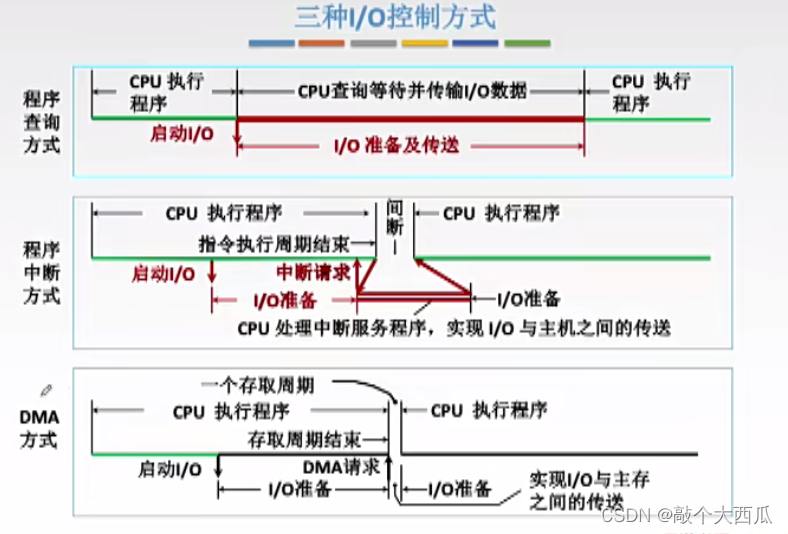

程序查询方式

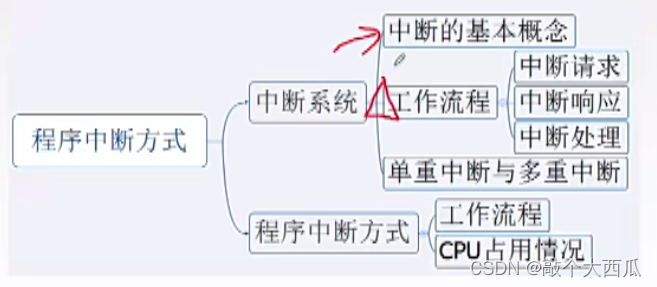

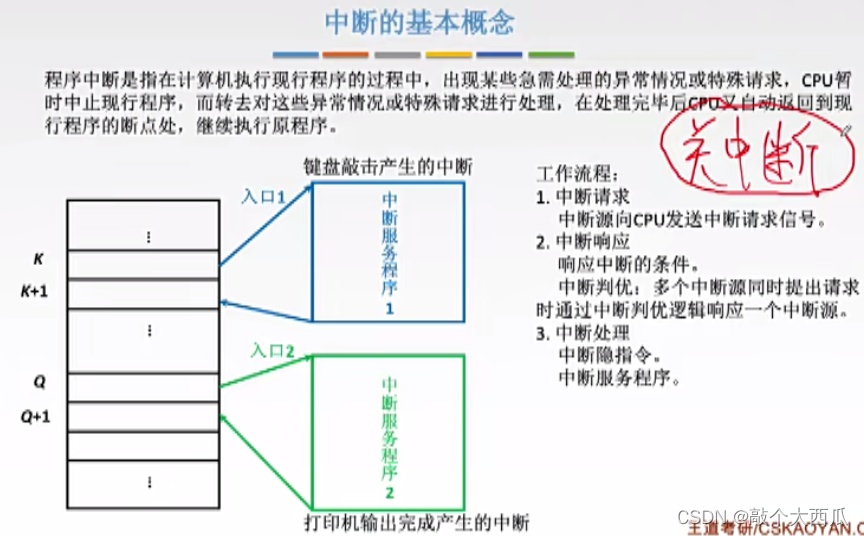

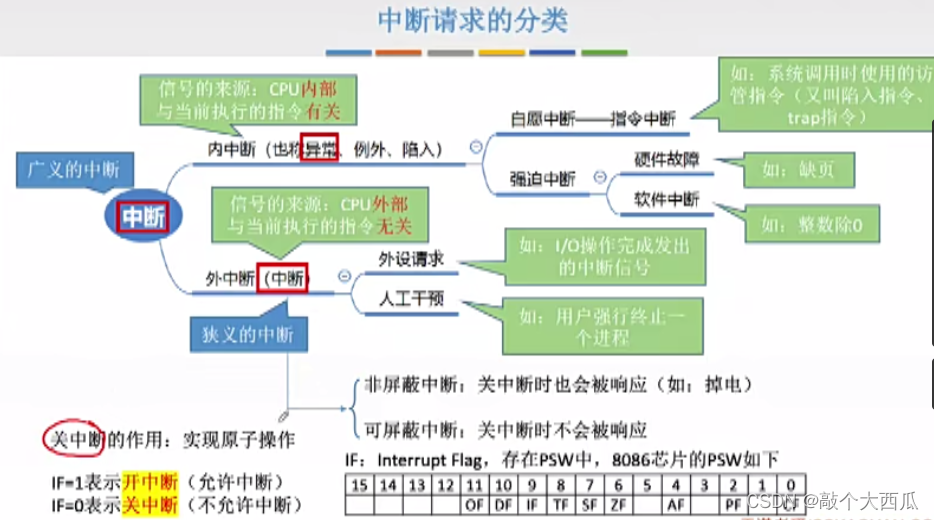

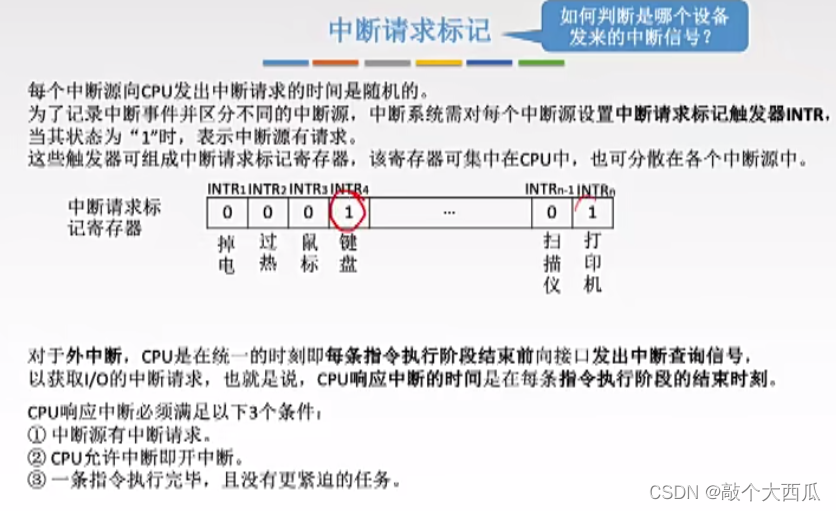

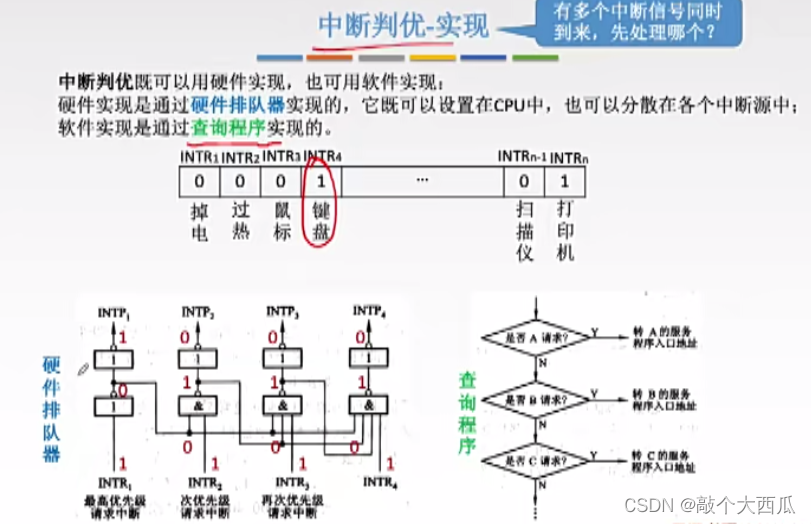

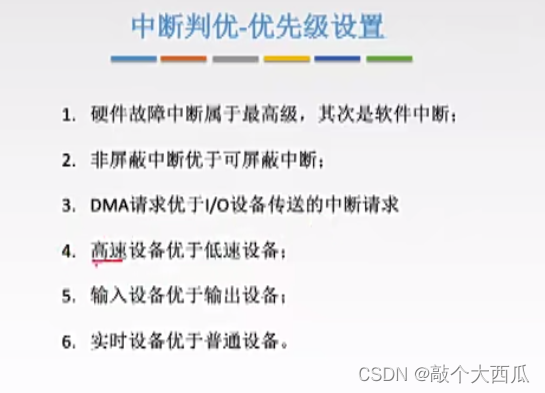

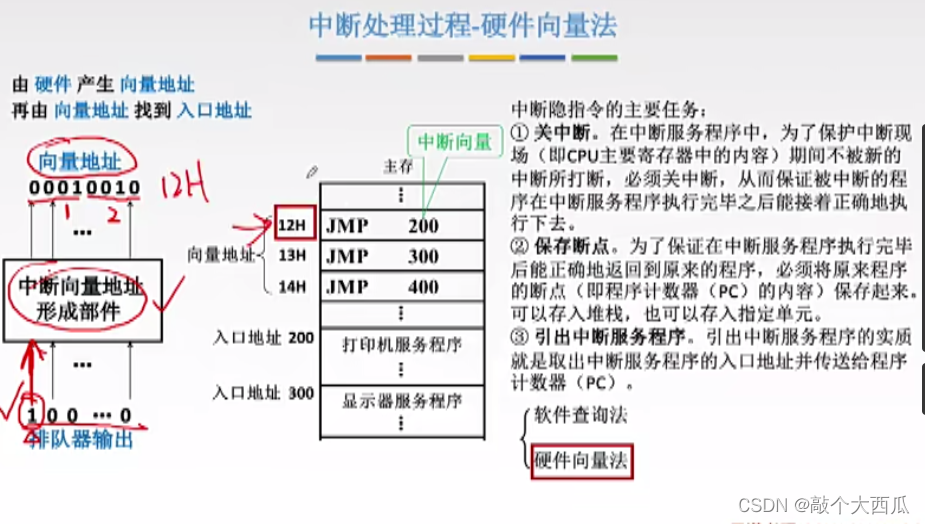

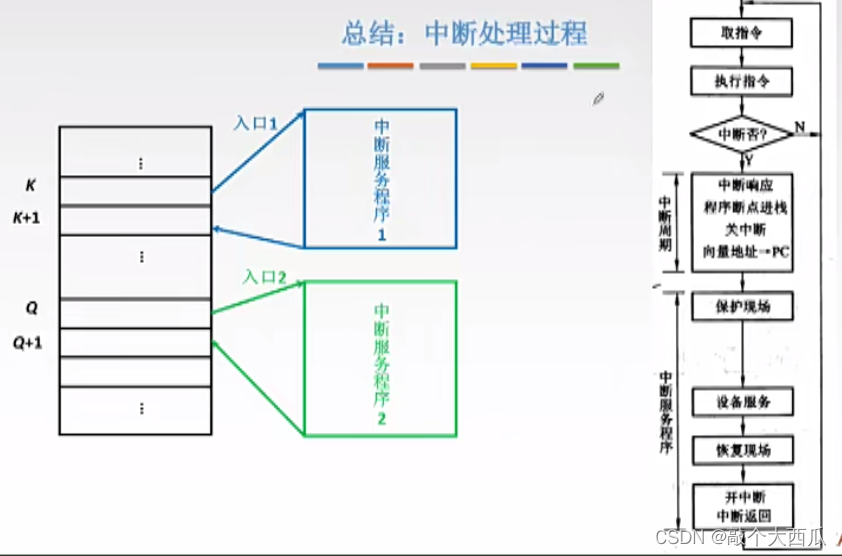

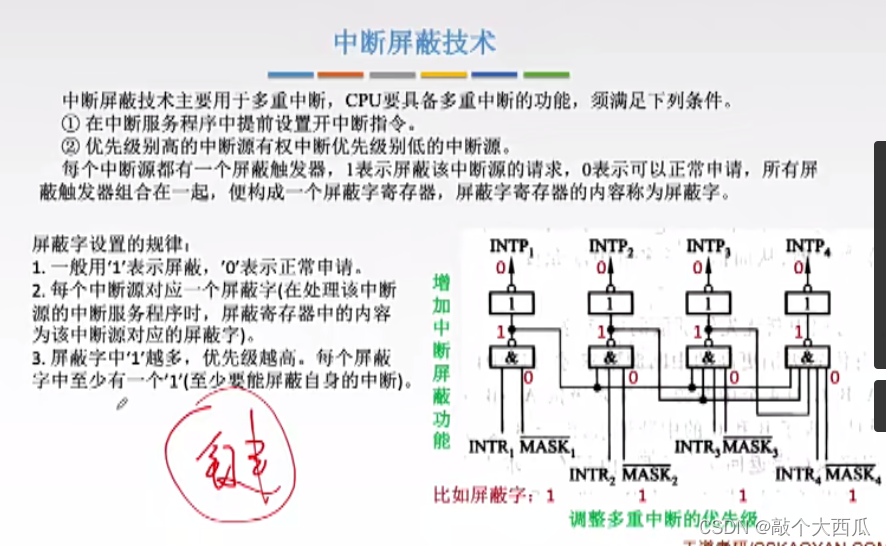

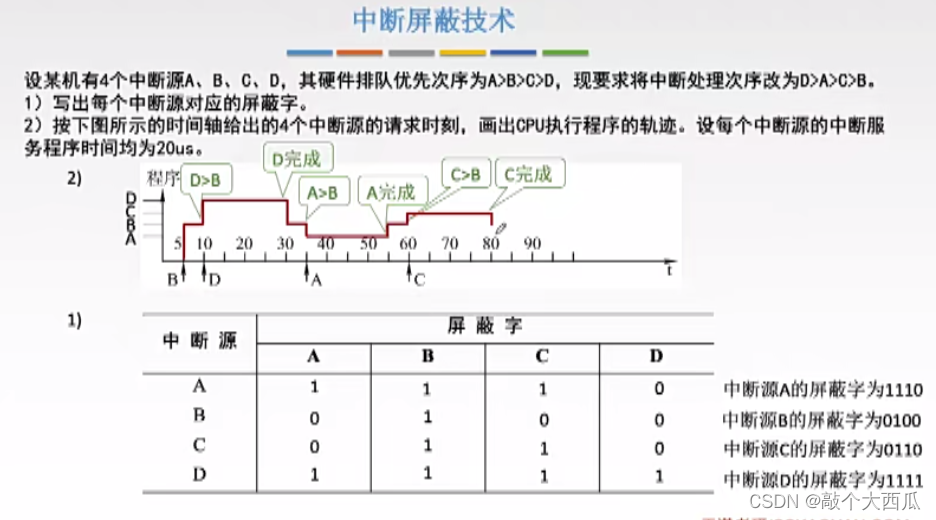

中断的作用和原理

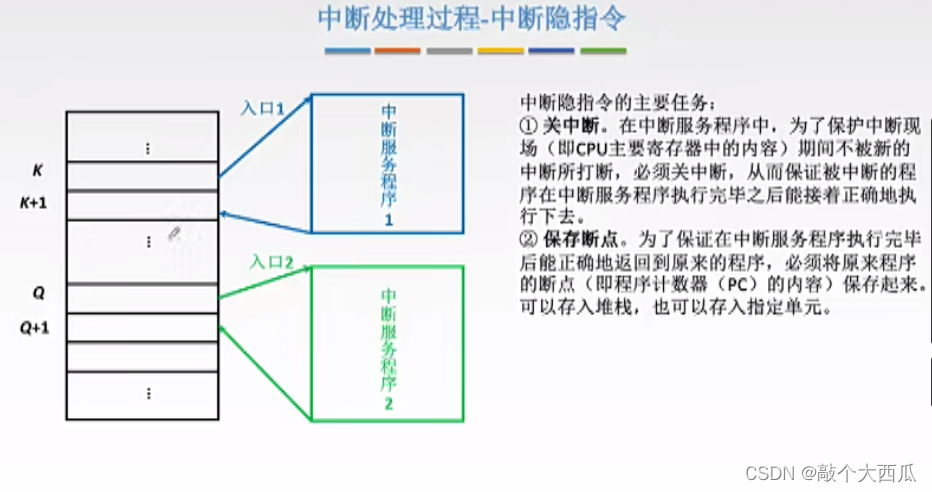

硬件快中断慢

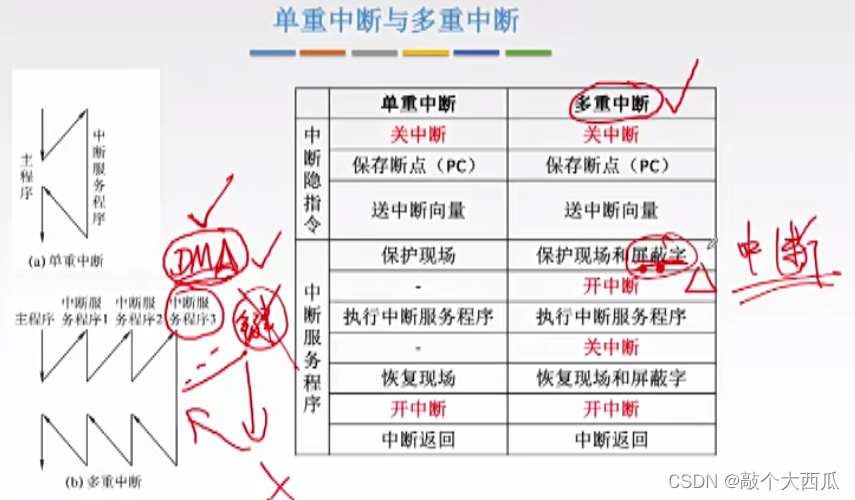

多重中断

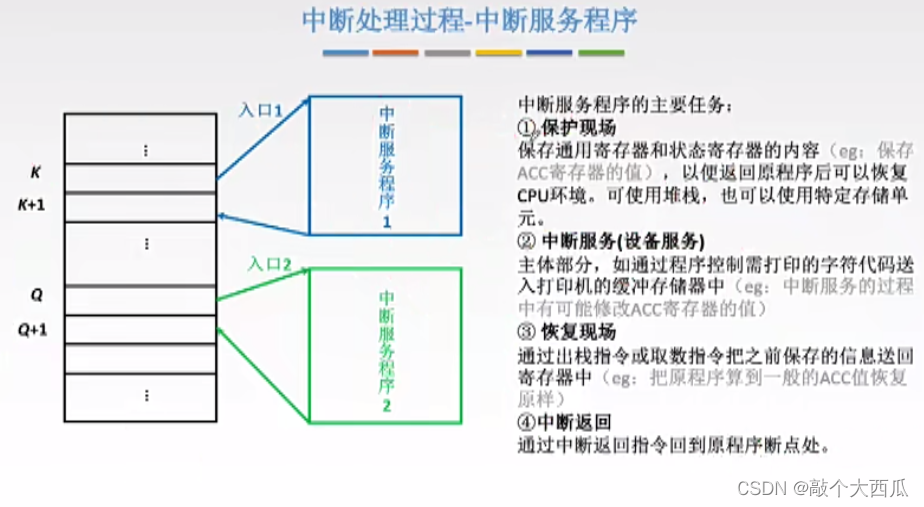

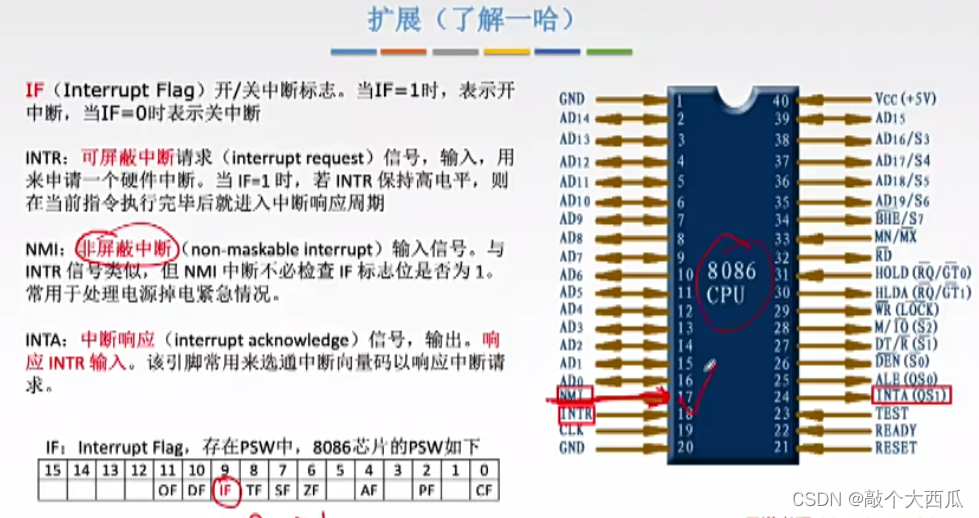

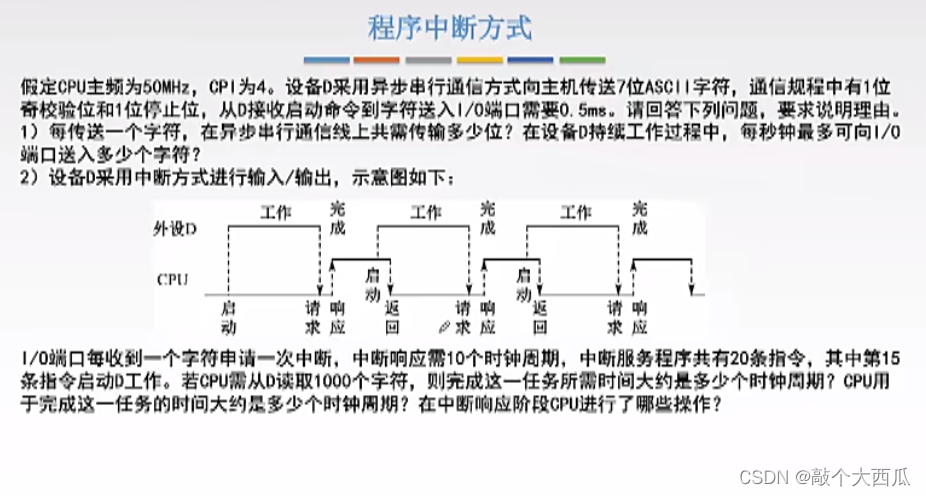

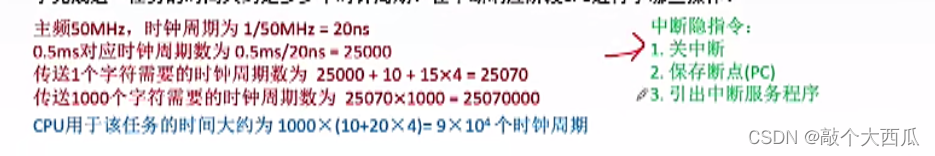

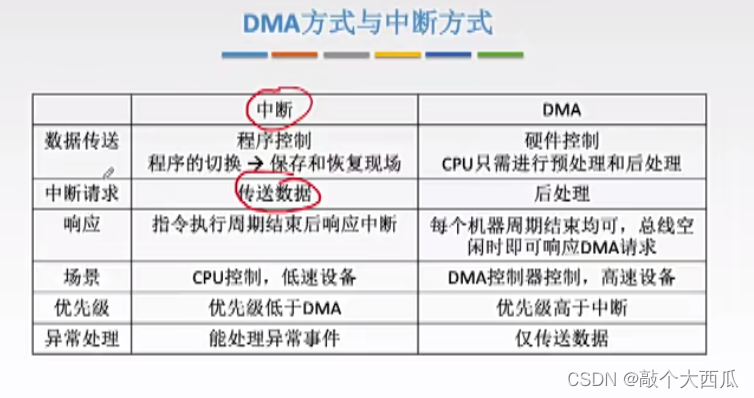

程序中断方式

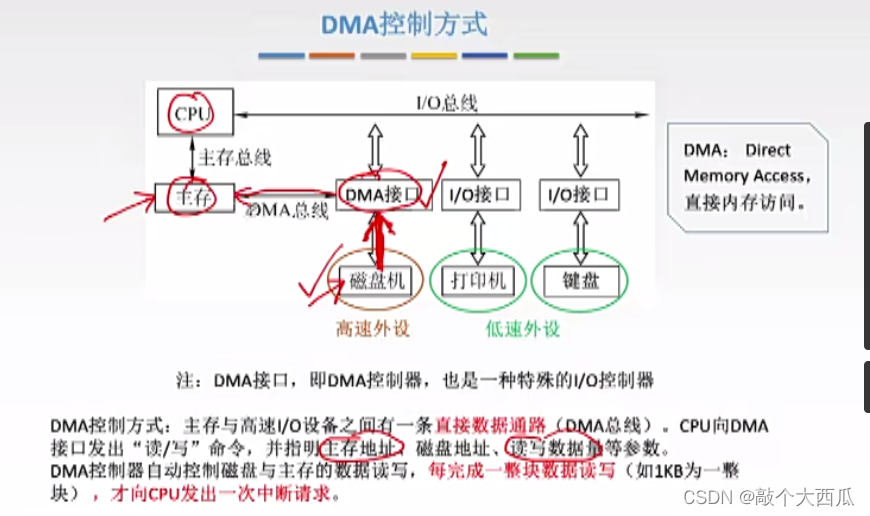

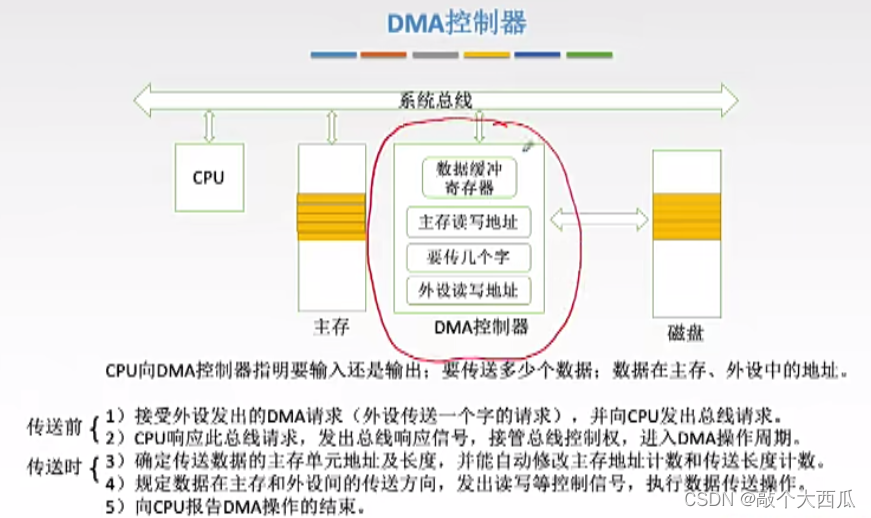

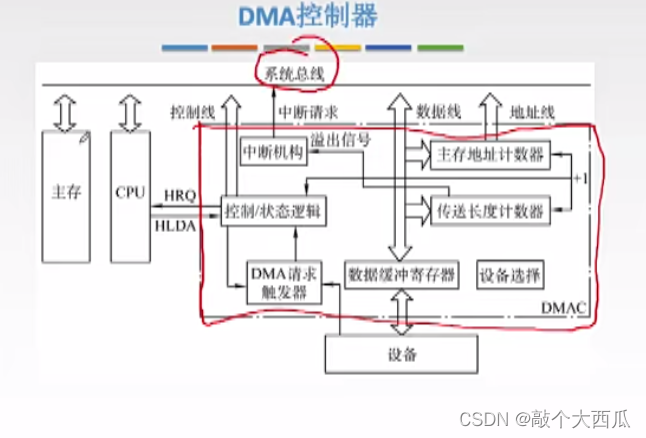

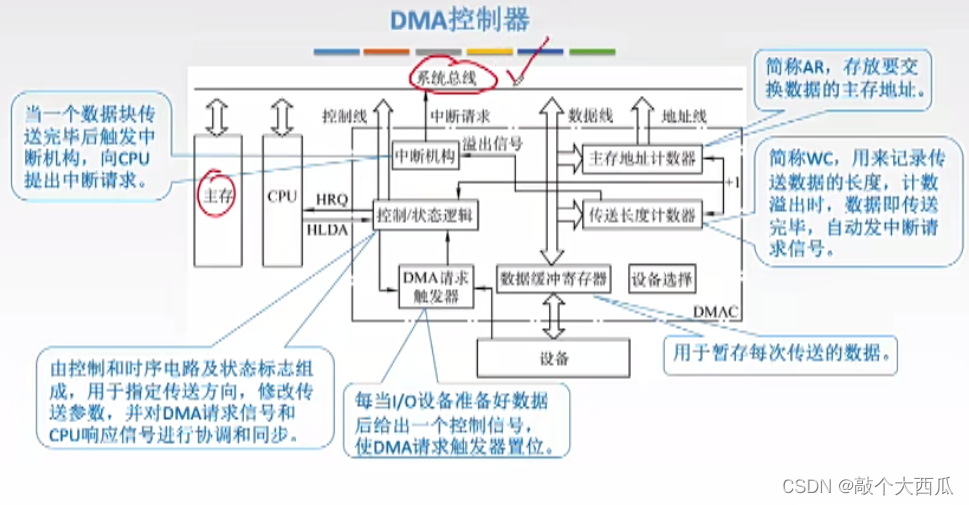

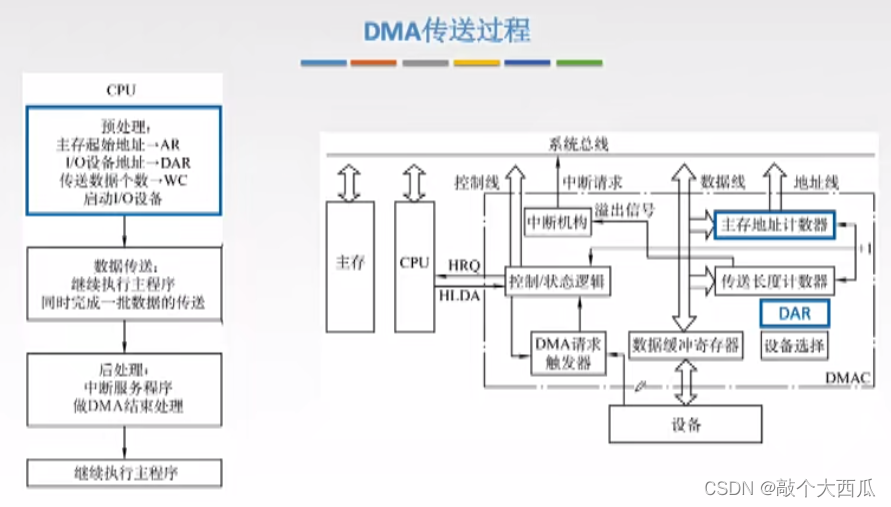

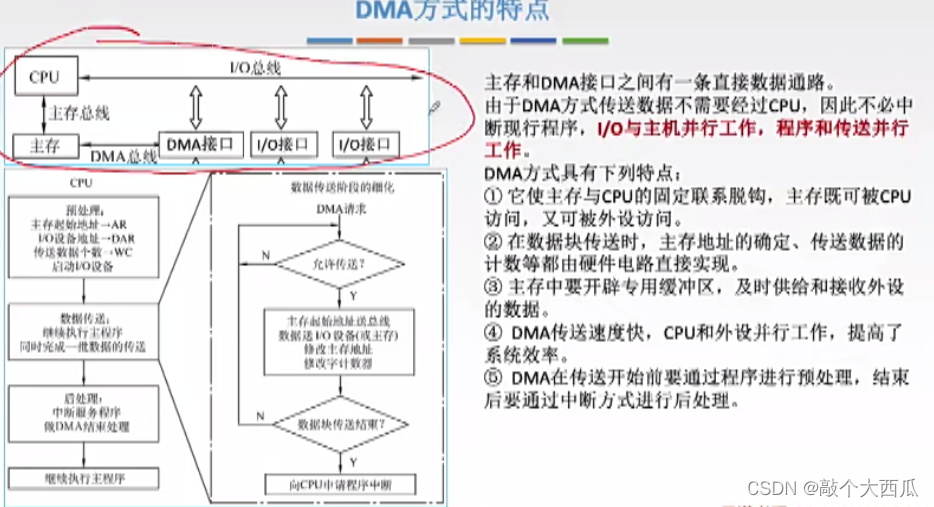

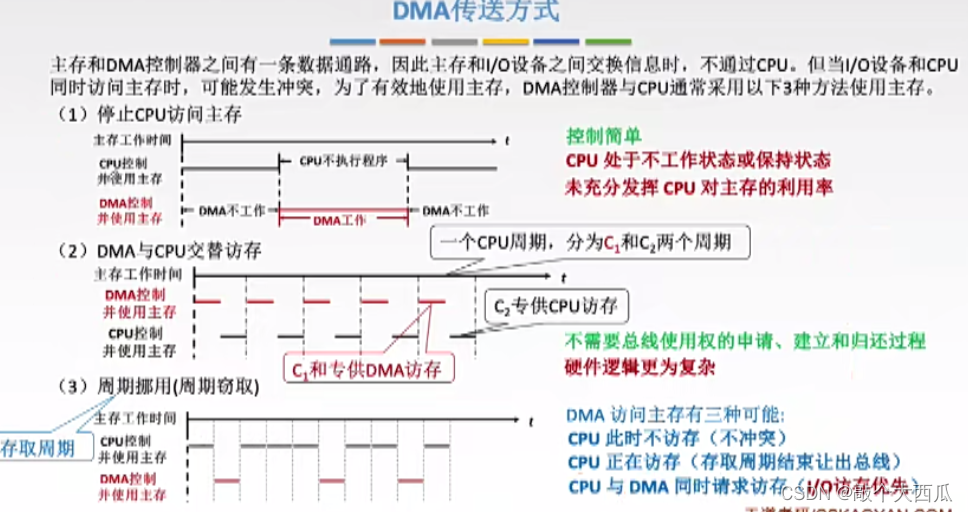

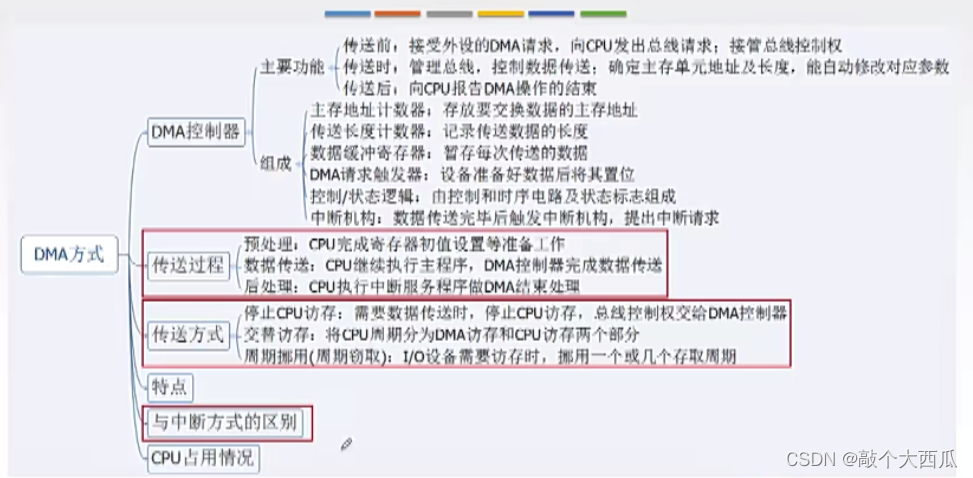

DMA方式传送

-

相关阅读:

SEO内链作用是什么,seo内链优化怎么做?

【鸿蒙学习笔记】交互事件

【GNN基础学习】图模块基本定义 || 图的邻接矩阵 || GNN中常见任务有哪些? || GNN消息传递方法 || 多层GCN有什么作用?

vue基于百度云实现行驶证识别

深度神经网络的训练过程,深度神经网络如何训练

物联网通信技术课程作业资料(TPUNB技术)

三、互联网技术——IP子网划分

快速幂取余

数字创新的风口:创业者如何在Web3时代抢占先机

《数据结构与算法基础 by王卓老师》学习笔记——1.4算法与算法分析

- 原文地址:https://blog.csdn.net/wangjunlei666/article/details/126644209