-

STM32 GPIO工作原理

STM32 GPIO工作原理

STM32引脚说明

共有7组IO口,每组IO口有16个IO-—共16X7=112个IO

编号为:GPIOA,GPIOB……GPIOG,从A到G刚好7组

共有4组IO口,共16X3+3 = 51个IO

编号为:GPIOA0 ~ GPIOA15

GPIOB0 ~ GPIOB15

GPIOC0 ~ GPIOC15

GPIOD0 ~ GPIOD2

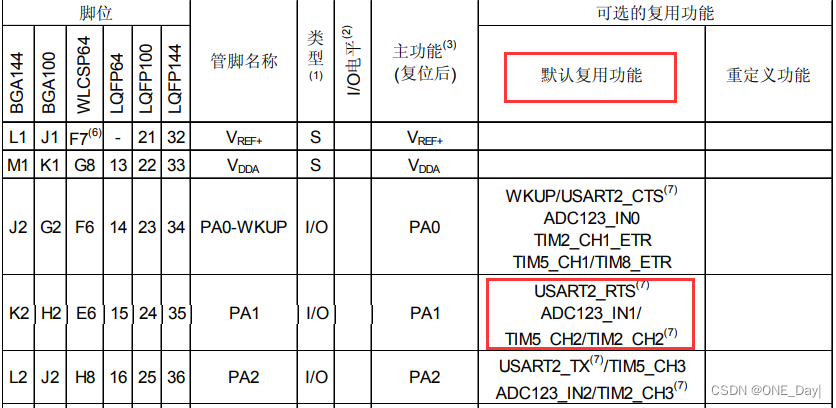

STM32的大部分引脚除了当GPIO使用外,还可以复用为外设功能引脚(比如串口)

在STM32F103ZET6的数据手册中可以看到GPIO说明表,表中的 I/O Level 项带有FT表示该引脚容忍5V,也就说虽然引脚输入输出3.3V,但你输入一个5V,引脚也可以判断为高电平,没带FT标志的说明该引脚不容忍5V

GPIO的工作方式

4种输入模式:

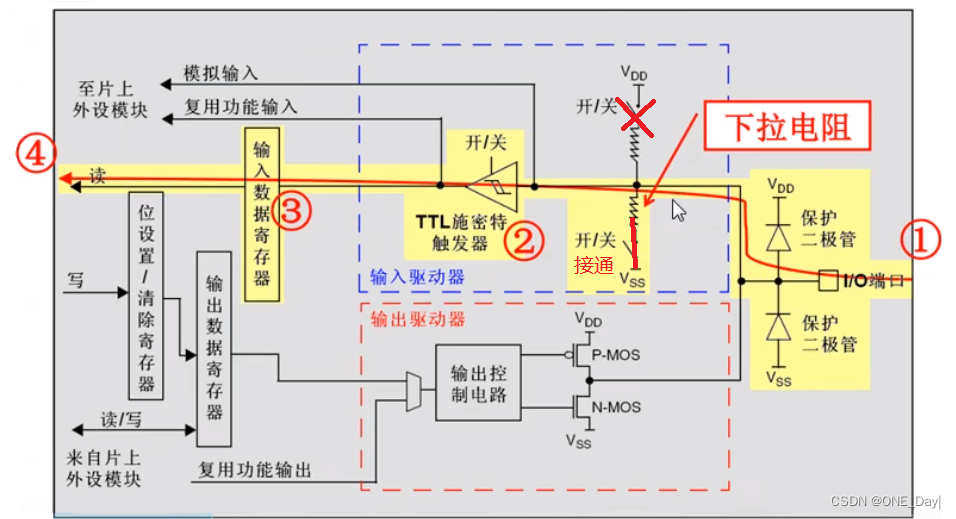

1.输入浮空

2.输入上拉

与输入浮空差不多,只是上拉电阻开关接通,接到了VDD,上拉电阻手册说明为30~50K

3.输入下拉

下拉电阻的开关接通,电平信号输入与浮空输入的类似,只不过经过了下拉电阻

4.模拟输入

多用于DA转换,将外部的电压转为内部能识别的数字信号

4种输出模式:

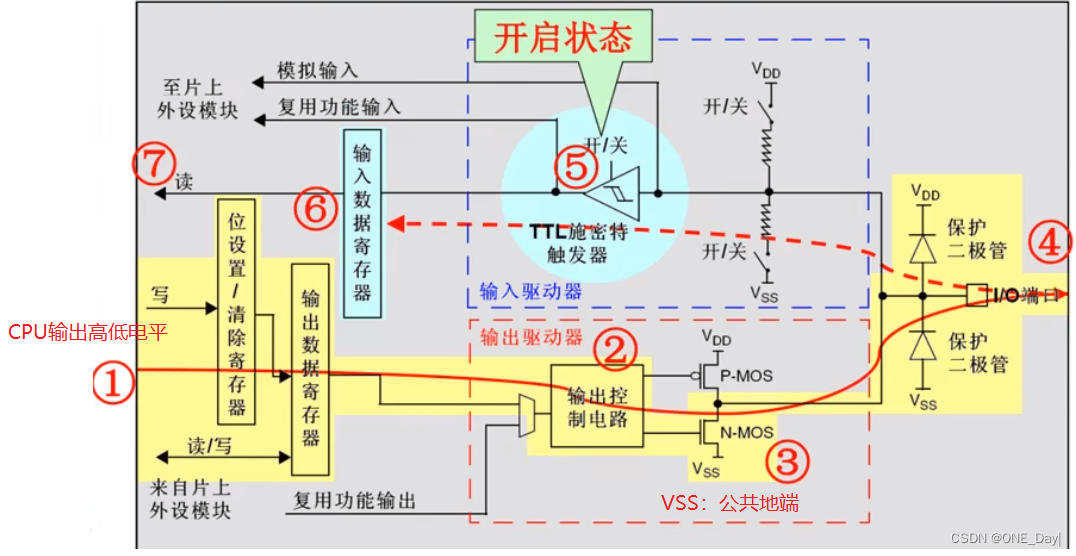

1.开漏输出

CPU往位设置寄存器写入1,则高电平1来到输出控制电路这里,N-MOS管不会导通,此时IO端口的电平状态由外部的上拉或者下拉决定,可能为高电平也可能为低电平;同时IO端口的状态可以被读取,通过虚线的电路被CPU读取,此时读取的并不一定是CPU输出的高电平1,而是外部的状态

CPU如果往位设置寄存器写入0,则低电平0来到输出控制寄存器,N-MOS管导通,IO端口与VSS导通,而VSS是电路公共地端电压,一般接GND,所以IO端口就输出低电平0;同时CPU读取时端口状态就是自己输出的低电平0

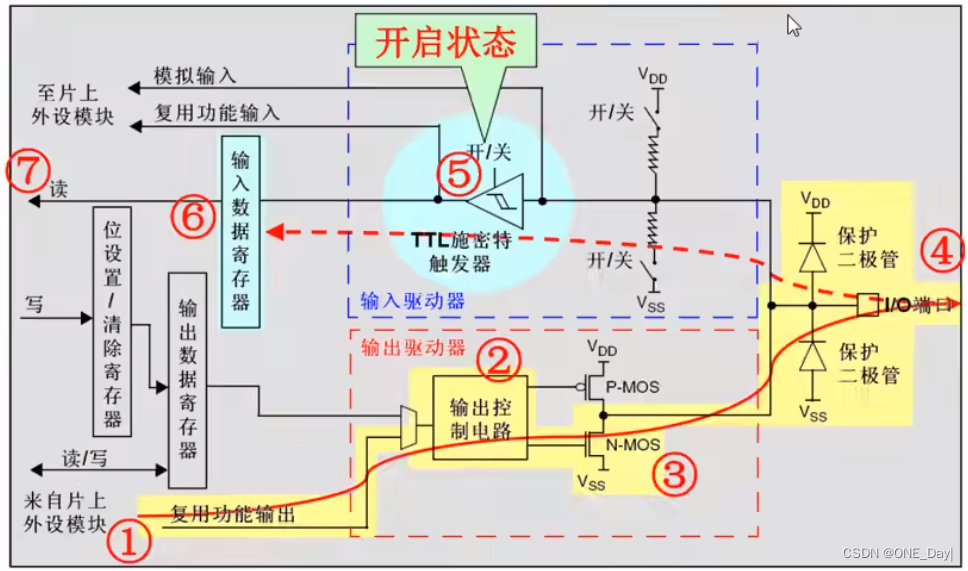

2.开漏复用输出

与开漏输出类似,不过电平不是由CPU输出,而是由来自片上的外设模块输出

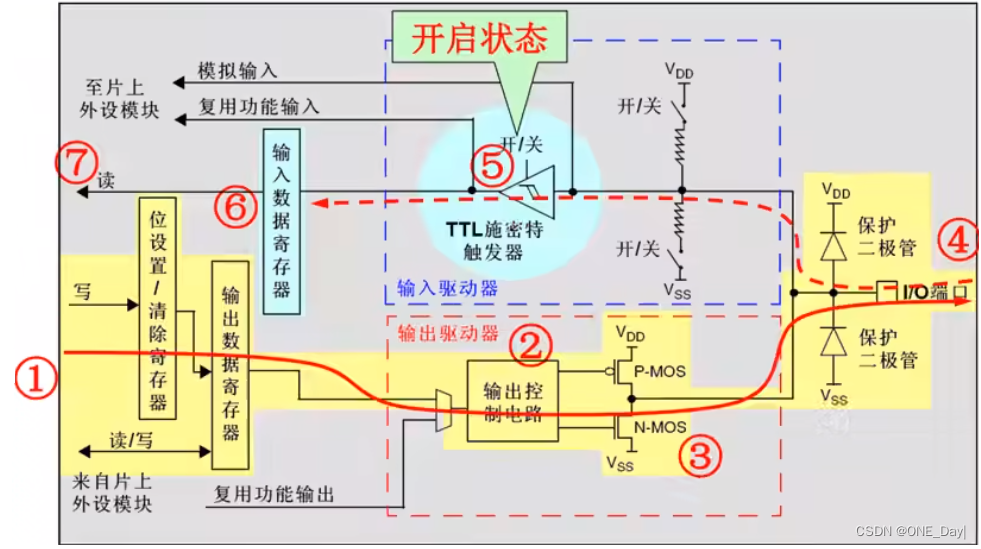

3.推挽输出

CPU往位设置寄存器写入1,则来到输出控制电路这里,P-MOS管导通,N-MOS管截止,IO端口接到VDD,IO口输出高电平1

CPU往位设置寄存器写入0,则来到输出控制电路这里,N-MOS管导通,P-MOS管截止,IO端口接到VSS,而VSS是接GND的,IO口输出低电平0

4.推挽复用输出

与推挽输出逻辑一样,只不过不是由CPU输出电平,而片上外设模块输出电平

注意:

推挽输出:

可以输出强高低电平,连接数字器件

开漏输出:

只可以输出强低电平,高电平得靠外部电阻拉高。输出端相当于三极管的集电极,要得到高电平状态需要上拉电阻才行,适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内)

开漏输出一般作为信号输出,比如给模块一个使能信号;

推挽输出一般作为驱动信号,比如驱动一个灯,但只有20mA的电流,如果要驱动蜂鸣器这样的,需要加三极管

F1系列没有专门设置输入上拉或者下拉的寄存器,属于伪上/下拉

在F4系列里面就有专门的寄存器设置。

3种最大翻转速度:

2MHZ

10MHZ

50MHZ

GPIO相关配置寄存器

每组GPIO端口的寄存器包括:

两个32位配置寄存器(GPIOx_CRL , GPIOx_CRH);

两个32位数据寄存器(GPIOx_IDR和GPIOx_ODR);

一个32位置位/复位寄存器(GPIOx_ BSRR);

一个16位复位寄存器(GPIOx_ BRR);

一个32位锁定寄存器(GPIOx_LCKR)。

每个I/O端口位可以自由编程,然而I/O端口寄存器必须按32位字被访问(不允许半字或字节访问)。

端口配置低寄存器(GPIOx_CRL)、端口配置高寄存器(GPIOx_CRH)

配置寄存器比较好理解,STM32的引脚分为了7组,GPIOA、GPIOB、GPIOC……GPIOG,每一组都有端口配置低寄存器(GPIOx_CRL),x就代表A、B、C……G,后面的端口配置高寄存器也是这样;

那每一组有16个IO口,每个IO的配置需要4位来完成,因为STM32一次性只能处理32位的数据,所以GPIOx_CRL就只有32位(0 ~ 31);32 / 4 = 8,只能配置8个IO口,那这个组还剩8个IO口怎么办,就只能再用一个端口配置高寄存器(GPIOx_CRH)来进行配置

总结:CRL/CRH每四个位控制一个IO口,CRL控制标号0-7的口,CRH控制标号8-15的口

端口输入数据寄存器(GPIOx_IDR) (x=A…E)

IDR寄存器低16位,每个位控制该组IO的一个IO口,对应的是IO口的输入电平

端口输出数据寄存器(GPIOx_ODR) (x=A…E)

ODR寄存器跟IDR相反,是控制IO口输出。低16位每个位控制一个IO口的输出电平高或低

端口位设置/清除寄存器(GPIOx_BSRR) (x=A…E)

BSRR寄存器低16位,对应位设置为1,那么IO口输出为高电平,对应位设置为0,对应IO口不产生任何影响。高16位作用相反。

该寄存器可以用来设置IO口为高电平1,也可用来清除IO口为低电平0

端口位清除寄存器(GPIOx_BRR) (x=A…E)

清除IO口的电平,该寄存器只能清除,不能设置,看名字就知道

端口复用功能

STM32的大部分端口都具有复用功能。

所谓复用,就是一些端口不仅仅可以做为通用IO口,还可以复用为一些外设引脚,比如PA9 、PA10可以复用为STM32的串口1引脚。

作用:最大限度的利用端口资源

端口重映射功能

就是可以把某些功能引脚映射到其他引脚。

比如串口1默认引脚是PA9,PA10,可以通过配置重映射映射到PB6,PB7

作用:方便布线

例如:USART1_TX默认复用到PA9,USART1_RX默认复用到PA10,可以通过重映射,将USART1_TX映射到PB6,将USART1_RX映射到PB7

STM32 所有IO口都可以作为中断输入

标准库GPIO相关函数功能简介

-

相关阅读:

电动平衡车UL2272测试哪些项目

C. Labs

学生个人单页面网页作业 学生网页设计成品 静态HTML网页单页制作 dreamweaver网页设计与制作代码 web前端期末大作业

基于springboot+vue水务报修处理系统

GO语言基础

企业AI虚拟ip形象定制的应用场景

目标检测YOLO系列算法的进化史

Redis5 分布式系统之主从模式

【1day】用友U8Cloud未授权访问漏洞学习

Vite+Vue3创建项目案例

- 原文地址:https://blog.csdn.net/weixin_46251230/article/details/126602606