-

【牛客网】Verilog快速入门-基础语法(1)

⭐作者: 桐桐花❀

⭐个人主页:桐桐花的博客_CSDN博客-python,Verilog,数字IC领域博主

⭐系列专栏:Verilog刷题_桐桐花的博客-CSDN博客

⭐推荐刷题神器:

牛客网 - Verilog刷题模块Verilog快速入门-基础语法篇(1)

1、四选一多路选择器

描述:制作一个四选一的多路选择器,要求输出定义上为线网类型。

状态转换:

d0 11

d1 10

d2 01

d3 00信号示意图:

波形示意图:

输入描述:

输入信号 d1,d2,d3,d4 sel

类型 wire输出描述:

输出信号 mux_out

类型 wire答案

- `timescale 1ns/1ns

- module mux4_1(

- input [1:0] d1,d2,d3,d0,

- input [1:0] sel,

- output [1:0]mux_out

- );

- //*************code***********//

- reg [1:0] mux_out_1;

- always@(*)

- begin

- case(sel)

- 2'b00: begin mux_out_1 = d3; end

- 2'b01: begin mux_out_1 = d2; end

- 2'b10: begin mux_out_1 = d1; end

- 2'b11: begin mux_out_1 = d0; end

- endcase

- end

- assign mux_out = mux_out_1;//(输出定义上为线网类型)

- //*************code***********//

- endmodule

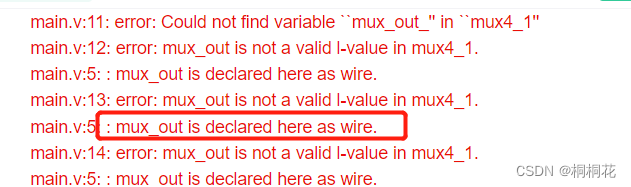

问题:下面代码可以运行成功吗?如果没有运行成功,有什么问题?

无法编译成功。

模块端口默认声明变量为wire类型,但是在always块里,变量是reg类型的。

把模块端口里面的mux_out改成 reg类型,可以编译成功吗?

依然没有编译成功。

因为 ,“描述:制作一个四选一的多路选择器,要求输出定义上为线网类型。”

所以要将MUX的输出结果通过assign连接出去。即

assign mux_out = mux_out_1;//(输出定义上为线网类型)2、异步复位的串联T触发器

题目描述:

用verilog实现两个串联的异步复位的T触发器的逻辑,结构如图:

信号示意图:

波形示意图:

输入描述:

输入信号 data, clk, rst

类型 wire

在testbench中,clk为周期5ns的时钟,rst为低电平复位输出描述:

输出信号 q

类型 reg答案

- module Tff_2 (

- input wire data, clk, rst,

- output reg q

- );

- reg q1;

- always@(posedge clk or negedge rst)

- begin

- if(!rst)

- begin

- q1<=0;

- q<=0;

- end

- else

- begin

- q1 <= data ^ q1;

- q <= q1 ^ q;

- end

- end

- endmodule

testbench

- `timescale 1ns/1ns

- module testbench( );

- reg clk=0;

- reg rst=0;

- reg data=0;

- wire q;

- Tff_2 Tff_2(

- .data(data),

- .clk(clk),

- .rst(rst),

- .q(q)

- );

- always #5 clk = ~clk; // Create clock with period=10

- initial begin

- #10 rst = 1'b1;

- #60 data = 1'b1;

- #110 data = 1'b0;

- #160 data = 1'b1;

- end

- endmodule

相关知识点:

1、T触发器

T触发器特性方程

T触发器的特性表

T触发器 状态转换图

T触发器 状态转换图

2、异步复位

异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

练习题目:

-

相关阅读:

一文了解如何源码编译Rainbond基础组件

C语言进阶——字符串函数&&内存函数

Spring监听器

UI线程和bitmap

【嵌入式Linux】编译应用和ko内核模块Makefile使用记录

升级 Kubernetes 上的 TiDB 集群

kubernetes布署方式介绍

打造自己的3D模型AI 自动纹理工具

创意无限,图文生成如虎添翼:星火大模型的威力

Redis 一个key-value存储系统

- 原文地址:https://blog.csdn.net/weixin_41788560/article/details/126470476