-

HNU 电子电路 模型机综合设计

作为电子电路总成绩的重要组成部分之一,一个完整的CPU设计起来难度可以想象,特别是对于第一次接触Verilog的来说。不过好在可以借鉴往届学长学姐们的cpu,再将vhdl转成Verilog。这东西要独立完成还是相当困难的,毕竟可能所有元件都没问题,但组装起来就是会报错,你也不知道错哪。我那个就是自认为感觉没啥问题就一直有错误,询问了胡老师才知道是一个很蠢的问题。不过这cpu难归难,我还是认为越早做完越好,因为根据同一届的经验来看越接近验收的那两天熬夜熬的越猛,恰逢期末复习时间,如果不早点弄好这个CPU的话还是很容易忙的焦头烂额的。另外,学好这东西对于下学期的计算机系统这门课也有些许帮助哦。

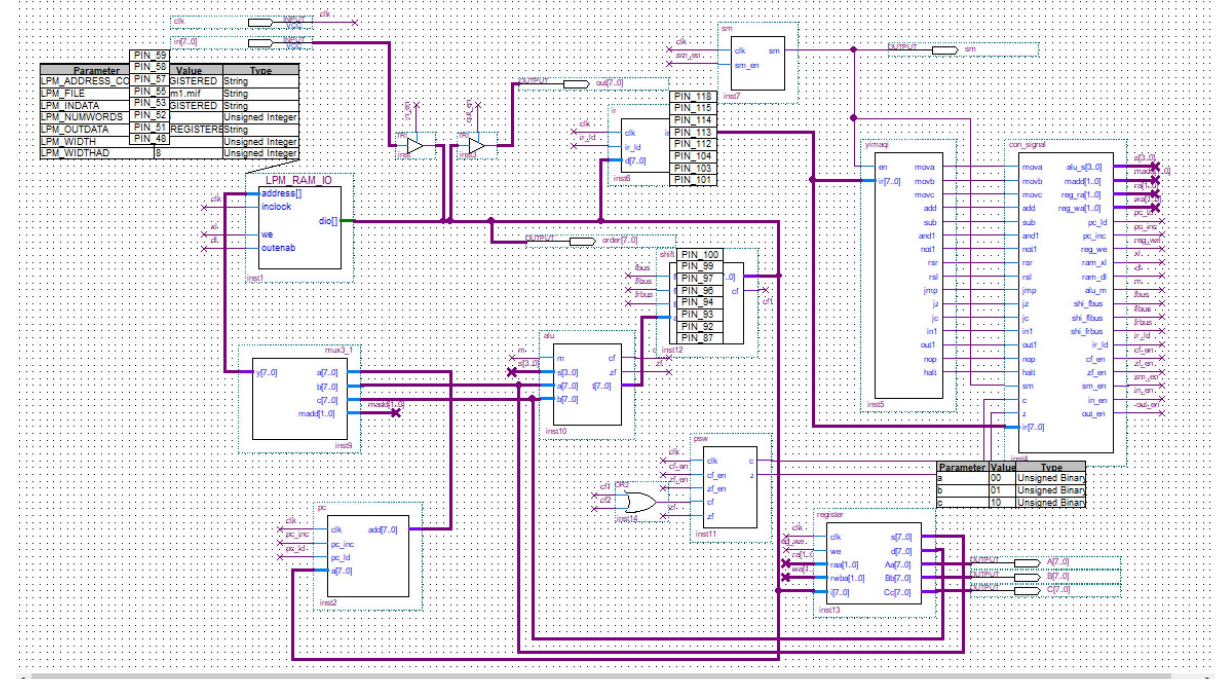

完整的设计框架

总体来说就那么几个元件,要连接顺序都固定了,主要就看你摆放的位置和布局是否美观就行了。在这里我为了追求美观删除了一些东西,但CPU还是能跑的。最后得的成绩不记得了多少了,好像是95还是多少,我感觉我cpu完成得也没问题,性能也比较好,测试程序也是自己写的,也知道那些100分的咋得的。

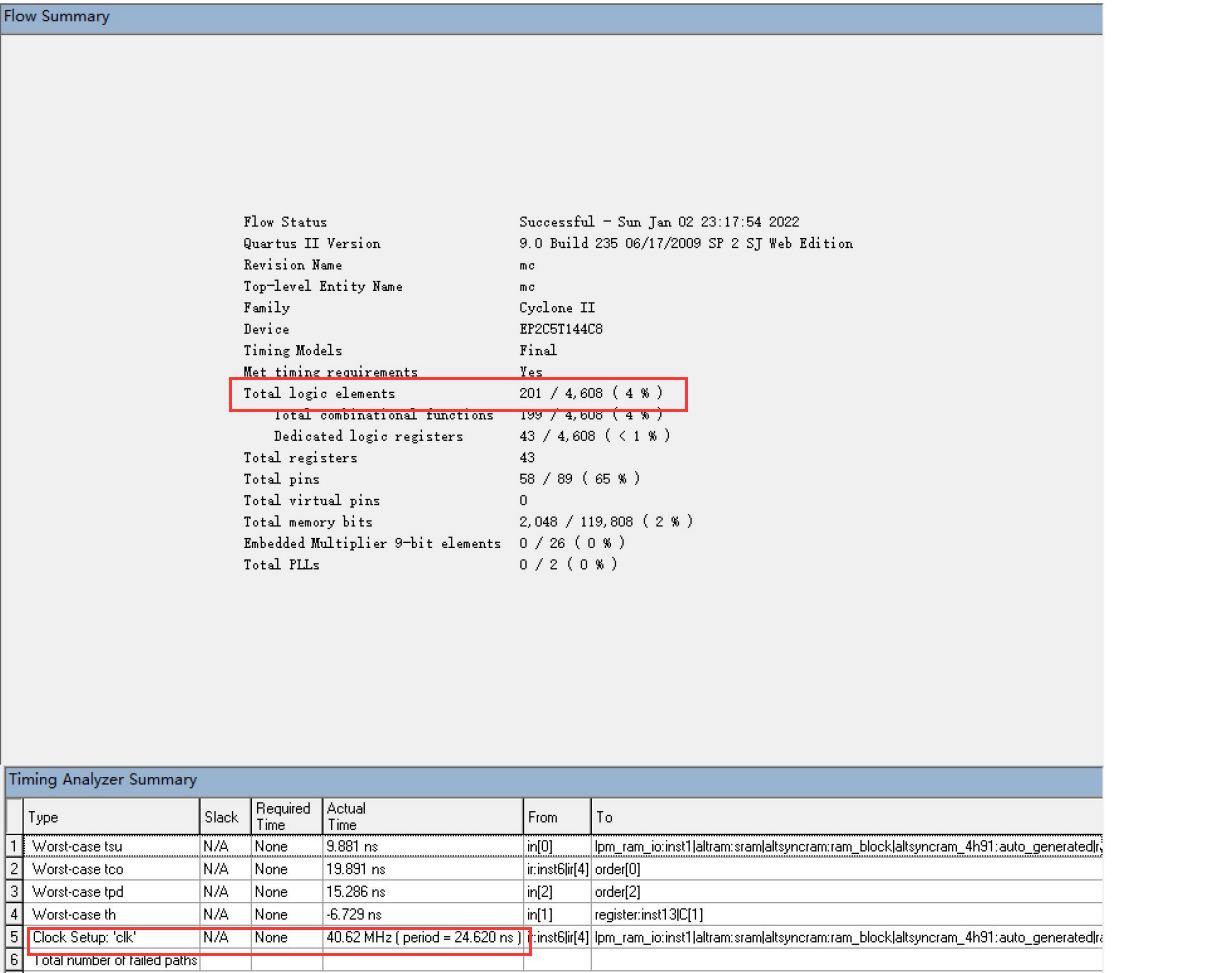

CPU的性能主要看这两个方面,理论上数值越小性能越好,最后验收的成绩也会越高

注意:每年的元件的要求不一定都完全一样,一定别完全地抄,注意甄别

完整工程放在这

-

相关阅读:

RabbitMQ

回文数 洛谷 - P1015

ts json的中boolean布尔值或者int数字都是字符串,转成对象对应类型

【论文解读】CP-SLAM: Collaborative Neural Point-based SLAM System_神经点云协同SLAM系统(上)

深度学习-nlp系列(5)文本实体识别(LSTM)pytorch

《016.SpringBoot+vue校园社团管理系统》【有文档】

智能机器人与AI助手:未来办公场景的变革者

【教学类-09-02】20221022《动物棋 S形迷宫》(数字续写和骰子游戏)(大班主题《动物花花衣》)

合同矩阵充要条件

12. 一文快速学懂常用工具——docker 命令

- 原文地址:https://blog.csdn.net/qq_51684393/article/details/126414638