-

Vivado 综合后工程

Vivado支持多种类型(3种:RTL/post-synthesis/io-plan)工程,当创建Post-Synthesis (门级)工程时,需要注意:

大概是5种类型的输入文件:1,struct verilog 2,edf 3,BD file 4,XCI 5,DCP

对于IP文件需要使用XCI文件作为输入,而不是dcp文件(虽然dcp文件包含设计约束,但却没有elf/coe这些ram的初始化文件),同时这个XCI并不是一个单纯的xci文件,需要设置OOC方式完成生成后,

vivado会自动搜索当前路径下的相关文件(保持文件夹的独立性,一个ip一个文件夹,不要混入其它文件),添加时只要把xci添加进来即可:比如:

生成dcp的方式有很多:dcp本身是一个zip文件

1,打开网表,手动生成:

手动生成时一般有两种方式,一种是直接把需要的模块设置为顶层,综合后打开,直接输入:

write_checkpoint -file 1.dcp 【可以单独引用】

另一种是直接打开完整的工程,使用-cell参数,但是这个方式生成的dcp在使用时总是提示缺少文件:

2,综合完成后一般默认会在综合路径下自动生成一个dcp:【可以单独引用(该文件的size相对其它方式较大推荐优先使用)】

3,当将ip设置为ooc是也会默认在ip对应的文件夹自动生成一个dcp,但是单独引用这个

dcp是有问题的。(如前所述-如何引入ip到post_synthesis prj)

-------------------------------------------------------------------------------------------

-mode out_of_context是否需要设置?

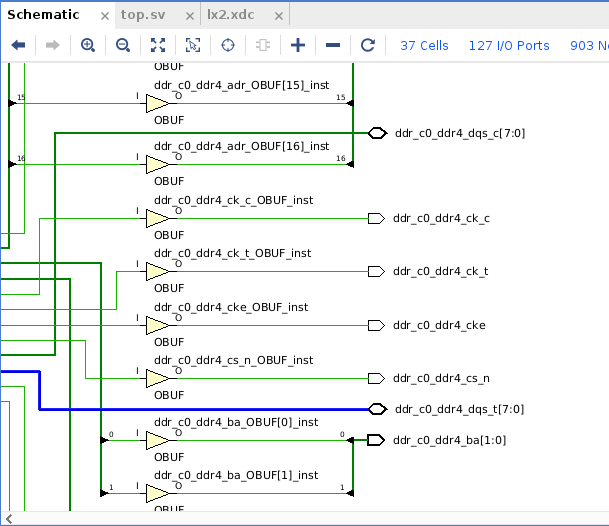

一般综合时会在port上自动插入ibuf/obuf:以xilinx ddr ip做黑核为例

xilinx ddr ip 实际在内部会用rtl例化各个port的buf,这样一来将设计网表和ip网表合到一起时看上去应该会有冲突(比如一个端口有两个ibuf):但实际并不是如此,vivado会自动处理这种情况:

也就是说重复的ibuf/obuf不会对工程实现造成影响,vivado是允许这种情况的。因此在生成dcp时是否选择out_of_context有时候没有区别。

对于ooc模式的网表也会自动插入io buffers.

目前看上去只适用于单端的ibuf/obuf,差分的一般要手动例化,如ibufds.

-----------------------------------------------------------------------------

参考:

Vivado Design Suite User Guide: System-Level Design Entry (UG895)

Vivado Design Suite Tcl Command Reference Guide (UG835)

Vivado Design Suite User Guide: Synthesis ( UG901 ) -

相关阅读:

linux写代码环境和工具

“信任机制”才是数字化时代发展中的精髓所在

ipconfig显示的内容分析(一)网卡

亚马逊化学物质和重金属限制物质清单

若依3.6.0使用Mybatis-plus分页失效以及完美替换Pagehelper【已解决】

(十一)人工智能应用--深度学习原理与实战--实现泰坦尼克号生存者预测案例Titanic Survival

GO语言开山篇(一):学习方向

【单链表】无头单项不循环(2)

hyper-v安装 windows10虚拟机后,登录一直是锁屏界面,无法开启增强会话

【数据结构与算法】手撕链表OJ题

- 原文地址:https://blog.csdn.net/u011329967/article/details/126359101