-

计算机基础(一):面向CPU编程

前言

之前我已表达过学习计算机基础的必要性,这方面的知识之前一直都很欠缺,最近我也开始了学习计算机基础、底层相关的内容。因此,开始在这里也进行一些相关的总结。

计算机起源

根源–图灵机模型

我们都知道,现代计算机的原理源自于图灵机模型,图灵机是一个抽象的模型,是英国数学家艾伦・麦席森・图灵提出的一个计算模型:

通用图灵机向人们展示这样一个过程:程序和其输入可以先保存到存储带上,图灵机就按程序一步一步运行直到给出结果,结果也保存在存储带上。更重要的是,隐约可以看到现代计算机主要构成,尤其是冯・诺依曼理论的主要构成。(百度百科)

我们可以简单理解为:通过一台机器运行有限次的步骤,得到最终的计算结果。可以实现代替人类计算的这样一台机器。

如果将图灵机看做是程序设计中的接口,那么我们可以将冯诺依曼体系理解为对其进行的实现。

体系–冯诺依曼体系结构

数学家冯·诺依曼提出了计算机制造的三个基本原则,即采用二进制逻辑、程序存储执行以及计算机由五个部分组成(运算器、控制器、存储器、输入设备、输出设备),这套理论被称为冯·诺依曼体系结构。(百度百科)

我们可以看到冯诺依曼体系结构中,结合物理、数学的相关知识,确定了计算机硬件的基本构成:运算器、控制器、存储器、输入输出设备。

后面的历史我们也可以从百度百科中得知第一台通用计算机ENIAC就这样诞生了。

计算机硬件组成

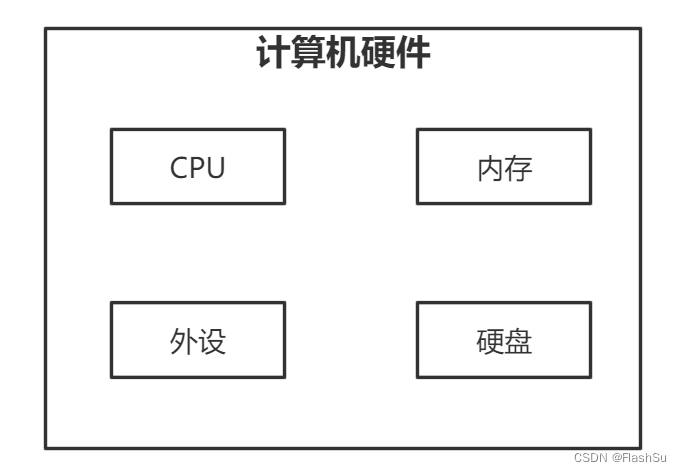

上面提到计算机由五个部分组成:运算器、控制器、存储器、输入设备、输出设备,后面我们知道运算器、控制器其实是放在CPU中的,存储器也被分为硬盘和速度更快的内存,输入输出设备可以统称为外设。因此简化之后的计算机硬件基本构成:

在这其中,CPU是核心,我们只要控制了CPU,就可以操作其他组件,因此,我们也可以将CPU看做是整个计算机的控制器,通过它来控制计算机的一切!CPU的组成

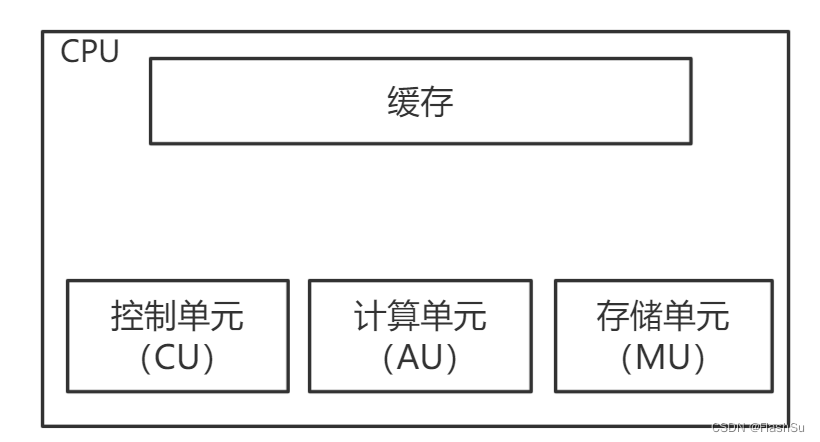

放大来看,CPU自己也是一个小世界,类似地,其中主要包含的组件有:- ALU(Arithmetic logic unit 算术和逻辑运算的计算单元)

- MU(向ALU 提供操作数并存储 ALU 运算结果的处理器寄存器(存储单元))

- CU(Control unit 通过指导 ALU、寄存器和其他组件的协调操作从内存获取、解码和执行指令)

控制单元、计算单元、存储单元处理的速度可以看做是相近的,但和内存的速度却查了数量级的区别,因此中间还需要加入一层缓存来匹配整体的速度。

CPU的执行流程

大多数 CPU 的基本操作,无论它们采用何种物理形式,都是执行一系列存储的指令,称为程序。要执行的指令保存在某种计算机内存中。几乎所有 CPU 在其操作中都遵循获取、解码和执行步骤,这些步骤统称为指令周期。

在执行一条指令后,整个过程会重复,由于程序计数器中的值增加,下一个指令周期通常会获取顺序中的下一条指令。如果执行了跳转指令,程序计数器将被修改为包含跳转到的指令的地址,程序继续正常执行。在更复杂的 CPU 中,可以同时获取、解码和执行多条指令。

一些指令操纵程序计数器而不是直接产生结果数据;此类指令通常称为“跳转”指令,并促进程序行为,如循环、条件程序执行(通过使用条件跳转)和函数的存在。在某些处理器中,其他一些指令会改变“标志”寄存器。这些标志可用于影响程序的行为方式,因为它们通常指示各种操作的结果。例如,在这样的处理器中,“比较”指令评估两个值并设置或清除标志寄存器中的位,以指示哪个更大或它们是否相等;然后这些标志之一可以被稍后的跳转指令用来确定程序流程。(维基百科)

从上面这段描述中,我们知道了何谓程序、以及CPU执行指令的步骤:Fetch(取指令)、Decode(解码/译码)、Execute(执行),这些步骤统称为指令周期

Fetch

取指涉及从程序存储器中检索一条指令(由一个数字或数字序列表示)。指令在程序存储器中的位置(地址)由程序计数器(PC;在 Intel x86 微处理器中称为 instruction pointer “指令指针”)确定,该计数器存储一个数字,用于标识要获取的下一条指令的地址。获取指令后,PC 会增加指令的长度,以便它包含序列中下一条指令的地址。通常,必须从相对较慢的内存中检索要获取的指令,导致CPU 在等待指令返回时停止。这个问题在现代处理器中主要通过缓存和流水线架构解决。

Decode

CPU从内存中加载的指令决定了CPU将要做什么。在Decode阶段,通过称为指令解码器的二进制解码器电路执行,将指令转换为控制CPU其他部分的信号。

指令的解释方式由CPU的 ISA(instruction set architecture 指令集架构) 定义。通常,指令中的一组bits(可以叫作一个字段),被称作操作码(opcode)指示要执行的操作具体要干什么,其余字段通常提供操作所需的补充信息,例如操作数。这些操作数可以指定为常量值(成为立即数 immediate value),或者是值的具体位置,该位置可以是寄存器或者是内存地址,具体由寻址模式确定。

Execute

在获取和解码步骤之后,执行执行步骤。根据 CPU 架构,这可能由单个操作或一系列操作组成。在每个动作期间,控制信号以电气方式启用或禁用 CPU 的各个部分,以便它们可以执行全部或部分所需操作。然后完成该动作,通常是响应时钟脉冲。经常将结果写入内部 CPU 寄存器,以便后续指令快速访问。在其他情况下,结果可能会写入速度较慢但成本较低且容量较大的主存储器。

指令与程序

以上三段CPU执行操作的描述,翻译自维基百科,可能第一次看的话,会让人云里雾里,各种名词不清楚,这里我们重点关注下 ISA 这个一个概念就好。

ISA(Instruction set architecture),也被叫作计算机架构,是计算机的抽象模型。执行由 ISA 描述的指令的设备,例如中央处理单元 (CPU),称为实现。

一般来说,ISA 定义了支持的指令、数据类型、寄存器、管理主存的硬件支持、基本特性(例如内存一致性、寻址模式、虚拟内存)以及一系列实现的输入/输出模型。

看这个定义可能还是云里雾里,其实对下层来讲,ISA就是定义的对CPU进行操作的规则;对上层来讲,ISA就是所有编程语言的根。

我们都知道我们所写的Java、Python、PHP、JS都会映射成二进制的形式,交给CPU去执行,但是最终的二进制具体是怎样的规则呢,其实就是由 ISA 来定义的。

ISA 可以按多种不同的方式进行分类。一个常见的分类是按架构复杂性来分,其中常见的两大类型:复杂指令集计算机 (CISC: complex instruction set computer) 有许多专门的指令,其中一些在实际程序中可能很少使用。精简指令集计算机 (RISC:reduced instruction set computer) 通过仅有效地执行程序中经常使用的指令来简化处理器。CISC的典型代表为Intel,RISC的典型代表为AMD。

上图是一个表示CPU执行的的一个整体示意图:ISA指令传入控制单元,从存储单元中加载数据,进行第3步的运算,然后写入存储器或缓存,进而同步到主存。

-

相关阅读:

C# .Net AOP 演进历史POP OOP 代码细节篇

基于SSM框架的电影院售票网站

区块链的量子威胁:解密数学漏洞

第104天: 权限提升-Linux 系统&环境变量&定时任务&权限配置不当&MDUT 自动化

【大厂招聘试题】__嵌入式开发工程师_2023届“联想”_1

1024节日

Go语言学习教程(十四)

【场景化解决方案】销帮帮酷应用,帮助企业销售团队实现精细化管理

Junit 集成测试

关于商业智能BI,今天只谈这五点

- 原文地址:https://blog.csdn.net/lyg673770712/article/details/126338138