-

Linux中make命令和makefile文件的编写,最后附完整代码。

前言:

首先我们必须要知道:make是一个命令 ,makefile是一个文件。

目录

一:makefile三要素

目标:最终要生成的目标文件

依赖项:目标文件由哪些文件生成

依赖关系:如何使依赖项生成目标文件

在编写makefile文件时,目标是必须要存在的,对于依赖项和依赖关系,可以没有。

二:makefile中的变量与常用函数

1:普通变量的定义和使用

那么如果还要使用普通变量 j,也需要特定的格式 $(j) 才可以 。

2:自动变量

这些变量是makefile文件中特有的,他们每一个都代表着特别的含义。

$^:代表着目标的所有依赖项目

$@:代表目标

$<:代表目标的第一个依赖项

$?:代表目标的第一个变化的依赖项(这个用到比较少)

注意:这些自动变量只能使用在依赖关系中。

3:常用函数

wildcard:查找指定目录下的指定类型文件

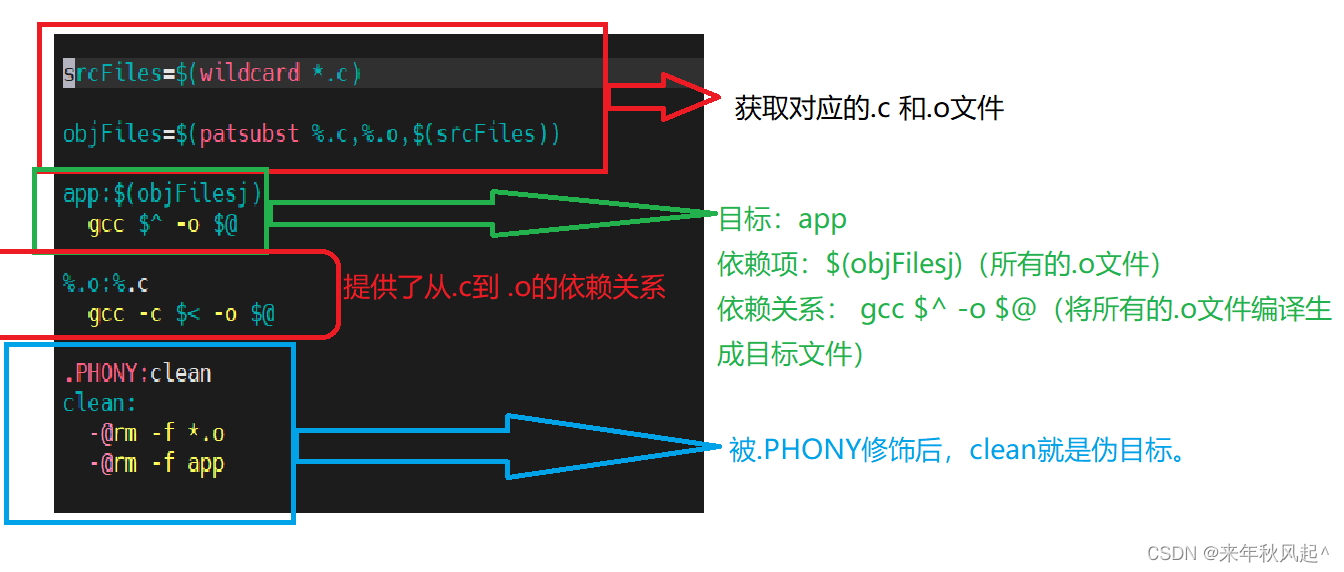

srcFiles=$(wildcard *.c)//获取当前工作目录下所有的 .c 文件,交给变量srcFiles(当然这里也可以查找其他类型的文件)

patsubst:匹配替换

objFiles=$(patsubst %.c,%.o,$(srcFiles))//将$(srcFiles)中所有的.c文件替换成.o文件交给变量objFiles。(这里注意使用变量时必须遵守的格式:$(变量名))

4:目标与伪目标

其实对与伪目标而言,它只是比目标多一个 .PHONY:修饰,这里的app就是目标,clean就是伪目标

二者的区别在于:

伪目标:总是可以被执行。

目标:当它的依赖项没有发生改变时,他是不能被二次执行的。

三:makefile的总体简介

-:代表当前命令错误时,继续执行下一条命令

@:代表不要打印当前命令行

四:makefile的编写

- 1 srcFiles=$(wildcard *.c)

- 2

- 3 objFiles=$(patsubst %.c,%.o,$(srcFiles))

- 4

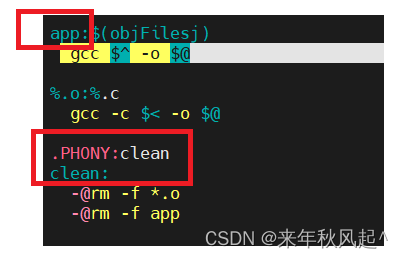

- 5 app:$(objFilesj)

- 6 gcc $^ -o $@

- 7

- 8 %.o:%.c

- 9 gcc -c $< -o $@

- 10

- 11 .PHONY:clean

- 12 clean:

- 13 -@rm -f *.o

- 14 -@rm -f app

-

相关阅读:

Darty自养号测评下单支付方式和注册账号手法有哪些要求?

MySQL监控innodb的阻塞

zemax坐标断点实现光束偏移

异或(xor)的讲解和使用方法

nginx反向代理

java版直播商城平台规划及常见的营销模式有哪些?

PikaScript实践记录(2)之移植PikaScript(1)

过一遍Python的Numpy库(最后因为各种原因只过到一半)

决策树深度探索: 从基础构建到机器学习应用

在鲲鹏服务器搭建k8s高可用集群分享

- 原文地址:https://blog.csdn.net/qq_51004011/article/details/126299632