-

跨时钟域问题(一)(建立时间保持时间和亚稳态)

🏡 博客首页:安静到无声

⛳️ 欢迎关注: ❤️ 点赞 🎒 收藏 ✏️ 留言

🚧 系列专栏:跨时钟域

🎈 如有错误不吝赐教

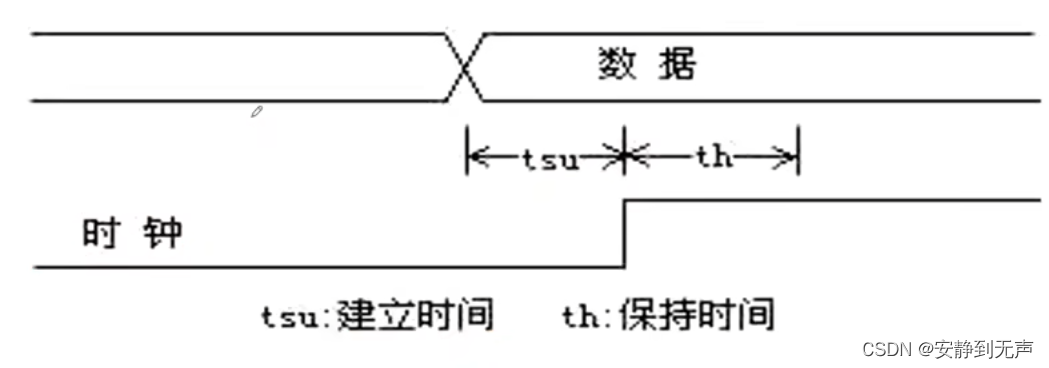

1. 建立时间和保存时间

建立时间:建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。

保持时间:保持时间是指触发器的时钟信号上升沿到来以后,数据保持稳定不变的时间。建立时间和保持时间是由器件(实质触发器决定的),当然,建立时间和保持时间是越短越好。

例子:

关于建立时间和保持时间的考虑:(笔试题目)

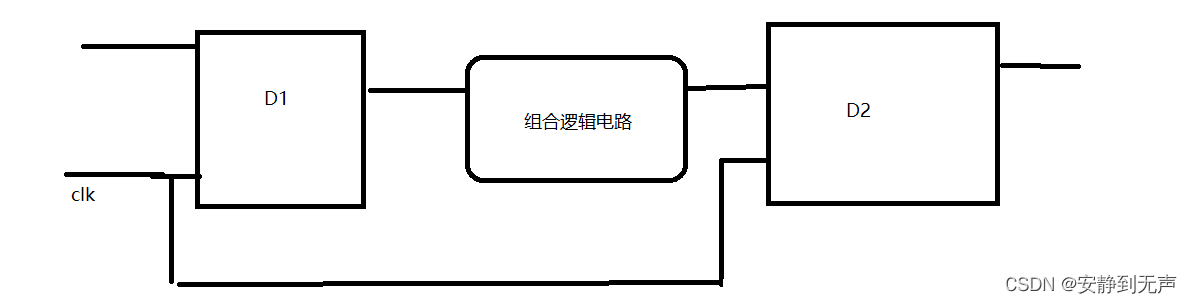

题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。请问:触发器D2的建立时间T3和保持时间T4应满足什么条件,才能够使数据可以正确的输出?分析

Tffpd:,触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来不后多长的时间内发生变化并且稳定,也可以理解为融发器的输出延时。

Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。

Tsetup:建立时间

Thold:保持时间

Tclk:时钟周期

建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。

保持时间容限:保持时间容限也要求大于等于0。图表达

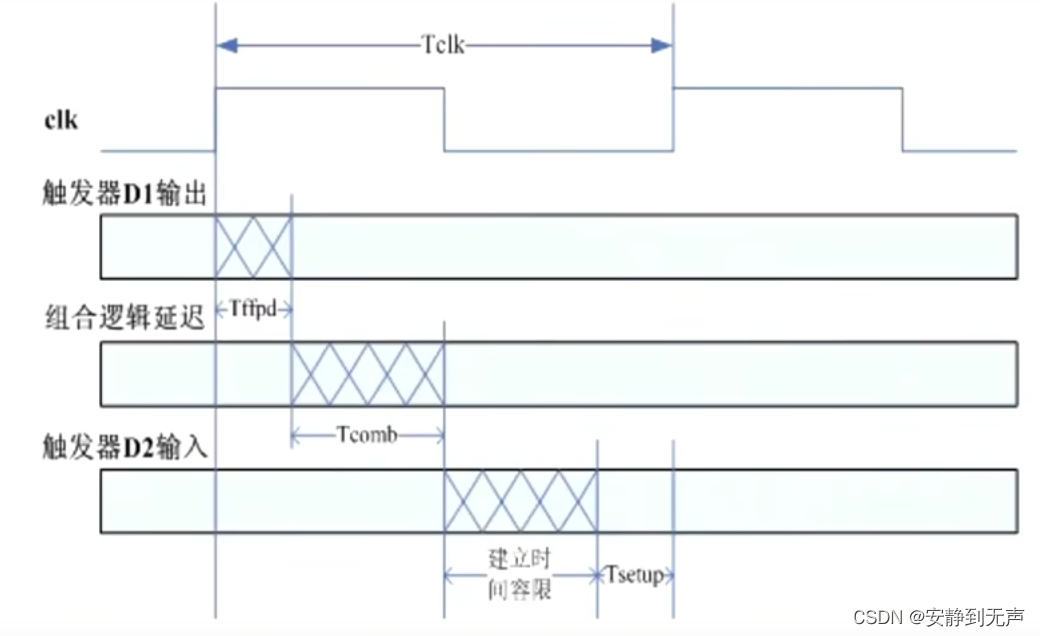

1.1 建立时间分析

由上图可知,建立时间容限=Tclk-Tffpd(max)-Tcomb(max)-Tsetup,根据建立时间容限≥0,也就是Tclk-Tffpd(max)-Tcomb(max)-Tsetup2≥0,可以得到触发器D2的Tsetup≤Tclk-Tffpd(max)-Tcomb(max),由于题目没有考虑Tffpd,所以我们认为Tffpd=0,于是得到Tsetup≤T-T2max。组合逻辑电路最大延迟为T2max,最小为T2min。

要求:对于一个高速的设计,T减小,主要是要将组合逻辑的时间减小。

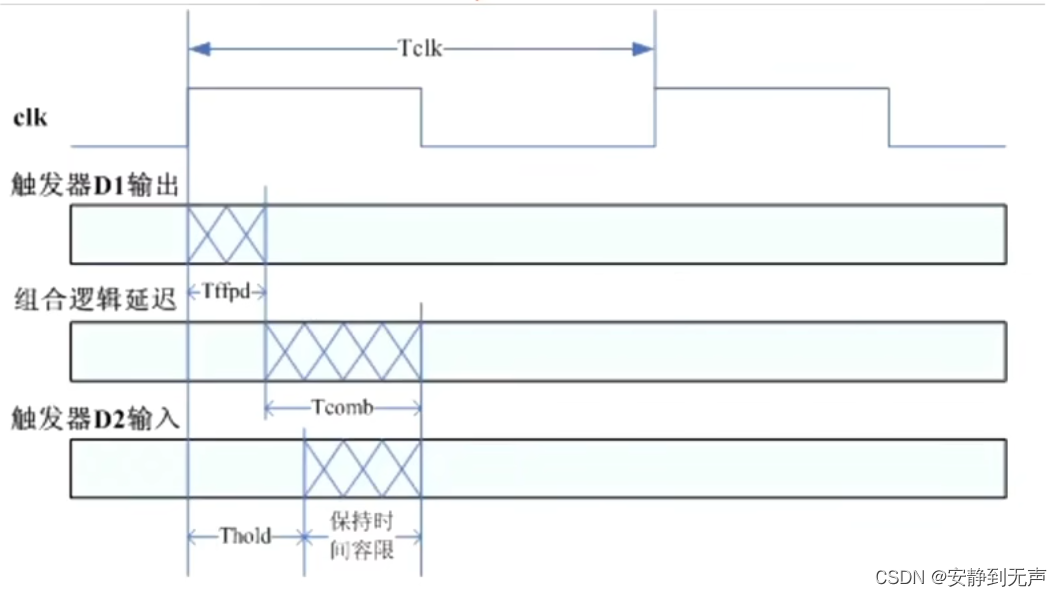

1.2 保持时间分析

保持时间,有上图可知保持时间容限+Thold=Tffpd(min)+Tcomb(min)。所以保持时间容限=Tffpd(min)+Tcomb(min)-Thold,根据保持时间的容限时≥0,也就是Tffpd(min)+Tcomb(min)-Thold≥0,可以得到触发器D2的Thold≤Tffpd(min)+Tcomb(min),由于题目没有考虑Tffpd,所以可以认为Tffpd=0,于是可以得到Thold≤T2min。关于保持时间的理解就是在触发器D2的输入信号还在保持时间的时候,如果触发器D1的输出已经通过组合逻辑电路到达D2的输入端的话,将会破坏D2本应该保持的数据。

由此我们可以得到一个组合逻辑延迟的区间[Thold:T-Tsetup]

1.3 结论

建立时间:触发器在时钟沿到来之前,其数据输入端必须保持不变的时间,决定了触发器之间组合逻辑的最大延迟。

保持时间:触发器在时钟沿到来之后,其数据输入端必须保持不变的时间,决定了触发器之间组合逻辑的最小延迟。2. 亚稳态

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

2.1 简介

触发器的建立时间和保持时间在时钟上升沿左右定义了一个时间窗口,如果触发器数据输入端口上的数据在这个时间窗口内发生变化(或者数据更新),那么就会产生时序违规。存在这个时序违规是因为违反了建立时间要求和保持时间要求,此时触发器内部的一个节点(一个内部节点或者要输出到外部节点)可能会在一个电压范围内浮动,无法稳定在逻辑0或者逻辑1状态。换句话说,如果数据在上述窗口中被采集,触发器中的晶体管不能可靠地设置为逻辑0或者逻辑1对应的电平上。所以此时的晶体管并未处于饱和区对应的高或者低电平,而是在稳定到一个确定电平之前,徘徊在一个中间电平状态(这个中间电平或许是一个正确值,又或许不是)。

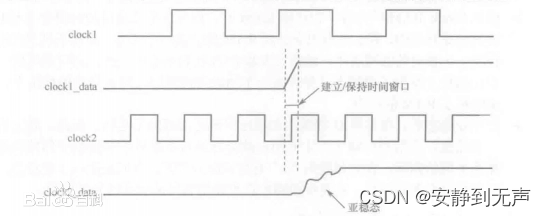

图3 异步时钟域亚稳态波形图程

如图3所示,此时第一个时钟触发器的输出数据,在第二个时钟的建立/保持时间窗口发生改变,就导致了第2个时钟触发器的输出有一段时间处于一种无法确定的电压范围(亚稳态)。

2.2 亚稳态产生原因

在同步系统中,如果触发器的建立时间 / 保持时间不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。这段时间称为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是究竟是0还是1,是随机的,与输入没有必然的关系。

2.3 处理亚稳态的经典办法——双触发

当需要在两个时钟域传输信号时,有一个重要的问题是:是否需要采样从一个时钟域传输到另一个时钟域的这个信号的每一个值?通过思考这个问题可以发现,在跨时钟边界存在跨时钟域传输数据允许丢失部分采样值和跨时钟域传输数据不允许丢失任何信号采样值两种情况,而且确认设计到底属于哪种情况则变得非常重要。

对于第一种情况来说,没有必要去采样每一个值,但是需要注意的是被采样的值必需要确保精确度;而在第二种情况中,一个跨时钟域信号必需要被正确识别,或者说在其允许发生改变之前必须被识别。这两种情况中,跨时钟域信号都需要被同步到其接收时钟域之中。

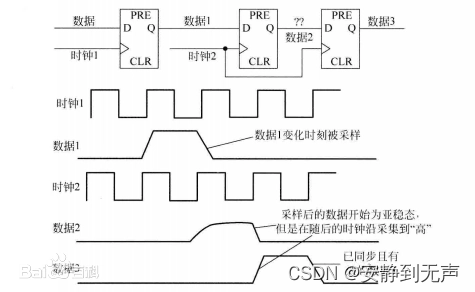

最常见的同步器就是使用两级寄存器,即使用寄存器打两拍的方式进行同步。所谓的同步器就是采样一个异步信号,采样输出能够同步到本地或采样时钟的模块。这种最简单也是使用最普遍的两级寄存的同步器如图1所示。

图4 两级寄存的同步器当然,仍然有可能级联的第二个寄存器输出还会表现为非稳定状态,但是这种双寄存同步器已经可以解决大部分这类亚稳态问题。在设计这种同步器的时候应当注意遵循以下原则:

级联的寄存器必须使用同一个采样时钟

发送端时钟域寄存器输出和接收端异步时钟域级联寄存器输入之间不能有任何其他组合逻辑。

同步器中级联的寄存器中除了最后一个寄存器外所有的寄存器只能有一个扇出,即其只能驱动下一级寄存器的输入。

注意:下一节将对该问题做出详细分析! -

相关阅读:

用HTML和CSS打造跨年烟花秀视觉盛宴

电压频率的变换原理

python之xml文件的读取介绍

【人工智能】神经网络八股

PHP M题 - 技巧

C/C++语言100题练习计划 92——矩阵加法(线性代数)

电动汽车充放电V2G模型

dubbo:从零理解及搭建dubbo微服务框架(一)【附带源码】

win10-docker-mysql镜像安装运行基础

java计算机毕业设计科研成果管理系统设计与实现MyBatis+系统+LW文档+源码+调试部署

- 原文地址:https://blog.csdn.net/lihuanyu520/article/details/126255326