-

中断系统结构及中断控制详解

中断系统结构及中断控制详解

MCS—51提供5个中断请求源,2个中断优先级,可实现两级中断服务程序嵌套。当CPU执行关中断指令后(或复位),将屏蔽所有中断请求,只有CPU执行开中断指令后才有可能接受中断请求,每个中断源可由软件编程为允许中断和禁止中断,每个中断源可程控为高优先级中断或低优先级中断。可见MCS-51具有较强的中断处理能力。

一、中断系统内部结构

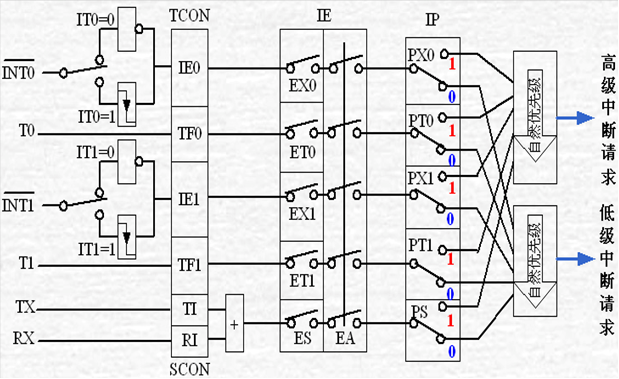

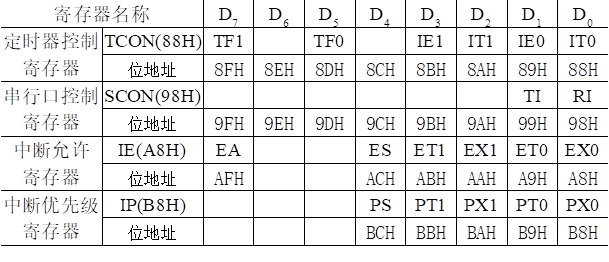

MCS-51的中断系统结构框图如下图所示,与中断有关的特殊功能寄存器有4个,分别为中断源寄存器(即专用寄存器TCON和SCON的相关位)、IE和IP。

MCS-51单片机有5个中断源,可提供两个中断优先级,即可实现二级中断嵌套。

二、MCS-51中断源及中断入口

MCS-51的中断源可分为三类:外部中断、定时中断和串行口中断。

1.外部中断类

由外部原因引起的:

INT0——外部中断0请求信号,由P3.2输入,IT0 (TCON.0) 决定中断请求信号是低电平有效还是下降沿有效。一旦输入有效,即向CPU申请中断,并使IE0=1。

INT1——外部中断1请求信号,由P3.3输入,由IT1 (TCON.2) 决定中断请求信号是低电平有效还是下降沿有效。一旦输入有效,即向CPU申请中断,并使IE1=1。

2.定时中断类

定时中断是为满足定时或计数溢出处理的需要而设置的,在单片机芯片内部发生,无需在芯片上设置引入端,但在计数方式时,中断源可以由单片机芯片外部引入。

TF0——定时器T0溢出中断请求。当定时器T0产生溢出时,其中断请求标志TF0=1,请求中断处理。

TF1——定时器T1溢出中断请求。当定时器T1产生溢出时,其中断请求标志TF1=1,请求中断处理。

3.串行口中断类

串行口中断为串行数据的传送需要而设置的。

RI或TI——串行中断请求。

各中断源对应的中断服务程序入口地址:

中断源 入口地址

外部中断0 0003H

定时器T0中断 000BH

外部中断1 0013H

定时器T1中断 001BH

串行口中断 0023H

三、MCS-51中断请求

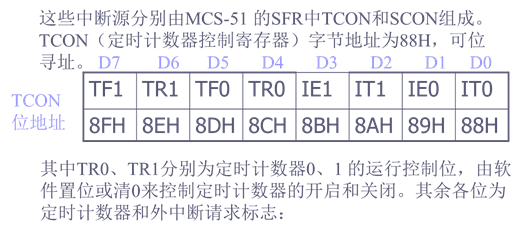

中断标志位:

TF1、TF0、IE1、IE0、RI 、TI登记各中断源请求信号:=1,有中断请求;= 0,无中断请求。

CPU响应中断后,该中断标志自动清零。TI,RI标志必须软件清零。

外部中断触发方式选择位:

- IT0、IT1=1:负边沿触发中断请求;= 0:低电平触发中断请求。

-

IE0:外中断0中断申请标志

若IT0=0,每个机器周期的S5P2采样INT0 ,若INT0=0则IE0=1;当 IT0=1时,第一个机器周期采样到INT0为高电平,第二个机器周期为低电平,则IE0=1。IE0=1表示外中断0正在向CPU申请中断,当CPU响应中断,转向中断服务程序时,由硬件清“0”IE0

-

TF0: T0溢出中断标志

T0被启动计数后,加1计数,溢出后,由硬件使TF0=1,请求中断,此标志保持到CPU响应中断后,由硬件自动清“0”。也可用软件查询该标志,并由软件清“0”。

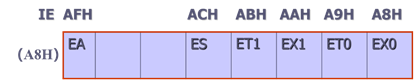

四、中断允许控制

中断允许控制位:EA、ES、ET1、EX1、ET0、EX0

=1开中断;= 0关中断。

例:允许CPU响应INT0的中断请求

SETB EX0

SETB EA

中断允许寄存器IE格式和各位含义如下:

- EA——CPU中断总允许位。EA=1,CPU开放中断;

- ES ——串行口中断允许位。 ES=1,允许串行口中断

- ET1—— T1中断允许位。 ET1=1,允许T1中断。

- EX1——外部中断1允许位。 EX1=1,允许外部中断1中断

- ET0—— T0中断允许位。 ET0=l,允许T0中断;

- EX0——外部中断0允许位。EX0=1,允许外部中断0中断

- MCS-5l系统复位后,IE中各中断允许位均被清“0” 。

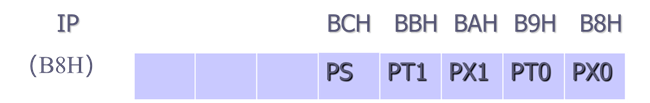

五、 中断优先级

中断优先级——设计人员给每个中断源事先安排中断响应的优先顺序。然后按轻重缓急的次序响应。

专用寄存器IP统一管理中断优先级。可实现两级中断嵌套。

- PS ——串行口中断优先级控制位。

- PT1——T1中断优先级控制位。

- PX1——外部中断1中断优先级控制位。

- PT0——T0中断优先级控制位。

- PX0——外部中断0中断优先级控制位。

以上对应位为1,高优先级;为0,低优先级。

当系统复位后,IP低5位全部清“0”,将所有中断源设置为低优先级中断。

同一优先级别按内部查询顺序排列优先级:

高 INT0、T0、INT1、T1、SIO 低。

自然优先级由硬件形成,排列次序如下:

- 中断源 自然优先级

- 外部中断0 最高级

- 定时器T0中断

- 外部中断1

- 定时器T1中断

- 串行口中断 最低级

-

相关阅读:

GitHub上标星120k的Java进阶面试教程等!(建议收藏)

IPFS系列 - 答疑

windows 中pycharm中venv无法激活

Android Java反射与Proxy动态代理详解与使用基础篇(一)

选择边缘计算网关的五大优势

C++——关键字|命名空间|输入&输出|缺省参数|函数重载|引用

《高考择校择专业:权衡与抉择的智慧》

假设检验计算

【读书笔记】【Effective C++】继承与面向对象设计

pagehelper分页查询

- 原文地址:https://blog.csdn.net/m0_52316372/article/details/126236880