-

HLS学习1:点灯

0、引言

本系列博客主要用于记录学习过程,如有错误欢迎指点。

芯片:xc7z020clg400-1;

开发板:小熊猫7020开发板;

开发环境:Vivado 18.3;

系统环境:Windows 11;

参考资料:小熊猫HLS文档、ug902、ug871、米联客HLS、黑金HLS等。1、HLS

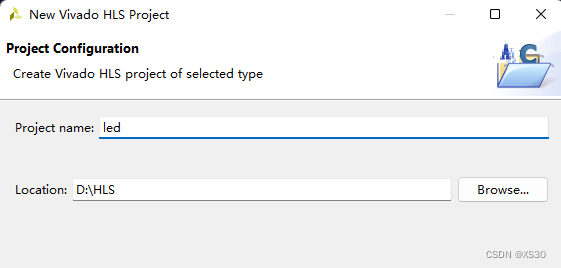

新建工程

名字随意取,路径要记住

添加文件

添加使用HLS语言编写的cpp文件,添加完成后,浏览该文件,提取Top Function文件(这里的文件名对应之后的IP名)

然后添加TestBench Files(用于测试和调用前者的CPP文件),你也可以不添加,一样可以综合打包完成选择芯片

代码

#include "stdio.h" #include "ap_int.h" #define CLK_FREQ 1 void hls_01_fpga_led_stream_ip(ap_int<4> &led) { #pragma HLS interface ap_none port=led #pragma HLS interface ap_ctrl_none port=return static int led_number=0; static long cnt_reg=0; if(cnt_reg<CLK_FREQ)cnt_reg++; else { cnt_reg=0; if(led_number<3)led_number++; else led_number=0; } if(led_number==0) { led=0x1; } else if(led_number==1) { led=0x2; } else if(led_number==2) { led=0x4; } else if(led_number==3) { led=0x8; } }- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

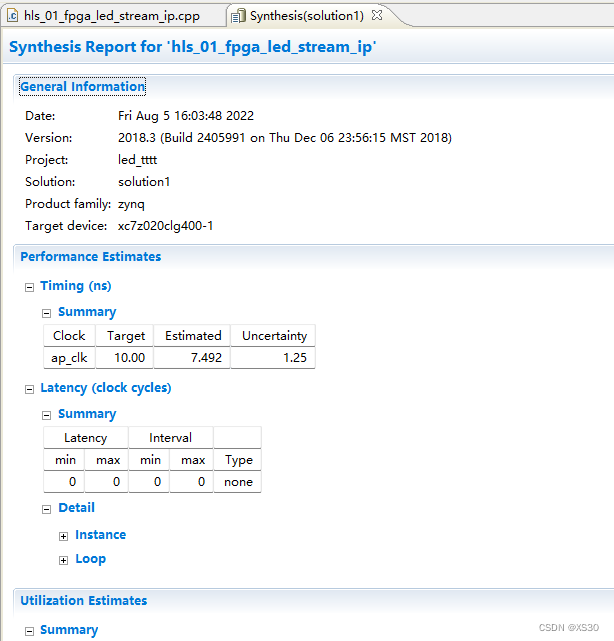

进行综合(Synthesis)

选择顶部菜单栏的综合按钮(C Synthesis)默认第一个

综合完成后,如果没有问题,会自动跳转到综合报告界面,可以看到端口和资源用量。

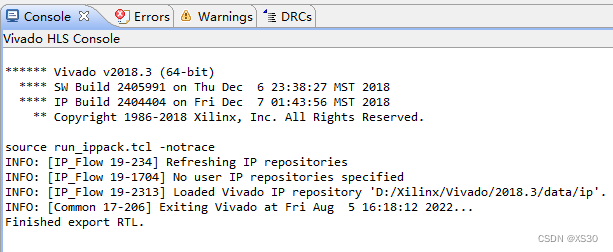

打包IP(导出RTL)

点击菜单栏的这个图标,进行导出

弹出的对话框,默认即可

完成导出

进行测试/仿真(Simulation)

此步骤非必须,但对后期代码实际部署有明显优点,可以通过该手段对代码进行测试。

如果说IP代码是一个功能块/函数;那个tb文件则是调用IP的主函数。#include "stdio.h" #include "ap_int.h" extern void hls_01_fpga_led_stream_ip(ap_int<4> &led); int main(void) { int i=0; unsigned int tmp_print_data=0; ap_int<4> led=7; for(i=0;i<1000;i++) { hls_01_fpga_led_stream_ip(led); tmp_print_data=led&0xf; printf("i=%d,led=%d\r\n",i,tmp_print_data); } return 0; }- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

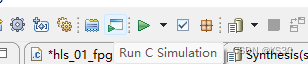

然后点击该图标,进行仿真

通过查看log文件或console窗口的输出信息,判定程序是否正确运行。

2、Vivado

创建工程

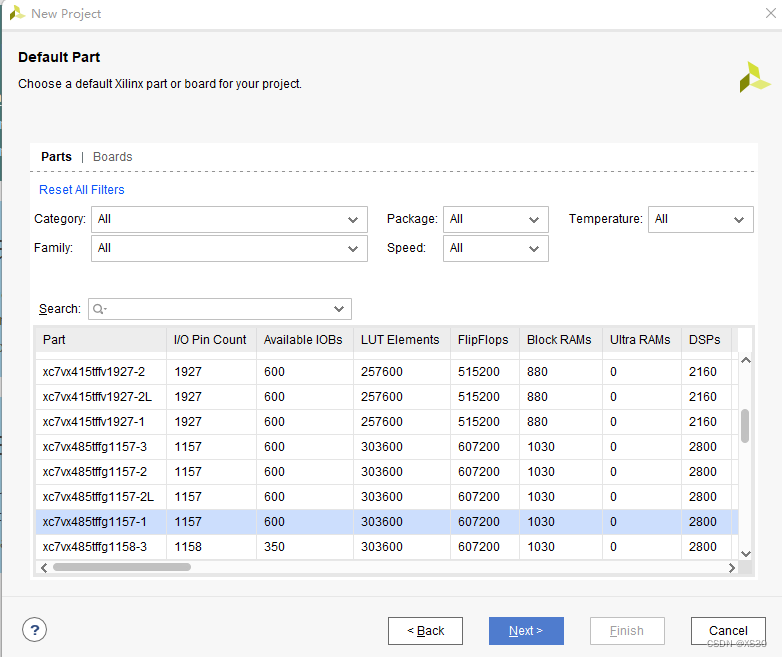

一路Next,直到这里选择自己的芯片xc7z020clg400-1(这个错了,会导致IP无法正确加载,这个选择可以在软件中进行二次修改)

导入IP

点击左侧的Setting(这里可以修改芯片型号)

IP——>Repository——>添加——>选择HLS工程路径

点击OK,添加完成(这里需要注意,必须是IP名称前的图标必须是黄色的才行,如果是灰色,将无法进行后续工作,请检测是否芯片不匹配。

点击OK关闭界面。

创建 Block Design

点击右侧的加号,将刚刚导入的IP进行添加

添加完成

进行连线及配置

由于我们要实现的是简单的流水灯功能,所需要的时钟信号和复位信号都由外置引脚进行提供,LED也需要参考原理图进行了配置,所以在块设计中,我们需要将所有的端口进行配置。

选中对应管脚,使用Ctrl+T快捷键,快速生成端口。

连线完成后,我们需要要块设计转换为HDL Wrapper

创建完成

分配管脚

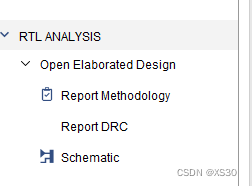

点击左侧选单中的Open Elaborated Design,弹出的对话框默认OK。

弹出该页面

按照下图进行引脚配置,然后Ctrl+S保存,并命名

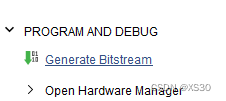

生成Bit文件

这里的14指的电脑CPU核心数

可以选Open Hardware Manager打开该界面,然后选择Open target,选择Auto

烧录测试

选择Program device烧录。

-

相关阅读:

目标检测-Yolo框架

java计算机毕业设计校园共享单车系统源程序+mysql+系统+lw文档+远程调试

蓝桥杯构造法|两道例题(C++)

前端学习-BFC,作用和原理,typeof,parseIntString()函数,Boolean()函数,深浅克隆

入门力扣自学笔记186 C++ (题目编号:1822)

干货:服务器网卡组技术原理与实践

国庆来临,外贸人出货必须注意的几个点(附节日营销技巧)

MXNet实现ResNet(残差网络)深度神经网络模型

java中的注解

挂耳式蓝牙耳机性价比推荐,盘点五款性能高的耳机分享

- 原文地址:https://blog.csdn.net/u014798590/article/details/126178484