-

【硬件架构的艺术】学习笔记(3)处理多个时钟

目录

写在前面

这个博客系列是对最近阅读的书籍《硬件架构的艺术》的部分内容的读书笔记,大部分的内容是摘抄书上的内容,小部分是自己的笔记,对书上部分知识点的理解以及拓展(红色标注)。

3 处理多个时钟

通常在 RTL 的设计中,选用一个时钟作为驱动是比较好设计的,但是有时不可避免的需要的多个时钟去驱动,相对于单时钟,多时钟在亚稳态、建立时间和保持时间更容易出问题,这时候如何去处理多个时钟就显得尤为重要。

3.1 多时钟域

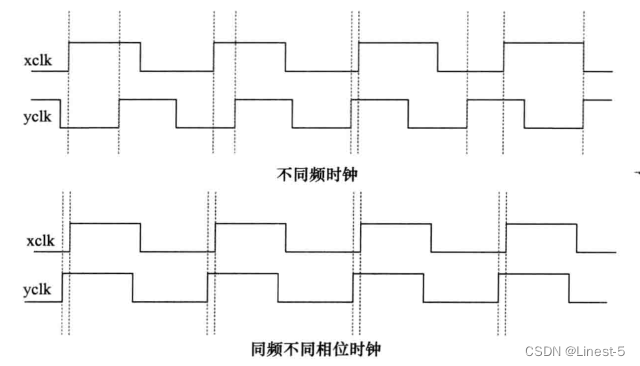

多时钟的可以大致分成两类:

- 时钟的频率不同

- 时钟的频率相同但相位不同

3.2 多时钟域的设计难点

多时钟域的设计主要难点:

- 建立时间和保持时间

- 亚稳态

3.2.1 建立时间和保持时间

建立时间:在时钟到来前,输人数据需要保持稳定的时间。

保持时间:在时钟到达后,输人数据仍需保持稳定的时间。

关于更多建立时间和保持时间的解释在之间的文章有详细的阐述。

3.2.2 亚稳态

在之前的文章也讲述的比较清楚。

3.3 多时钟设计的处理技巧

在含多个时钟的设计时,遵循一些准则可以给设计过程中带来便利:

- 时钟命名规则

- 分模块设计

这个在之前的文章也有介绍。直达链接如下:

3.4 跨时钟域

多个时钟都起源于同一时钟,并且它们的相位和频率关系是已知的,那么这些时钟可以看成是跨同步时钟域的时钟。按照相位和频率的关系,可以将这些时钟分成以下类型:

- 同频零相位差时钟

- 同频恒定相位差时钟

- 非同频可变相位差时钟(整数倍时钟、有理数倍时钟)

由于同频零相位差时钟严格意义上不属于跨时钟,所以这里不展开叙述。

3.4.1 同频恒定相位差时钟

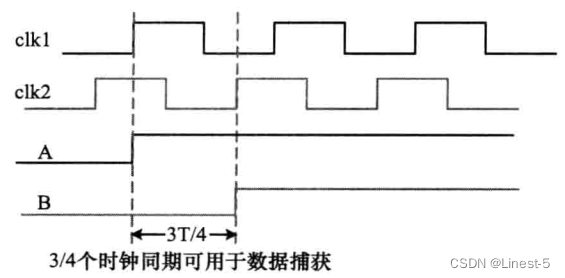

时钟有相同的周期,相位差恒定。比如对某个时钟及其反相时钟的使用,或者是某个时钟相对于其上级时钟发生了相位移动。在下图中 “clk1” 相对于 “clk2” 相位前移了 3T/4 个单位时间。

每当数据从 “clk1” 传输到 “clk2” 时,由于更小的建立时间/保持时间裕量,对组合逻辑的延时约束都会变得更紧。如果组合逻辑的延时能保证满足采样沿处建立时间和保持时间的要求,数据就可以正确地传输,并且不会有亚稳态产生,在这种情况下是不需要同步器的。

3.4.2 非同频可变相位差时钟

这类时钟具有不同的频率,而且相位差也是可变的。可以将这类时钟分为两类:各时钟周期之间是整数倍的关系、各时钟周期是非整数倍(有理数倍)的关系。

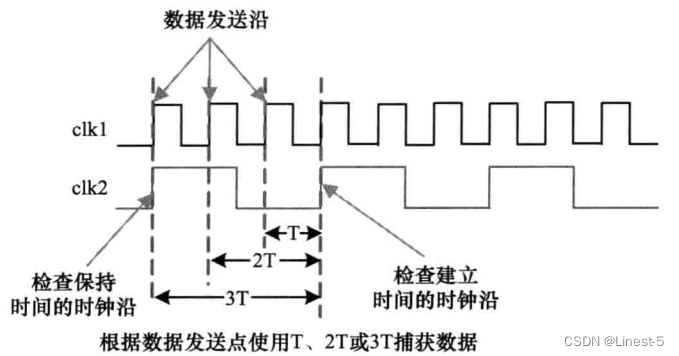

整数倍时钟

在这种情况下,一个时钟的频率是另一个时钟的整数倍,并且它们有效边沿的相位差是可变的。这两个时钟的有效边沿之间可能的最小相位差始终等于其中较快的那个时钟的时间周期。

既然在这里数据由较快时钟发出,并由较慢时钟捕获,那么为了避免数据丢失,源数据应该保持至少一个目的时钟周期的稳定状态。可以使用一些控制电路来满足这一要求,例如,使用一个简单的有限状态机(FSM)。如下图,如果使源数据每三个源时钟改变-一次,就不会出现丢数据的问题了。

从快时钟域到慢时钟域,数据可能会丢失,这时解决方法其实主要有两个,一个是上述所说的方法,另一个是使用 FIFO 做数据缓冲,这个在后面会详细说明。

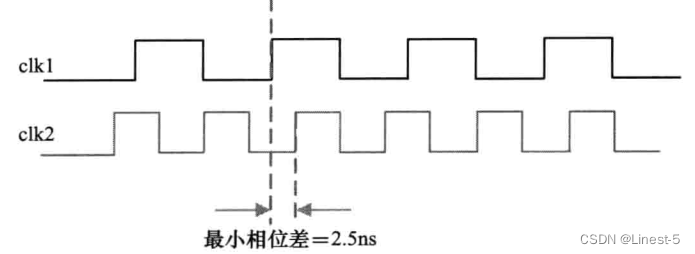

非整数倍时钟

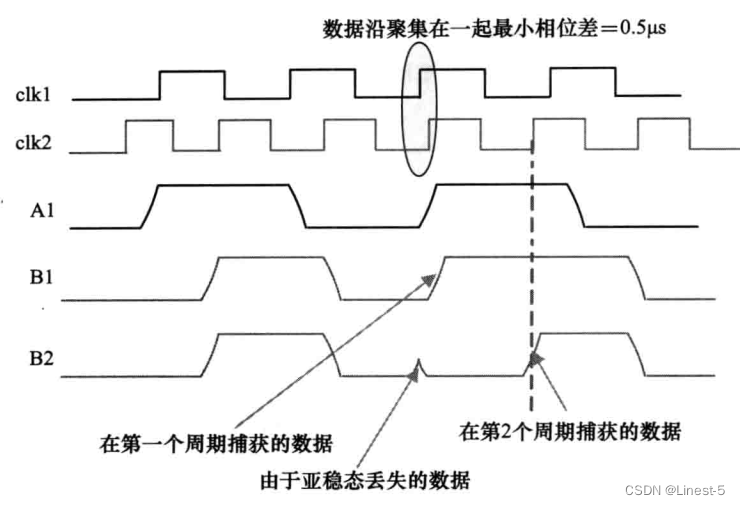

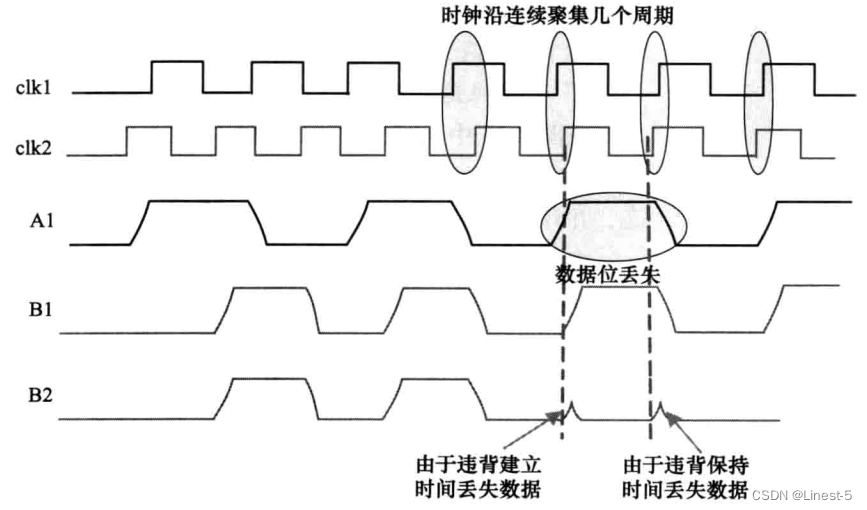

这种情况下两时钟之间的最小相位差可能产生亚稳态。下面介绍三种不同的情况。

情况一

在源时钟有效沿和目的时钟有效沿之间有足够大的相位差,所以不会有亚稳态产生。

情况二

源时钟和目的时钟有效沿非常接近,导致产生亚稳态问题。然而这里时钟频率倍数关系需要满足以下条件,即一旦有时钟边沿接近出现,下一个时钟周期就会留出足够大的时间冗余,使数据的捕获不会出现违背建立时间或保持时间的要求。

情况三

两个时钟的时钟沿在许多连续的周期中都非常接近。这与异步时钟的行为很相似,但因为这两个时钟的源头是相同的,所以它们之间的相位差是可以计算出来的。

对于非整数倍的多时钟情况,可能出现的情况比较多,因此需要对于实际的项目中设计的实例进行分析,对症下药。

3.5 握手信号方法

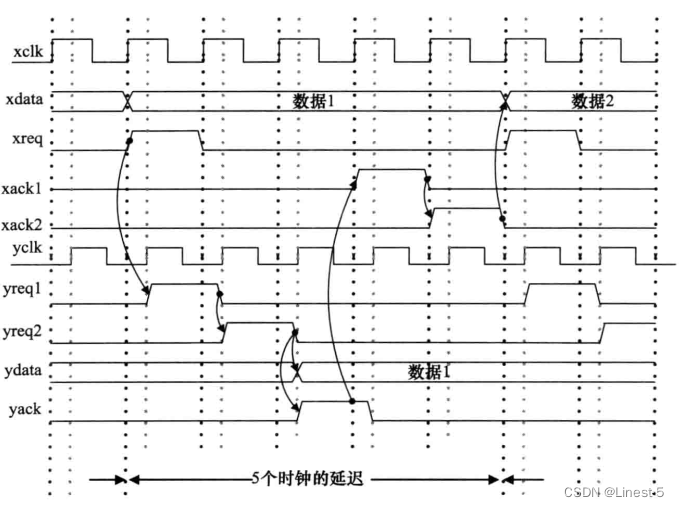

使用握手信号 “xack” 和 “yreq”, “系统X” 将数据发送给 “系统Y"。

下面是使用握手信号传输数据的例子。

- 发送器 “系统X” 将数据放到数据总线上并发出 “xreq” (请求)信号,表示有效数据已经发到接收器 “系统Y” 的数据总线上。

- 把 “xreq” 信号同步到接收器的时钟域 “yclk" 上。

- 接收器在识别 “xreq” 同步的信号 “yreq2” 后,锁存数据总线上的信号。

- 接收器发出确认信号 “yack", 表示其已经接受了数据。

- 接收器发出的 “yack" 信号同步到发送时钟 “xclk” 上。

- 发送器在识别同步的 “xack2” 信号后,将下一个数据放到数据总线上。

其实就是我们常用的 “valid” 和 “ready” 信号。“valid” 信号表示发送方的数据有效,“ready” 表示接收方将数据已正常接收,可以接收下一数据。

握手信号时序如下图所示。

在图中可以看出,安全地将一个数据从发送器传输到接收器需要 5 个时钟周期。

使用握手信号传递数据应该在发送时钟域内稳定至少两个时钟上升沿。请求信号 “xreq” 的宽度应该超过两个上升沿时钟,否则从高速时钟域向低速时钟域传递可能无法捕捉到该信号。并且使用握手信号一大缺点就是跨时钟域传输单个数据的延迟比使用 FIFO 传输相同的数据要大得多,这个在需要高速传输数据的项目要求中还是很致命的。

3.6 使用同步 FIFO 传输数据

3.7 使用异步 FIFO 传输数据

这部分在之前的文章中有详细说明,链接。

-

相关阅读:

最强大脑记忆曲线(7)——“复习页面”逻辑实现

雷电模拟器上使用第一个frida(一)之安装

vue + Lodop打印控件的使用

工业自动化控制通信协议Profinet系列-1、了解Profinet协议及收集资料

Java 将Excel转为UOS

227 微信登录验证 java_移动端第三方登录(微信)java验证并获取用户信息

用c++补全二维数组问题代码

c++ linux 配置

在 Elasticsearch 中实现自动完成功能 1:Prefix queries

我好像洞察到二叉树路径和的秘密

- 原文地址:https://blog.csdn.net/m0_61298445/article/details/126167474